Fターム[5F101BD31]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | アレイ (242)

Fターム[5F101BD31]の下位に属するFターム

稠密アレイ構造 (233)

Fターム[5F101BD31]に分類される特許

1 - 9 / 9

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

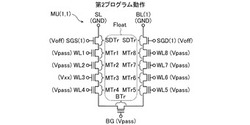

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

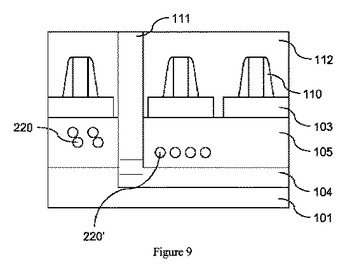

埋め込み型トラッピング層によるトランジスタの閾値電圧の調整方法

方法は、電子サブアセンブリの形成について、調整可能な閾値電圧を有する少なくとも1つの第1のトランジスタ(110)を担持する半導体層(103)が絶縁層(102、105)に接合される組み立てステップと、半導体層および第1のトラッピングゾーンが容量結合されるように、第1のトラッピングゾーン(220)が所定の第1の深さで絶縁層に形成される形成ステップであって、前記第1のトラッピングゾーンが、前記第1のトランジスタのチャネルの少なくとも下に延び、かつ前記第1のトラッピングゾーンの外側のトラップの密度より高い密度のトラップを有する形成ステップとを含み、前記第1のトランジスタからの有用な情報はこのトランジスタ内の電荷移動である。具体的な実施形態において、第2のトランジスタのチャネルの少なくとも下に延びる第2のトラッピングゾーンが、第1のトラッピングゾーンに使用されるのとは異なるエネルギーおよび/または用量および/または原子の第2の注入によって形成される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置の消去回路

【課題】 メモリセルブロック単位での消去処理において、消去処理にかかる制御を複雑化することなく、各メモリセルブロックを電気的に絶縁するための境界領域を設けずにチップ面積をおさえることができる不揮発性半導体記憶装置を提供する。

【解決手段】 第1導電型の半導体基板に形成された第2導電型のウェル領域内に、メモリセルを行及び列方向にマトリクス状に配列し、同一行にあるメモリセルの制御ゲートを夫々共通のワード線に接続してなるメモリセルアレイが形成され、メモリセルアレイを複数のワード線を含んで構成される複数のメモリセルブロックに分割し、メモリセルブロック単位で消去処理を行なう不揮発性半導体記憶装置であって、ウェル領域に消去用正電圧を、消去対象ブロック内の全てのワード線に同じ消去用負電圧を、消去対象ブロックを除くメモリセルブロックに含まれる全てのメモリセルの制御ゲートに消去用正電圧を印加して消去処理を行なう。

(もっと読む)

メモリーセル、及びデータ記録方法

本発明は、少なくとも一のビット・データを記憶するメモリーセル(10)に関する。当該メモリーセルは、少なくとも二つの電気的接続(40、130)と、少なくとも一のポテンシャル井戸(200)を有するバンド曲線(EL)を伴う半導体構造(11)で構成されている。供給電圧(Us=Uspeis)を二つの電気的接続へ印加することによってポテンシャル井戸が電荷担体で帯電された状態が増大し、放電電圧(Us=Usperr)を印加することによって減少するほか、維持電圧(Us=Ubei)を印加することによってこの状態が維持されて、それぞれ帯電したポテンシャル井戸の状態がメモリーセルのビット・データ片を決定する。本発明によれば、この半導体構造が空間電荷ゾーン(Wn)を有しており、ポテンシャル井戸が半導体ヘテロ接合(80)によって形成されている。この半導体ヘテロ接合と空間電荷ゾーンは、維持電圧が印加されている場合は空間電荷ゾーン内に、供給電圧が印加されている場合は空間電荷ゾーンの周縁もしくは外に、放電電圧が印加されている場合は空間電荷ゾーン内に、半導体ヘテロ接合が位置するように、空間的に相対的な配置がなされている。 (もっと読む)

半導体集積回路装置およびアドレス変換テーブルの生成方法

【課題】初期化動作の時間を大幅に低減し、不揮発性半導体メモリの高速化を実現する。

【解決手段】不揮発性半導体メモリ2のメモリアレイMAは、データが格納されるデータ格納領域、プログラムが格納されるプログラム格納領域、およびプログラム格納領域のアドレス変換テーブルが格納されるテーブルブロックからなる。記憶装置1のパワーオンリセットにおいて、プログラム格納領域が設定されている場合には、テーブルブロックのアドレス変換テーブルを読み出し、レディ状態となり、プログラム格納領域PSAのリードが可能となる。その後、データ格納領域のイニシャライズ動作を行うことで、該データ格納領域のアドレス変換テーブルが生成され、データ格納領域のアクセスが可能となる。

(もっと読む)

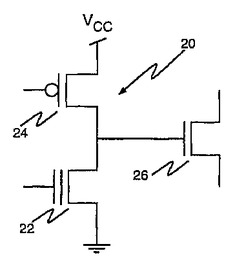

プログラマブルロジックアレイ用不揮発性プログラマブルメモリセル

プログラマブルロジックアレイに用いるために適した不揮発性プログラマブルメモリセルは、第2導電型の揮発性MOSトランジスタ24と直列に、第1導電型の不揮発性MOSトランジスタ22を具備する。不揮発性MOSトランジスタ22は、フラッシュトランジスタのようなフローティングゲートトランジスタであるか、又はフローティング電荷トラッピングSONOS、MONOSトランジスタ、若しくはナノ結晶トランジスタのような別のタイプの不揮発性トランジスタであってもよい。揮発性MOSトランジスタ、インバータ、又はバッファ26は、そのゲート又は入力を、不揮発性MOSトランジスタ22と揮発性MOSトランジスタ24との間のコモン接続点に接続することによって駆動される。  (もっと読む)

(もっと読む)

不揮発性半導体記憶装置及びその制御方法

【課題】読み出し動作信頼性を向上できる不揮発性半導体記憶装置及びその制御方法を提供すること。

【解決手段】不揮発性半導体記憶装置は、フローティングゲートを有する第1メモリセルがマトリクス状に配置された第1セルアレイと、フローティングゲートを有する第2メモリセルを複数含む第2セルアレイと、第1メモリセルのドレインに接続された第1ビット線と、第2メモリセルのドレインに接続された第2ビット線と、第1ビット線をプリチャージする第1プリチャージ回路と、第1メモリセルから読み出したデータを増幅するセンスアンプと、読み出し動作時において第2ビット線のプリチャージ及びディスチャージを行い、該第2ビット線のプリチャージ及びディスチャージに要した時間に基づいて、第1プリチャージ回路及びセンスアンプを制御する読み出し制御回路とを具備する。

(もっと読む)

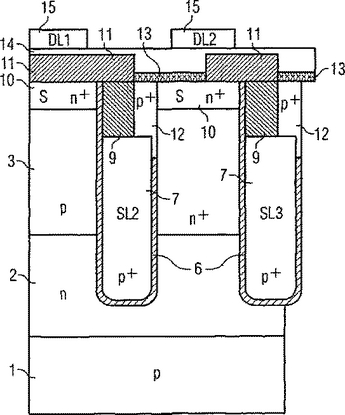

ビット線構造およびその製造方法

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

1 - 9 / 9

[ Back to top ]