Fターム[5F101BD32]の内容

不揮発性半導体メモリ (42,765) | 素子構造 (12,113) | アレイ (242) | 稠密アレイ構造 (233)

Fターム[5F101BD32]に分類される特許

1 - 20 / 233

半導体装置

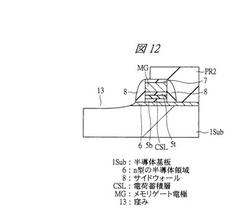

【課題】スプリットゲート型メモリセル構造を採用し、電荷蓄積層として窒化膜を用いる不揮発性メモリを有する半導体装置において電気的特性を向上させる。

【解決手段】半導体基板1Subの主面にn型の半導体領域6を形成した後、その上にスプリットゲート型のメモリセルのメモリゲート電極MGおよび電荷蓄積層CSLを形成する。続いて、そのメモリゲート電極MGの側面にサイドウォール8を形成した後、半導体基板1Subの主面上にフォトレジストパターンPR2を形成する。その後、フォトレジストパターンPR2をエッチングマスクとして、半導体基板1Subの主面の一部をエッチングにより除去して窪み13を形成する。この窪み13の形成領域では上記n型の半導体領域6が除去される。その後、その窪み13の形成領域にメモリセル選択用のnMISのチャネル形成用のp型の半導体領域を形成する。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ホールの微細化を図りつつ、ホールとスリットとを一括形成する。

【解決手段】4層分のワード線WL4〜WL1が順次積層されるとともに、ワード線WL4〜WL1にそれぞれ隣接するように4層分のワード線WL5〜WL8が順次積層され、ワード線WL5〜WL8が柱状体MP1にて貫かれるとともに、ワード線WL1〜WL4が柱状体MP2にて貫かれることで、NANDストリングNSが構成され、ワード線WL1〜WL8およびセレクトゲート電極SGD、SGSはロウ方向に沿って幅が周期的に変化されている。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

メモリ用シフトレジスタ

【課題】大容量なメモリ用シフトレジスタを提供する。

【解決手段】メモリ用シフトレジスタは、基板101と、基板101上に形成され、基板101の主面に垂直な軸Lの周りを回転する螺旋形状を有するチャネル層111とを備える。さらに、メモリ用シフトレジスタは、基板101上に形成され、軸Lに平行な方向に延びており、チャネル層111内の電荷を転送するために使用される3本以上の制御電極1121,1122,1123を備える。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

半導体装置の作製方法

【課題】複数のトランジスタが高集積化された素子の少なくとも一のトランジスタに、作製工程数を増加させることなくバックゲートを設ける半導体装置を提供する。

【解決手段】複数のトランジスタが上下に積層されて設けられた素子において、少なくとも上部のトランジスタ102は、半導体特性を示す金属酸化物により設けられ、下部のトランジスタ100が有するゲート電極層を上部のトランジスタのチャネル形成領域と重畳するように配して、ゲート電極層と同一の層の一部を上部のトランジスタ102のバックゲートBGとして機能させる。下部のトランジスタ100は、絶縁層で覆われた状態で平坦化処理が施され、ゲート電極が露出され、上部のトランジスタ102のソース電極及びドレイン電極となる層に接続されている。

(もっと読む)

半導体装置

【課題】ノーマリーオフのスイッチング素子を実現するトランジスタ構造およびその作製方法を提供する。トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する構成およびその作製方法を提供する。信頼性の高い半導体装置を提供する。

【解決手段】半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成比を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体層を用いる。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】用途に合わせて要求される電気的特性を備えた酸化物半導体層を用いたトランジスタ、及び該トランジスタを有する半導体装置を提供する。

【解決手段】酸化物絶縁膜上に、半導体層、ソース電極層又はドレイン電極層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタにおいて、該半導体層としてバンドギャップの異なる少なくとも2層の酸化物半導体層を含む酸化物半導体積層を用いる。酸化物半導体積層には、酸素又は/及びドーパントを導入してもよい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供と、さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図る。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】高いオン特性を有する酸化物半導体を用いたトランジスタを提供する。高速応答及び高速駆動の可能なトランジスタを有する高性能の半導体装置を提供する。

【解決手段】チャネル形成領域を含む酸化物半導体膜を有するトランジスタの作製工程において、該酸化物半導体膜に、金属元素を含む膜と接した状態で加熱処理することにより導入された金属元素と、注入法により該金属元素を含む膜を通過して導入されたドーパントとを含む低抵抗領域を形成する。低抵抗領域はチャネル長方向においてチャネル形成領域を挟んで形成する。

(もっと読む)

半導体装置の作製方法

【課題】DCスパッタリング法を用いて、酸化ガリウム膜を成膜する成膜方法を提供する

ことを課題の一つとする。トランジスタのゲート絶縁層などの絶縁層として、酸化ガリウ

ム膜を用いる半導体装置の作製方法を提供することを課題の一つとする。

【解決手段】酸化ガリウム(GaOxとも表記する)からなる酸化物ターゲットを用いて

、DCスパッタリング法、またはDCパルススパッタ方式により絶縁膜を形成する。酸化

物ターゲットは、GaOxからなり、Xが1.5未満、好ましくは0.01以上0.5以

下、さらに好ましくは0.1以上0.2以下とする。この酸化物ターゲットは導電性を有

し、酸素ガス雰囲気下、或いは、酸素ガスとアルゴンなどの希ガスとの混合雰囲気下でス

パッタリングを行う。

(もっと読む)

アプリケーション回路及び半導体デバイスの動作方法

【課題】バッテリレス電子タイマに適用される半導体デバイス、及びその動作方法とアプリケーション回路を提供する。

【解決手段】半導体デバイス600は、第1導電型半導体基板と、ゲート誘電層と、フローティングゲート606と、第2導電型ウェル608と、第1導電型ウェル610と、第2導電型ソース拡散層612と、第2導電型ドレイン拡散層614と、第2導電型制御ゲート拡散層616と、を含む。制御ゲート拡散層616、ソース拡散層612及びドレイン614の間の漏れ電流が二重のウェル領域上に印加されるバイアスを調節することにより減少される。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ162、トランジスタ162と異なる半導体材料を用いた読み出し用トランジスタ160及び容量素子164を含む不揮発性のメモリセルにおいて、メモリセルへの書き込みは、書き込み用トランジスタ162をオン状態とすることにより、書き込み用トランジスタ162のソース電極(またはドレイン電極)と、容量素子164の電極の一方と、読み出し用トランジスタ160のゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタ162をオフ状態とすることにより、ノードに所定量の電荷を保持させることで行う。また、読み出し用トランジスタ160として、pチャネル型トランジスタを用いて、読み出し電位を正の電位とする。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも

制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】トランジスタのオフ電流を十分に小さくすることができる材料、例えば、ワ

イドギャップ半導体である酸化物半導体材料を用いて半導体装置を構成する。トランジス

タのオフ電流を十分に小さくすることができる半導体材料を用いることで、長期間にわた

って情報を保持することが可能である。また、信号線の電位変化のタイミングを、書き込

みワード線の電位変化のタイミングより遅らせる。これによって、データの書き込みミス

を防ぐことが可能である。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】省電力化かつ高速での書き込み処理が可能なメモリの多値化に適した半導体装置およびベリファイ処理を提供する。

【解決手段】半導体装置に用いるメモリセルを、酸化物半導体を用いたトランジスタと酸化物半導体以外の材料を用いたトランジスタをそれぞれ有する構成とし、書き込み回路を用いてデータバッファのデータをメモリセルに書き込む前に、予め各々のメモリセルの有するしきい値ばらつきを調べ、データバッファのデータに対して当該しきい値ばらつきを補正したデータが各々のメモリセルに書き込む。

(もっと読む)

1 - 20 / 233

[ Back to top ]