Fターム[5F101BF01]の内容

不揮発性半導体メモリ (42,765) | 動作 (2,287) | 特性ヒステリシスしきい値 (921)

Fターム[5F101BF01]の下位に属するFターム

Fターム[5F101BF01]に分類される特許

1 - 20 / 143

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

不揮発性プログラマブルスイッチ

【課題】セル面積の小さい不揮発性プログラマブルスイッチを提供する。

【解決手段】第1配線に接続される第1端子と第2配線に接続される第2端子と第3配線に接続される第3端子とを有する第1不揮発性メモリトランジスタと、第4配線に接続される第4端子と第2配線に接続される第5端子と第3配線に接続される第6端子とを有する第2不揮発性メモリトランジスタと、第2配線にゲート電極が接続されたパストランジスタと、を備え、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも高い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が増加し、第2不揮発性メモリトランジスタの閾値電圧が低下し、第1および第4配線が第1電源に接続され、第3配線が第1電源の電圧よりも低い電圧に接続されるときに第1不揮発性メモリトランジスタの閾値電圧が低下し、第2不揮発性メモリトランジスタの閾値電圧が増加する。

(もっと読む)

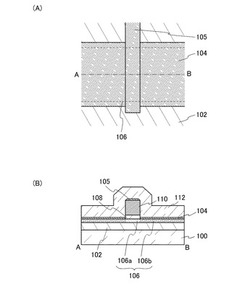

半導体装置および半導体装置の製造方法

【課題】トンネルウィンドウやセレクトゲートの加工寸法のばらつき、およびセレクトゲートのアライメント精度を考慮する必要がなく、セルサイズを小さくすることができる半導体装置およびその製造方法を提供すること。

【解決手段】不揮発性メモリセル7を半導体基板2上に選択的に備える半導体装置1が製造される。この製造方法は、ゲート絶縁膜23上において不揮発性メモリセル7用のアクティブ領域5に、セレクトゲート19を選択的に形成する工程と、セレクトゲート19に対して自己整合的に導入することによってn型トンネル拡散層11を形成する工程と、ゲート絶縁膜23の一部セレクトゲート19に対して自己整合的に除去し、その後の熱酸化によりトンネルウィンドウ25を形成する工程とを含む。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

論理回路

【課題】安定した高速動作を実現しつつ、製造工程も簡素化することが可能な論理回路を提供すること。

【解決手段】この論理回路1は、バイアス電源とグラウンドとの間で直列に接続され、それぞれのゲート端子に入力電圧が印加される第1及び第2のFET2A,2Bを備える論理回路であって、第1及び第2のFET2A,2BのうちのFET2Aは、ゲート端子が接続されるゲート電極膜17と、半導体材料からなるチャネル層12と、ゲート電極膜17とチャネル層12との間に配置され、電荷を蓄積及び放出する電荷蓄積構造を含む電荷蓄積層16と、を有する。

(もっと読む)

窒化シリコン膜の成膜方法、不揮発性記憶装置の製造方法

【課題】面内方向での膜厚の均一性に優れ、電荷保持特性に優れた窒化シリコン膜の成膜方法、及び窒化シリコン膜を備えた不揮発性記憶装置の製造方法を提供する。

【解決手段】半導体基板上に第2の窒化シリコン膜を形成する工程と、第2の窒化シリコン膜上に第2の窒化シリコン膜よりも光学吸収係数が大きくかつ光学吸収係数kが0.60〜1.26の第1の窒化シリコン膜を、ステップ成膜法により形成する工程と、を有する窒化シリコン膜の成膜方法。

(もっと読む)

半導体記憶装置及び半導体記憶素子

【課題】素子の面積を増大させることなく、かつ、コントロールゲート電圧を制御しなくとも、低電圧で書き込み量を大幅に増やすことが可能であり、また、安定して十分な書き込みを行うことが可能である不揮発性半導体装置を提供すること。

【解決手段】ドレインアバランシェホットエレクトロンにより書き込みを行う半導体記憶素子であって、第1導電型の半導体基板に形成された第2導電型の第1の半導体層と、前記第1の半導体層上に絶縁膜を介して設けられたフローティングゲートと、前記フローティングゲート下部の前記第1の半導体層の表面に形成されたチャネル領域と、前記チャネル領域に接触するように前記第1の半導体層上に設けられた第1導電型のソース領域及びドレイン領域とを有するMOSトランジスタであって、前記チャネル領域が2種類以上のキャリア濃度の分布をもつ半導体記憶素子とした。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択メモリセルトランジスタに電荷を蓄積する際の電圧を従来よりも自由に設定し得る不揮発性半導体記憶装置を提案する。

【解決手段】不揮発性半導体記憶装置1では、選択メモリセルトランジスタ115に電荷を蓄積させる際、電圧の高い書き込み禁止電圧をP型MOSトランジスタ9bから印加し、電圧の低い書き込み電圧をN型MOSトランジスタ15aから印加して、選択メモリセルトランジスタ115又は非選択メモリセルトランジスタ116へ電圧を印加する役割分担を、P型MOSトランジスタ9b及びN型MOSトランジスタ15aに分けたことで、P型MOSトランジスタ9b及びN型MOSトランジスタ15aそれぞれのゲート電圧やソース電圧を個別に調整でき、最終的にゲート基板間電圧を例えば4[V]等に設定し得る。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】高電界リークを低減して、書き込み特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。そして、前記電極間絶縁膜は、シリコン窒化膜もしくは高誘電率膜を2層のシリコン酸化膜で挟んだ積層構造または高誘電率膜とシリコン酸化膜の積層構造及び前記積層構造と前記制御電極層の間に形成された第2のシリコン窒化膜を有し、前記第2のシリコン窒化膜のうちの前記電荷蓄積層の上面上の部分を消失させた。

(もっと読む)

二重フローティングゲート構造を有するトランジスタを備えた不揮発性メモリ

【課題】CMOS製造プロセスに用いることのできる材料を用いかつノイズマージンの広い不揮発性メモリを提供する。

【解決手段】本実施形態の不揮発性メモリによれば、第1および第2のPチャネルトランジスタはそれぞれ第1の半導体領域上に設けられ、第1の半導体領域上に、第1の絶縁膜と、第1のフローティングゲート、第2の絶縁膜、第2のフローティングゲート、第3の絶縁膜、および第1の制御ゲートが、この順序で積層された構造を有し、前記第1および第2のNチャネルトランジスタはそれぞれ第2の半導体領域上に設けられ、前記第2の半導体領域上に、第4の絶縁膜、第3のフローティングゲート、第5の絶縁膜、第4のフローティングゲート、第6の絶縁膜、および第2の制御ゲートがこの順序で積層された積層構造を有している。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】隣接セルの書き込み閾値の変動を抑制すると共に、制御ゲート電極膜とシリコン基板との間のリーク電流を低減して消去特性を向上させる。

【解決手段】本実施形態の半導体装置は、半導体基板と、前記半導体基板における素子分離絶縁膜により区画された活性領域上にゲート絶縁膜を介して形成された電荷蓄積層と、前記素子分離絶縁膜の上面、前記電荷蓄積層の側面及び前記電荷蓄積層の上面に形成された電極間絶縁膜と、前記電極間絶縁膜上に形成された制御電極層とを備える。前記電極間絶縁膜は、第1のシリコン酸化膜、第1のシリコン窒化膜、第2のシリコン酸化膜および第2のシリコン窒化膜を積層形成した積層構造を有する。そして、前記電極間絶縁膜は、前記第2のシリコン酸化膜のうちの前記素子分離絶縁膜の上面上の部分の膜厚が前記電荷蓄積層の上面上の部分の膜厚より薄くなるように構成した。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

1 - 20 / 143

[ Back to top ]