Fターム[5F101BH13]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993)

Fターム[5F101BH13]の下位に属するFターム

ドライエッチング(方向性エッチング) (440)

ウェットエッチング(異方性エッチング) (424)

Fターム[5F101BH13]に分類される特許

1 - 20 / 129

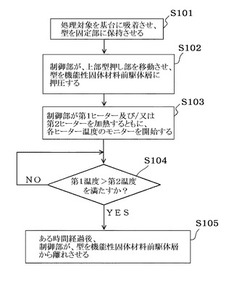

機能性デバイスの製造方法及び機能性デバイスの製造装置

【課題】機能性デバイスの高性能化、又はそのような機能性デバイスの製造プロセスの簡素化と省エネルギー化を提供する。

【解決手段】機能性デバイスの製造方法は、型押し工程と、機能性固体材料層形成工程を含む。型押し工程では、機能性固体材料前駆体溶液を出発材とする機能性固体材料前駆体層に対して型押し構造を形成する型を押圧している間の少なくとも一部の時間においてその機能性固体材料前駆体層に対して熱を供給する熱源の第1温度がその機能性固体材料前駆体層の第2温度よりも高くなるように、その機能性固体材料前駆体層に対して型押し加工を施す。また、機能性固体材料層形成工程では、型押し工程の後、酸素含有雰囲気中において、機能性固体材料前駆体層を前述の第1温度よりも高い第3温度で熱処理することにより、機能性固体材料前駆体層から機能性固体材料層を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】配線部に比べて引き出し部のスペースが広い場合においても、引き出し部の線幅を配線部の線幅に均一化できるようにする。

【解決手段】側壁パターン2a、2bおよび側壁ダミーパターン2c、2dをマスクとして被加工膜5を加工することにより、側壁パターン2aに対応した配線を下地層4上の配線部R1に形成するとともに、側壁パターン2bに対応した引き出し線5bを下地層4上の引き出し部R2に形成する。この時、下地層4上の引き出し部R2には、側壁ダミーパターン2cに対応したダミー引き出し線5cが引き出し線5bに並列に形成されるとともに、側壁ダミーパターン2dに対応したダミー引き出し線5dが引き出し線5bに並列に形成される。

(もっと読む)

半導体装置

【課題】結晶性の優れた酸化物半導体層を形成して電気特性の優れたトランジスタを製造

可能とし、大型の表示装置や高性能の半導体装置等の実用化を図ることを目的の一つとす

る。

【解決手段】第1の加熱処理で第1の酸化物半導体層を結晶化し、その上部に第2の酸化

物半導体層を形成し、温度と雰囲気の異なる条件で段階的に行われる第2の加熱処理によ

って表面と略垂直な方向にc軸が配向する結晶領域を有する酸化物半導体層の形成と酸素

欠損の補填を効率良く行い、酸化物半導体層上に接する酸化物絶縁層を形成し、第3の加

熱処理を行うことにより、酸化物半導体層に再度酸素を供給し、酸化物絶縁層上に、水素

を含む窒化物絶縁層を形成し、第4の加熱処理を行うことにより、少なくとも酸化物半導

体層と酸化物絶縁層の界面に水素を供給する。

(もっと読む)

半導体装置の製造方法

【課題】ラインスペースパターンと幅の広いパターンが混在する場合であっても、両パターンを精度よく加工する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、被加工層上にハードマスク層を形成する。その上に第1のマスク層を形成し、第1のマスク層をパターニングする。第1のマスク層が除去された領域にカーボン層を形成しパターニングする。カーボン層を部分的にエッチングし、カーボン層のパターン幅を縮小する。第1のマスク層と同一材料の第2のマスク層を形成し、エッチングによりカーボン層のパターンの両側面に第2のマスク層を残存させる。第2のマスク層のパターンに挟まれるカーボン層を除去する。第1および第2のマスク層のパターンをマスクにハードマスク層をパターニングする。第1および第2のマスク層のパターンを除去する。ハードマスク層のパターンをマスクに被加工層をパターニングする。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】SiN膜等の犠牲膜の残存を防止する。

【解決手段】一の実施形態による不揮発性半導体記憶装置の製造方法では、基板上に、複数のメモリセルトランジスタと、複数の選択トランジスタとを形成する。さらに、前記方法では、前記メモリセルトランジスタ間と、前記メモリセルトランジスタと前記選択トランジスタとの間と、前記選択トランジスタ間に、第1から第5の絶縁膜を順に埋め込む。さらに、前記方法では、前記選択トランジスタ間の前記第2及び第4の絶縁膜が一部残存するように、第1のエッチング処理により、前記第2及び第4の絶縁膜を除去する。さらに、前記方法では、前記選択トランジスタ間に残存した前記第2及び第4の絶縁膜を、前記第1のエッチング処理後に行う第2のエッチング処理により除去する。

(もっと読む)

不揮発性半導体記憶装置

【課題】選択ゲートトランジスタのゲート電極間の間隔の縮小を実現する不揮発性半導体記憶装置を提供する。

【解決手段】実施の形態の不揮発性半導体記憶装置は、半導体基板と、第1の方向に伸長する複数の第1の素子領域と、第1の素子領域を互いに分離する第1の素子分離領域と、第1の方向に伸長する複数の第2の素子領域と、第2の素子領域を互いに分離する第2の素子分離領域と、第1の素子領域と第2の素子領域との間に設けられ、第1および第2の素子領域に接続され、第1の方向と直交する第2の方向に伸長する第3の素子領域と、第1および第3の素子領域上にまたがり、第2の方向に伸長する第1の選択ゲート電極と、第2および第3の素子領域上にまたがり、第1の選択ゲート電極に隣接して平行に配置される第2の選択ゲート電極と、第1および第2の選択ゲート電極間の第3の素子領域に接続されるコンタクト電極を有する。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】ライナー膜をストッパ膜とした平坦化処理工程を設けることなくゲート電極上の段差を解消できるようにした不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置を提供する。

【解決手段】上端がキャップ膜と第2ゲート電極のシリコン層6との接触界面にほぼ一致するか低くなるようにメモリセルトランジスタの積層ゲート電極MG間および選択ゲート電極の積層ゲート電極SGD間に積層ゲート間絶縁膜8,9を形成する工程と、ライナー膜10を形成する工程と、選択ゲート電極SGD間のライナー膜10上に、第1の絶縁膜11を形成する工程と、ライナー膜10およびキャップ膜をエッチング処理する工程と、第1の絶縁膜11および積層ゲート間絶縁膜8,9をエッチングして第1の絶縁膜11の上面を第2ゲート電極6の上面高さとほぼ一致させる工程と、第2ゲート電極のシリコン層6の上部にシリサイド層7を形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】露光パターンのピッチの1/4のピッチのパターンを形成する方法でありながら、形成されたパターンの本数を4の倍数以外の数にする。

【解決手段】第2のパターンおよび第2のマスクパターンを覆うと共に第1の膜の上に第3の膜を形成する工程と、第3の膜をエッチバック処理することにより、第2のパターンおよび第2のマスクパターンの側壁に第1の側壁ラインパターンおよび第1の側壁マスクパターンをそれぞれ形成する工程と、第2のマスクパターンおよび第1の側壁マスクパターンを覆うように第3のマスクパターンを形成する工程と、第3のマスクパターンをマスクとし、第2のパターンを第1の側壁ラインパターンに対して選択的にエッチングして除去した後、第3のマスクパターンを除去する工程とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】側壁マスクプロセスにより同時に異なる幅を持つパターンを形成する。

【解決手段】実施形態に係わる半導体装置の製造方法は、被加工材12上に第1及び第2の芯材を形成する工程と、第1及び第2の芯材の上面及び側面を覆う第1及び第2の層16a,16bを有する被覆材を形成する工程と、第1の芯材を覆う第2の層16bを除去する工程と、被覆材をエッチングすることにより、第1の芯材の側面に第1の層16aを有する第1の側壁マスクを形成し、第2の芯材の側面に第1及び第2の層16a,16bを有する第2の側壁マスクを形成する工程と、第1及び第2の芯材を除去する工程と、第1及び第2の側壁マスクをマスクとして被加工材12をエッチングすることにより、異なる幅を持つ第1及び第2のパターンを同時に形成する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】 エアギャップ構造を簡易な方法で形成する。

【解決手段】 本発明の一態様の半導体装置の製造方法によれば、半導体基板上に導電層を含む被加工膜を形成する工程と、前記被加工膜上にダミー膜を形成する工程と、を備えている。さらに、前記ダミー膜を所望の形状にデポ条件の異方性エッチングにより加工する工程と、前記被加工膜を所望の形状に異方性エッチングにより加工する工程と、前記所望の形状に加工された被加工膜上の前記ダミー膜を異方性エッチングにより除去する工程と、前記被加工膜上に上層膜を形成する工程と、を備えている。

(もっと読む)

半導体装置の製造方法

【課題】加工膜と非加工膜をRIE法で選択的に加工するときに、非加工膜の加工量を低減させる半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地層1,7,8の上に非加工膜14を形成する工程と、非加工膜14および下地層1,7,8に溝4を形成する工程と、溝内を埋め込むように加工膜5を形成する工程と、非加工膜14を露出させるように加工膜5を平坦化する工程とを備える。更に、加工膜5および非加工膜14の上に保護膜16を形成する工程と、RIE法を用いて、保護膜16をエッチングすると共に、加工膜5を選択的にエッチングして溝内の加工膜5を落とし込む工程とを備える。

(もっと読む)

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】デバイス特性及びプロセスのばらつきを低減できる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板10と、下部ゲート層BGと、積層体と、ダミー電極層DWLと、絶縁膜30と、チャネルボディ20,45とを備えた。下部ゲート層BGは、基板10上に設けられた。積層体は、下部ゲート層BG上にそれぞれ交互に積層された複数の絶縁層と複数の電極層WLとを有する。ダミー電極層DWLは、下部ゲート層BGと積層体との間に設けられ、電極層WLと同じ材料からなり、各々の電極層WLよりも厚い。絶縁膜30は、積層体及びダミー電極層を貫通して形成されたホールMHの側壁に設けられた電荷蓄積膜を含む。チャネルボディ20,45は、ホールMH内における絶縁膜30の内側に設けられた。

(もっと読む)

不揮発メモリ装置及び不揮発メモリ装置の製造方法

【課題】不揮発メモリ装置のメモリセルを小型化する。

【解決手段】フローティングゲート電極120は、トンネル絶縁膜110の上に形成されている。コントロールゲート電極140は、第1絶縁膜130を介してフローティングゲート電極120の上に形成されている。セレクトゲート絶縁膜150は、基板10の上に形成されており、トンネル絶縁膜110の横に位置している。セレクトゲート電極170はセレクトゲート絶縁膜150上に位置している。またセレクトゲート電極170は、第2絶縁膜160を介してフローティングゲート電極120の横に位置している。そしてセレクトゲート電極170のうちフローティングゲート電極120に面する側面は、下端174が第2絶縁膜160の下に入り込んでいる。

(もっと読む)

不揮発性半導体記憶装置

【課題】各メモリセルの書込消去特性を極力一定にできる不揮発性半導体記憶装置を提供する。

【解決手段】複数のメモリセルトランジスタMTは、活性領域Saが素子分離溝2によって互いに分離している。これらのメモリセルトランジスタMTは、それぞれ、活性領域Saの上面上または上方にトンネル絶縁膜3を介して電荷蓄積機能を有する電荷トラップ膜4を備えている。積層絶縁膜Bは、トンネル絶縁膜3および電荷トラップ膜4を少なくとも含んで構成され、トンネル絶縁膜3が素子分離溝2の内面に沿って形成されると共に電荷トラップ膜4がトンネル絶縁膜3の上面に沿って積層されており、素子分離溝2内の全領域に埋込まれている。

(もっと読む)

2つの自己整合型独立ゲートを有するメモリの製作

【課題】並置されたゲートを有するトランジスタを備えるマイクロエレクトロニクス不揮発性メモリデバイスを作る方法を提供する。

【解決手段】支持体上にある、少なくとも1つの第1のゲート材料に基づく層内に、少なくとも1つの第1のトランジスタゲートブロックおよび少なくとも1つの犠牲ブロックを形成する段階であって、前記第1のブロックおよび前記犠牲ブロックが、所与のスペースだけ隔てられる段階aと、前記所与のスペース内に、少なくとも1つの絶縁層および少なくとも1つの第2のゲート材料を含むスタックを形成する段階であって、前記スペース内に位置する前記ゲート材料が、第1のブロックから前記絶縁層だけ隔たった第2のゲートブロックを形成するように意図されている段階bと、前記犠牲ブロックを除去する段階cとを含む方法。

(もっと読む)

半導体装置の製造方法

【課題】側壁転写技術により倒れにくいマスクパターンを形成するNANDフラッシュメモリ等の製造方法を提供する。

【解決手段】非晶質シリコン膜21上に第1膜のシリコン酸化膜22を形成し(a)、所定のラインアンドスペースのパターンに加工して中間パターン23を形成する(b)。中間パターン23は、パターン部23aを有するとともに、パターン部23aの間に残存部23bを残してた状態で形成される。中間パターン23をスリミング処理し、非晶質シリコン膜21上に芯材パターン24を形成する(c)。残存部23bは除去される。芯材パターン24上に第2膜のシリコン窒化膜を形成し、エッチバック処理で側壁パターンを形成し、芯材パターン24を除去してマスクパターンを得る。マスクパターンは、段差のない非晶質シリコン膜21上に形成されるので応力差に起因した倒れの発生を抑制できる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置を提供する。

【解決手段】第1の配線と、第2の配線と、第3の配線と、第4の配線と、第1のトランジスタ160と、第2のトランジスタ162と、を有し、第1のトランジスタ160は、半導体材料を含む基板に設けられ、第2のトランジスタ162は酸化物半導体層を含んで構成され、第1のトランジスタ160のゲート電極と、第2のトランジスタ162のソース・ドレイン電極とは、電気的に接続され、第1の配線と、第1のトランジスタ160のソース電極とは、電気的に接続され、第2の配線と、第1のトランジスタ160のドレイン電極とは、電気的に接続され、第3の配線と、第2のトランジスタ162のソース・ドレイン電極の他方とは、電気的に接続され、第4の配線と、第2のトランジスタ162のゲート電極とは、電気的に接続される。

(もっと読む)

1 - 20 / 129

[ Back to top ]