Fターム[5F101BH14]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | エッチング (993) | ドライエッチング(方向性エッチング) (440)

Fターム[5F101BH14]に分類される特許

1 - 20 / 440

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの電荷蓄積層内での電荷の横方向の移動を抑制する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1乃至第nの半導体層(nは2以上の自然数)12−1〜12−3と、第1乃至第nの半導体層12−1〜12−3をチャネルとする第1乃至第nのメモリストリングS1〜S3とを備える。第iのメモリストリング(iは1〜nのうちの1つ)Siは、第iの半導体層12−iの第3の方向にある表面上に、複数のメモリセルMCに対応する、複数の電荷蓄積層16及び複数のコントロールゲート18を備える。また、第iのメモリストリング内において、少なくとも第2の方向に隣接する2つのメモリセルMCの電荷蓄積層16が互いに結合される。そして、複数のコントロールゲート18間に、複数の電荷蓄積層16のバンドオフセットを上昇させる金属元素19が添加される。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化されたトランジスタのオン特性を向上させる。微細化されたトランジスタを歩留まりよく作製する。

【解決手段】一対の低抵抗領域及び該低抵抗領域に挟まれるチャネル形成領域を含む酸化物半導体層と、ゲート絶縁層を介してチャネル形成領域と重畳する第1のゲート電極層と、第1のゲート電極層のチャネル長方向の側面及びゲート絶縁層の上面と接し、一対の低抵抗領域と重畳する一対の第2のゲート電極層と、第2のゲート電極層上の、側端部を第2のゲート電極層の側端部と重畳する一対の側壁絶縁層と、を有する半導体装置を提供する。

(もっと読む)

シリコン膜の形成方法及び半導体装置の製造方法

【課題】狭スペースへのシリコン膜の埋め込み性の向上を図る。

【解決手段】実施形態によれば、シリコン膜の形成方法は、凹部20の開口側からボトム側に向けてくぼんだくぼみ40を有するアンドープの第1のシリコン膜32を凹部20に形成する工程を含む。また、前記シリコン膜の形成方法は、凹部20内の第1のシリコン膜32の一部を塩素を含むガスを用いてエッチングし、第1のシリコン膜32に凹部20のボトム側よりも開口側で幅が広い隙間41を形成する工程を含む。また、前記シリコン膜の形成方法は、隙間41に面する第1のシリコン膜32の内壁に不純物を添加する工程を含む。また、前記シリコン膜の形成方法は、不純物の添加後、隙間41を埋める第2のシリコン膜33を形成する工程を含む。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを提供する。

【解決手段】ソース電極層及びドレイン電極層上を覆うように酸化物半導体層を成膜した後、ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を研磨により除去する。ソース電極層及びドレイン電極層と重畳する領域の酸化物半導体層を除去する工程において、レジストマスクを用いたエッチング工程を用いないため、精密な加工を正確に行うことができる。また、ゲート電極層のチャネル長方向の側面に導電性を有する側壁層を設けることで、当該導電性を有する側壁層がゲート絶縁層を介してソース電極層又はドレイン電極層と重畳し、実質的にLov領域を有するトランジスタとする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

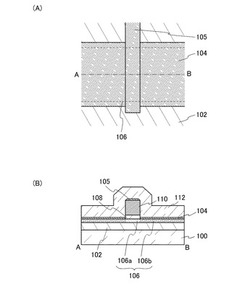

半導体装置

【課題】微細化が可能な半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、上面に、一方向に延び上方に突出した複数本のアクティブエリアが形成された半導体基板と、前記アクティブエリア間のトレンチの下部に埋め込まれた素子分離絶縁体と、第1の絶縁材料からなり、前記素子分離絶縁体の直上域に配置され、下部が前記トレンチ内に配置され、上部が前記アクティブエリアの上端よりも上方に突出した絶縁ブロックと、前記第1の絶縁材料とは異なる第2の絶縁材料からなり、前記半導体基板及び前記絶縁ブロックの上方に設けられた層間絶縁膜と、前記層間絶縁膜内に形成され、下端が前記アクティブエリアの上面に接続されたコンタクトと、を備える。前記コンタクトにおける前記絶縁ブロックの直上域に位置する部分の下面は、前記コンタクトにおける前記アクティブエリアの直上域に位置する部分の下面よりも上方に位置している。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】寄生抵抗がより低いチャネルボディ層を有する不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態の不揮発性半導体記憶装置は、半導体層と、第1絶縁層が表面に設けられた第2絶縁層と、第3絶縁層と、第2絶縁層および第3絶縁層の上に、電極層と絶縁膜とを有する第1積層体と、第1積層体の積層方向に貫通し第2絶縁層に達する一対の第1ホールのそれぞれの側壁に設けられたメモリ膜と、メモリ膜の内側に設けられた第1チャネルボディ層と、層間絶縁膜と選択ゲートとを有する第2積層体と、一対の第1ホールのそれぞれ上端と連通し、第2積層体の積層方向に貫通する第2ホールの側壁に設けられたゲート絶縁膜と、ゲート絶縁膜の内側に設けられた第2チャネルボディ層と、第1積層体の下側に設けられた連結部と、一対の第1ホールの間に挟まれ、第1積層体の表面から第1絶縁層に達する第4絶縁層と、を備える。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】不揮発性半導体記憶装置の加工精度をより向上させる。

【解決手段】実施形態によれば、不純物含有領域と、被エッチング領域と、を有する半導体層を形成し、それぞれの表面から内部にかけて第1絶縁層を形成し、第1絶縁膜を介して、半導体層上に複数の電極層を含む積層体を形成し、積層体に、被エッチング領域に達し第2絶縁層を挟む一対のホールを形成し、被エッチング領域を一対のホールを通じて除去し、半導体層に一対のホールのそれぞれの下端とつながった空間部を形成し、一対のホールのそれぞれの側壁に、メモリ膜を形成し、空間部の内壁に第4絶縁層を形成し、一対のホールのそれぞれの側壁と空間部の内壁とに形成されたメモリ膜の表面に、チャネルボディ層を形成する。

(もっと読む)

半導体装置の製造方法

【課題】低コスト化を図ることができる半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、半導体基板上にボロンを含む膜を形成する工程と、前記ボロンを含む膜上に酸化シリコンを含む膜を形成する工程と、前記酸化シリコンを含む膜をパターニングする工程と、前記パターニングされた前記酸化シリコンを含む膜をマスクとして、前記ボロンを含む膜を、塩素を含むガスを用いてエッチングする工程と、を備える。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】選択ゲートの閾値電圧の変動が抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、交互に積層された複数の電極層と複数の第1絶縁層とを有する第1積層体と、第1積層体を貫通する第1ホールの側壁に設けられたメモリ膜と、第1ホール内に設けられたメモリ膜の内側に設けられた第1チャネルボディ層と、第1積層体の上に設けられた層間絶縁膜と、層間絶縁膜の上に設けられた選択ゲート電極層と、選択ゲート電極層の上に設けられた第2絶縁層と、を有する第2の積層体と、第1ホールに連通し第2積層体および層間絶縁膜を貫通する第2ホールの側壁に設けられたゲート絶縁膜と、第2ホール内におけるゲート絶縁膜の内側に設けられ、第1チャネルボディ層とつながった第2チャネルボディ層と、を備える。選択ゲート電極層と第2絶縁層との界面における第2ホールの径は選択ゲート電極層と層間絶縁膜との界面における第2ホールの径よりも小さい。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】シリサイド工程によるゲート絶縁膜の金属汚染や、メモリセルのショートチャネル効果を抑制する。

【解決手段】実施形態によれば、不揮発性半導体記憶装置は、半導体基板と、前記半導体基板上に順に形成された第1絶縁層、電荷蓄積層、第2絶縁層、および制御電極を有し、前記電荷蓄積層の側面が傾斜面を有する複数のメモリセルトランジスタとを備える。さらに、前記装置は、前記メモリセルトランジスタの側面と、前記メモリセルトランジスタ間の前記半導体基板の上面に形成された第1の絶縁膜部分と、前記メモリセルトランジスタ間のエアギャップ上と前記メモリセルトランジスタ上に連続して形成された第2の絶縁膜部分と、を有する1層以上の絶縁膜を備える。さらに、前記メモリセルトランジスタ間の前記半導体基板の上面から前記エアギャップの下端までの第1距離は、前記メモリセルトランジスタの側面に形成された前記絶縁膜の膜厚よりも大きい。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】信頼性を向上させることができる半導体記憶装置及びその製造方法を提供することである。

【解決手段】実施形態に係る半導体記憶装置は、積層して設けられた複数のゲート電極と、前記ゲート電極の間に設けられた絶縁膜と、を有した積層体と、前記積層体を貫く半導体ピラーと、前記半導体ピラーと前記ゲート電極との間に空隙を介して設けられた電荷蓄積層と、前記電荷蓄積層と前記ゲート電極との間に設けられたブロック絶縁層と、を有したメモリセルを積層方向に複数備えている。そして、前記複数の各メモリセル毎に、前記電荷蓄積層と前記半導体ピラーとの間の距離を保つ支持部が設けられている。

(もっと読む)

酸化物半導体膜の成膜方法、半導体装置および半導体装置の作製方法

【課題】酸化物半導体を用いたトランジスタは、非晶質シリコンを用いたトランジスタと比較して信頼性が劣る場合があった。そこで、信頼性が高い酸化物半導体を用いたトランジスタを有する半導体装置を提供する。

【解決手段】酸化物半導体膜に含まれる水素、窒素および炭素などの不純物は酸化物半導体膜の半導体特性を低下させる要因となる。例えば、酸化物半導体膜に含まれる水素および窒素は、酸化物半導体膜を用いたトランジスタのしきい値電圧をマイナス方向へシフトさせてしまう要因となる。また、酸化物半導体膜に含まれる窒素、炭素および希ガスは、酸化物半導体膜中に結晶領域が生成されることを阻害する。そこで、酸化物半導体膜の不純物濃度を低減することで、高い信頼性を有するトランジスタを作製する。

(もっと読む)

1 - 20 / 440

[ Back to top ]