Fターム[5F101BH16]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | 熱処理 (725)

Fターム[5F101BH16]に分類される特許

161 - 180 / 725

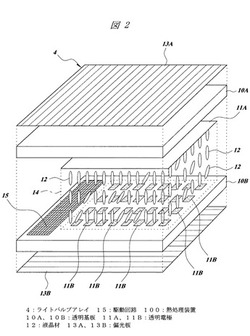

熱処理装置

【課題】半導体薄膜を低熱負荷で均一に改質することのできる熱処理装置を提供する。

【解決手段】熱処理装置100の光学系は、一対の透明基板10A、10Bと、透明基板10A、10Bのそれぞれに設けられた透明電極11A、11Bと、透明電極11A、11Bに挟まれた液晶材12と、透明基板10A、10B、透明電極11A、11Bおよび液晶材12を挟む一対の偏光板13A、13Bとを備えたライトバルブアレイ4を有している。透明電極11Bは、ライトバルブアレイ領域14内でマトリクス状に細分化され、それぞれの透明電極11Bには、駆動回路15の選択スイッチを介して独立に電圧が印加される。

(もっと読む)

記憶装置

【課題】誤書込みを防止することが可能な記憶装置を提供する。

【解決手段】複数のメモリセルが直列に接続されたNANDセルユニットと、NANDセルユニットの一方の端子に接続する第1の選択トランジスタと、NANDセルユニットの他方の端子に接続する第2の選択トランジスタと、第1の選択トランジスタと接続するソース線と、該ソース線と交差し、且つ第2の選択トランジスタと接続するビット線とを有し、第1の選択トランジスタ及び第2の選択トランジスタは、チャネル領域が酸化物半導体層で形成されたトランジスタである。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体層の側面からの酸素の脱離を防ぎ、酸化物半導体層中の欠陥(酸素欠損)が十分に少なく、ソースとドレインの間のリーク電流が抑制された半導体装置を提供する。

【解決手段】酸化物半導体膜に対して第1の加熱処理を施した後に該酸化物半導体膜を加工して酸化物半導体層を形成し、その直後に該酸化物半導体層の側壁を絶縁性酸化物で覆い、第2の加熱処理を施すことで、酸化物半導体層の側面が真空に曝されることを防ぎ、酸化物半導体層中の欠陥(酸素欠損)を少なくして半導体装置を作製する。酸化物半導体層の側壁はサイドウォール絶縁層により覆われている。なお、該半導体装置はTGBC(Top Gate Bottom Contact)構造とする。

(もっと読む)

記憶素子、記憶装置、信号処理回路、記憶素子の駆動方法

【課題】電源電圧の供給が停止した後もデータ保持可能な記憶素子を提供する。消費電力の低減可能な信号処理回路を提供する。

【解決手段】クロック信号に同期してデータを保持する記憶素子において、酸化物半導体層にチャネルが形成されるトランジスタ及び容量素子を用いることより、電源電圧の供給が停止した間もデータ保持ができる。ここで、電源電圧の供給を停止する前に、クロック信号のレベルを一定に保った状態で当該トランジスタをオフ状態とすることにより、データを正確に容量素子に保持させることができる。また、このような記憶素子を、CPU、メモリ、及び周辺制御装置のそれぞれに用いることによって、CPUを用いたシステム全体で、電源電圧の供給停止を可能とし、当該システム全体の消費電力を削減することができる。

(もっと読む)

半導体装置の駆動方法

【課題】新たな構造の半導体装置、及びその駆動方法を提供することを目的の一とする。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のpチャネル型トランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電荷を保持させることで行う。また、保持期間において、メモリセルを選択状態とし、且つ、読み出し用トランジスタのソース電極およびドレイン電極を同電位とすることで、ノードに蓄積された電荷を保持する。

(もっと読む)

半導体メモリ装置

【課題】短チャネルでも動作するフローティングゲートを有する半導体メモリ装置を提供する。

【解決手段】フローティングゲート104に窒化インジウム、窒化亜鉛等の仕事関数が5.5電子ボルト以上の高仕事関数化合物半導体を用いる。このことにより、基板101とフローティングゲート104の間のフローティングゲート絶縁膜103のポテンシャル障壁が従来のものより高くなり、フローティングゲート絶縁膜103を薄くしても、トンネル効果による電荷の漏洩を低減できる。フローティングゲート絶縁膜103をより薄くできるのでチャネルをより短くできる。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の変動が生じにくく、且つ電気特性の良好な半導体装置の作製方法を提供することである。

【解決手段】基板上にゲート電極を形成し、ゲート電極上にゲート絶縁膜を形成し、酸化物半導体膜を形成し、第1の酸化物半導体膜を形成した後、加熱処理をして第2の酸化物半導体膜を形成し、第1の導電膜を形成し、厚さの異なる領域を有する第1のレジストマスクを形成し、第1のレジストマスクを用いて第2の酸化物半導体膜および第1の導電膜をエッチングして第3の酸化物半導体膜および第2の導電膜を形成し、第1のレジストマスクを縮小させて、第2のレジストマスクを形成し、第2のレジストマスクを用いて第2の導電膜の一部を選択的に除去することでソース電極およびドレイン電極を形成する半導体装置の作製方法である。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

記憶装置、半導体装置、検出方法

【課題】データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を、短時間にて正確に行うことができる記憶装置の提供。

【解決手段】各メモリセルに、第1容量素子と、第2容量素子と、上記第1容量素子及び第2容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子として機能するトランジスタと、を少なくとも有する。また、第1容量素子の容量値が、第2容量素子の容量値の1000倍以上、好ましくは10000倍以上となるようにする。そして、通常動作の時に、第1容量素子及び第2容量素子を用いて電荷の保持を行う。また、データの保持時間が所定の長さに満たないメモリセルを検出するための検証動作を行う時に、第2容量素子を用いて電荷の保持を行う。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】良好な電気特性及び信頼性を有する不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板と、半導体基板に形成された素子分離溝に埋め込まれた素子分離絶縁膜と、素子分離溝により所定間隔だけ隔てられ、且つ、半導体基板上に第1の絶縁膜と電荷蓄積膜とが順次積層されてなる積層構造の複数のメモリセルと、電荷蓄積膜と素子分離絶縁膜との上に形成された第2の絶縁膜と、第2の絶縁膜上に形成された制御電極膜とを有し、素子分離絶縁膜の上面は電荷蓄積膜の上面よりも低く、第2の絶縁膜は、電荷蓄積膜上のセル上部分と素子分離絶縁膜上のセル間部分とを備え、セル上部分の誘電率はセル間部分の誘電率よりも低い。

(もっと読む)

半導体記憶装置の製造方法、及び半導体記憶装置

【課題】1つの実施形態は、例えば、トンネル電流を容易に増加できる半導体記憶装置の製造方法、及び半導体記憶装置を提供することを目的とする。

【解決手段】1つの実施形態によれば、半導体記憶装置の製造方法が提供される。半導体記憶装置の製造方法では、Ge、Sn、C、及びNのいずれかの不純物を半導体基板の表面に導入する。半導体記憶装置の製造方法では、前記不純物が導入された前記半導体基板の表面にトンネル絶縁膜が形成されるように、前記半導体基板を熱酸化する。半導体記憶装置の製造方法では、前記トンネル絶縁膜上に電荷蓄積層を有するゲートを形成する。半導体記憶装置の製造方法では、前記ゲートと自己整合的に前記半導体基板内に不純物拡散領域を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】デバイス特性に優れた半導体装置およびその製造方法を提供する。

【解決手段】実施の一形態の半導体装置は、第1および第2の領域を有する機能膜と、前記基板の前記第1の領域に設けられ、第1の幅を有する第1の溝と、前記基板の前記第2の領域に設けられ、第1の幅よりも広い第2の幅を有する第2の溝と、前記第1の溝を埋めるように高分子材料を前駆体として形成された第1の絶縁膜と、前記第1の幅を上回る直径を有し、前記第2の溝を埋める微粒子と、前記第2の溝内で前記微粒子間および前記微粒子と前記第2の溝との間隙を埋める前記高分子材料とを前駆体として形成された第2の絶縁膜とを持つ。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体膜をチャネル形成領域に用いたトランジスタにおいて、短チャネル効果による電気特性の変動を抑制し、微細化した半導体装置を提供する。また、オン電流を向上させた半導体装置を提供する。

【解決手段】非晶質領域である一対の第2の酸化物半導体領域と、一対の第2の酸化物半導体領域に挟まれた第1の酸化物半導体領域と、を有する酸化物半導体膜と、ゲート絶縁膜と、ゲート絶縁膜を介して第1の酸化物半導体領域上に設けられるゲート電極と、を有する半導体装置において、第2の酸化物半導体領域には、窒素、リン、又は砒素など15族元素のいずれか一以上の元素が添加されている。

(もっと読む)

信号処理回路

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路。特に、短時間の電源停止により消費電力を抑えることができる信号処理回路。

【解決手段】制御装置と、演算装置と、緩衝記憶装置とを有し、緩衝記憶装置は、主記憶装置から、或いは演算装置から送られてきたデータを、制御装置からの命令に従って記憶し、緩衝記憶装置は複数のメモリセルを有し、メモリセルは、チャネル形成領域に酸化物半導体を含むトランジスタと、トランジスタを介してデータの値に従った量の電荷が供給される記憶素子とを有する信号処理回路。

(もっと読む)

半導体装置

【課題】半導体装置の高集積化を図り、単位面積あたりの記憶容量を増加させる。

【解決手段】半導体装置は、半導体基板に設けられた第1のトランジスタと、第1のトランジスタ上に設けられた第2のトランジスタとを有する。また、第2のトランジスタの半導体層は、半導体層の上側で配線と接し、下側で第1のトランジスタのゲート電極と接する。このような構造とすることにより、配線及び第1のトランジスタのゲート電極を、第2のトランジスタのソース電極及びドレイン電極として機能させることができる。これにより、半導体装置の占有面積を低減することができる。

(もっと読む)

半導体装置

【課題】微細化による電気特性の変動が生じにくい半導体装置を提供する。

【解決手段】第1の領域と、第1の領域の側面に接した一対の第2の領域と、一対の第2の領域の側面に接した一対の第3の領域と、を含む酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜上に第1の領域と重畳した第1の電極と、を有し、第1の領域は、CAAC酸化物半導体領域であり、一対の第2の領域及び一対の第3の領域は、ドーパントを含む非晶質な酸化物半導体領域であり、一対の第3の領域のドーパント濃度は、一対の第2の領域のドーパント濃度より高い半導体装置である。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】複数のメモリセルを3次元状に配置し、かつ、メモリセルにMONOS型トランジスタを使用するNAND型不揮発性メモリにおいて、データ保持特性の劣化を抑制することができる技術を提供する。

【解決手段】ギャップ絶縁層GIL1の右端部側に凹部CUが形成されている。このとき、この凹部CUの形状を反映するように、凹部CUの内部に上部電位障壁層EB2と電荷蓄積層ECが形成されており、この凹部CUの形状を反映した電荷蓄積層ECの内側に形成される下部電位障壁層EB1によって、凹部CUが完全に埋め込まれている。このため、凹部CUを埋め込んだ下部電位障壁層EB1の表面は平坦になっており、この平坦になっている下部電位障壁層EB1の内側に柱状半導体部PSが形成される。

(もっと読む)

半導体記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能(不揮発性)で、且つ、書き込み回数にも制限が無い、新たな構造の半導体記憶装置を提供する。

【解決手段】半導体記憶装置に、複数のメモリセルがマトリクス状に配設されたメモリセルアレイと、制御信号に応じて、複数のメモリセルの中から動作を行うメモリセルを選択するデコーダと、デコーダに対して制御信号を出力するか否かを選択する制御回路と、を設ける。なお、複数のメモリセルのそれぞれは、酸化物半導体によってチャネル領域が形成される選択トランジスタをオフ状態とすることによってデータの保持を行う。

(もっと読む)

半導体装置の製造方法

【課題】注入した不純物の拡散を抑制しつつ結晶欠陥を低減する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、リンまたはボロンを分子状イオンの形態で含有する第1の不純物80と、リンまたはボロンよりも注入量が少ない炭素、フッ素または窒素を分子状イオンの形態で含有する、もしくは、リンまたはボロンよりも注入量が少ない炭素を原子イオンの形態で含有する第2の不純物81と、を半導体層1に注入して不純物注入層9を形成する工程を含む。

(もっと読む)

161 - 180 / 725

[ Back to top ]