Fターム[5F101BH26]の内容

不揮発性半導体メモリ (42,765) | 製造方法 (5,495) | テストエージング (92)

Fターム[5F101BH26]に分類される特許

1 - 20 / 92

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

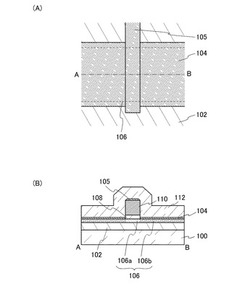

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜の水素濃度および酸素欠損を低減する。また、酸化物半導体膜を用いたトランジスタを有する半導体装置の信頼性を向上させる。

【解決手段】下地絶縁膜と下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜に重畳して設けられたゲート電極と、を有し、下地絶縁膜は、電子スピン共鳴にてg値が2.01で信号を表し、酸化物半導体膜は、電子スピン共鳴にてg値が1.93で信号を表さない半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

半導体不揮発性メモリ及びデータ書き込み方法

【課題】データ書き込み時における書き込み回数を減らし、且つ読み出し精度を高めることが可能な半導体不揮発性メモリ及びデータ書き込み方法を提供する。

【解決手段】書き込むべきデータの値に対応した量の電荷を電荷蓄積部に注入することによって書き込みを行うデータ書き込み手段を有し、データ書き込み手段によるデータの書き込みに先立ち、電荷蓄積部各々から読み出し電流を送出させ、読み出し電流が最大読み出し電流閾値よりも大となる電荷蓄積部に、この読み出し電流が最大読み出し電流閾値を下回るまで電荷を注入する初期化書き込みを行う。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

不揮発性半導体記憶装置

【課題】正確に書き込み動作を行うことができる不揮発性半導体記憶装置を提供する。

【解決手段】

複数の素子分離絶縁膜は、半導体層中に形成され、第1方向を長手方向とする。複数の素子形成領域は、素子分離絶縁膜により分離して形成される。素子形成領域にはメモリストリングが形成される。複数の素子形成領域群が素子形成領域により構成される。メモリセルアレイは、第1方向と直交する第2方向において、前記素子形成領域群の間隔が前記素子形成領域群の中の前記素子形成領域の間隔より大きくされている。制御回路は、前記メモリセルアレイに対する書き込み動作を、前記素子形成領域群ごとに実行する。

(もっと読む)

不揮発性半導体記憶装置

【課題】データの劣化を抑制した不揮発性半導体記憶装置を提供する。

【解決手段】メモリセルは、半導体層、電荷蓄積層、及び導電層を備える。半導体層は、半導体基板に対して垂直方向に延び、メモリセルのボディとして機能する。電荷蓄積層は、半導体層の側面に設けられ、電荷を蓄積する。導電層は、半導体層と電荷蓄積層を挟むよう設けられ、メモリセルのゲートとして機能する。制御回路は、第1プログラム動作の後、第2プログラム動作を実行する。第1プログラム動作は、メモリセルのボディに第1電圧を印加し且つメモリセルのゲートに第1電圧よりも大きい第2電圧を印加することによりメモリセルの閾値電圧を正方向に移動させる動作である。第2プログラム動作は、メモリセルのボディをフローティングにし且つメモリセルのゲートに正の第3電圧を印加する動作である。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置の駆動方法

【課題】半導体装置の駆動方法を提供する。

【解決手段】酸化物半導体を用いた書き込み用トランジスタ、該トランジスタと異なる半導体材料を用いた読み出し用のトランジスタ及び容量素子を含む不揮発性のメモリセルを有する半導体装置を提供する。メモリセルへの書き込みは、書き込み用トランジスタをオン状態として、書き込み用トランジスタのソース電極と、容量素子の電極の一方と、読み出し用トランジスタのゲート電極とが電気的に接続されたノードに電位を供給した後、書き込み用トランジスタをオフ状態として、ノードに所定量の電位を保持させることで行う。メモリセルの読み出しは、ビット線にプリチャージ電位を供給した後ビット線への電位の供給を止め、ビット線の電位がプリチャージ電位に保たれるか、または電位が下がるか、により行う。

(もっと読む)

記憶装置

【課題】データを保持する期間を確保しつつ、単位面積あたりの記憶容量を高めることが

できる記憶装置の提案を目的の一とする。

【解決手段】記憶素子と、記憶素子における電荷の蓄積、保持、放出を制御するための、

酸化物半導体を活性層に含むトランジスタと、記憶素子に接続された容量素子とを有する

記憶装置。上記容量素子が有する一対の電極の少なくとも一方は、遮光性を有している。

さらに、上記記憶装置は遮光性を有する導電膜或いは絶縁膜を有しており、上記活性層が

、遮光性を有する電極と、遮光性を有する導電膜或いは絶縁膜との間に位置する。

(もっと読む)

記憶装置

【課題】電力が供給されない状況でも記憶内容の保持が可能であり、記憶素子を構成するトランジスタをオンすることなく、記憶したデータを高速で読み出すことができる記憶装置を提供する。

【解決手段】記憶装置において、酸化物半導体層をチャネル領域として有するトランジスタ及び保持容量素子を有するメモリセルと、容量素子と、を電気的に接続させてノードを構成し、該ノードは保持容量素子を介した容量結合により保持データに応じて昇圧され、この電位を増幅回路によって読み出すことで、データの識別を行うことができる。

(もっと読む)

記憶装置、及び半導体装置

【課題】プロセスを複雑化させることなく、単位面積あたりの記憶容量を高めることができる記憶装置を提案する。

【解決手段】複数のメモリセルと、複数のワード線と、複数のビット線とを有し、複数のメモリセルは、スイッチング素子と、第1の電極及び第2の電極を有する容量素子と、をそれぞれ有し、複数のメモリセルの少なくとも1つにおいて、複数のワード線のうち一のワード線に与えられる電位に従って、スイッチング素子が複数のビット線のうち一のビット線と第1の電極の接続を制御し、なおかつ、第2の電極が複数のワード線のうち一のワード線とは異なる一のワード線に接続されている記憶装置。

(もっと読む)

ラッチ回路及び半導体装置

【課題】新規のラッチ回路を提供すること。

【解決手段】ラッチ回路は、酸化物半導体(OS)によってチャネル領域が形成されるトランジスタ10を有し、出力端子(Q端子)並びにトランジスタ10のソース及びドレインの一方に電気的に接続され、且つトランジスタ10がオフ状態となることによって浮遊状態となるノード11においてデータを保持する。なお、当該酸化物半導体は、シリコンよりもバンドギャップが広く、真性キャリア密度がシリコンよりも低い。このような酸化物半導体によってトランジスタのチャネル領域が形成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。

(もっと読む)

記憶装置

【課題】リフレッシュ動作の回数を減らすことで、消費電力を抑える。また、先に書き込んだデータを破壊することなく、データを読み出す。

【解決手段】ソースまたはドレインの一方となる第1の電極と、ソースまたはドレインの他方となる第2の電極と、第1のチャネル形成領域に絶縁膜を介して重畳して設けられた第1のゲート電極と、を有する第1のトランジスタと、ソースまたはドレインの一方となる第3の電極と、ソースまたはドレインの他方となる第4の電極と、第2のチャネル形成領域が第2のゲート電極と第3のゲート電極との間に絶縁膜を介して設けられた第2のトランジスタと、を有するメモリセルを複数有し、第1のチャネル形成領域及び第2のチャネル形成領域は、酸化物半導体を含んでおり、第2の電極は、第2のゲート電極に直接接続されている記憶装置とする。

(もっと読む)

信号処理回路

【課題】新たな構成の不揮発性の記憶回路を用いた信号処理回路を提供する。

【解決手段】演算部と、メモリと、演算部及びメモリを制御する制御部と、を有し、制御部は、揮発性の記憶回路と揮発性の記憶回路に保持されたデータを記憶するための第1の不揮発性の記憶回路との組を複数有し、メモリは、第2の不揮発性の記憶回路を複数有し、第1の不揮発性の記憶回路及び第2の不揮発性の記憶回路は、チャネルが酸化物半導体層に形成されるトランジスタと、トランジスタがオフ状態となることによってフローティングとなるノードに一対の電極のうちの一方が電気的に接続された容量素子とを有する。

(もっと読む)

1 - 20 / 92

[ Back to top ]