Fターム[5F102FB00]の内容

接合型電界効果トランジスタ (42,929) | 特殊動作 (121)

Fターム[5F102FB00]の下位に属するFターム

SIT (80)

バリスティック素子

負性抵抗素子 (2)

トンネル電流制御素子 (5)

主電流が電界以外に反応 (10)

その他の特殊動作 (22)

Fターム[5F102FB00]に分類される特許

1 - 2 / 2

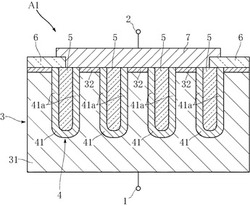

半導体装置およびその製造方法

【課題】流れる電流の大きさのバラツキを抑制するとともに、効率よく製造することが可能な半導体装置を提供すること。

【解決手段】アノード1およびカソード2と、アノード2に導通するドレイン領域およびカソード2に導通するソース領域を有するn型半導体層3と、カソード2に導通するゲート領域を有するp型半導体層4と、を備える定電流ダイオードA1であって、n型半導体層3には、その表面にカソード2が接続され、その裏面にアノード1が接続されており、p型半導体層4は、それぞれがn型半導体層3の表面から裏面に向かって延びる1対の壁部からなる複数の壁部対41aが、n型半導体層3の厚さ方向と直角である方向に配列された構成とされており、n型半導体層3の表面側部分のうち、複数の壁部対41aに挟まれた部分が、上記ソース領域となるn+型半導体層32とされている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

1 - 2 / 2

[ Back to top ]