Fターム[5F102GA02]の内容

接合型電界効果トランジスタ (42,929) | 集積化 (1,005) | FETとFET (424) | E/D型(エンハンスメント/ディプレッション型) (79)

Fターム[5F102GA02]に分類される特許

1 - 20 / 79

半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

ネスト化複合スイッチ

【課題】高いスイッチング速度及び低いオン状態抵抗を有し、電圧降伏耐性を強化したネスト化複合スイッチを提供する。

【解決手段】ネスト化複合スイッチ240は、複合スイッチに結合されたノーマリオン・プライマリ・トランジスタを含む。複合スイッチは、中間型トランジスタ222とカスコード接続された低電圧(LV)トランジスタ224を含み、中間型トランジスタは、LVトランジスタよりは大きく、ノーマリオン・プライマリ・トランジスタよりは小さい降伏電圧を有する。1つの実現では、ノーマリオン・プライマリ・トランジスタはIII-V族トランジスタとすることができ、LVトランジスタはIV族LVトランジスタとすることができる。

(もっと読む)

炭化珪素半導体装置

【課題】オン抵抗が低く高速動作が可能でありノーマリオフ特性を有し、かつ一の基板を用いて構成された炭化珪素半導体装置を提供する。

【解決手段】第1、第2、第4および第5不純物領域11、12、21、22は第1導電型を有し、第3不純物領域13は第2導電型を有する。第1〜第3不純物領域11〜13は第1導電型の第1層34に達する。第4および第5不純物領域21、22は第2層35上に設けられている。第1〜第5電極S1、D1、G1、S2、D2は第1〜第5不純物領域のそれぞれの上に設けられている。第1および第5電極S1、D2の間と、第3および第4電極G1、S2の間とは電気的に接続されている。第4および第5不純物領域21、22の間を覆うゲート絶縁膜I2上に第6電極G2が設けられている。

(もっと読む)

集積電力段

【課題】集積電力段において、入力電圧を集積電力段の一側面(例えば上面)で受け取り、出力電圧を集積電力段の反対側面(例えば底面)から出力する。

【解決手段】集積電力段は負荷段の上に位置する共通ダイを備え、共通ダイはドライバ段102及び電力スイッチ104を備える。電力スイッチは制御トランジスタ110及び同期トランジスタ112を含む。制御トランジスタのドレインD1が共通ダイの入力電圧を共通ダイの一側面(例えば上面)で受ける。制御トランジスタのソースS1が同期トランジスタのドレインD2に結合され、前記共通ダイの出力電圧を共通ダイの反対側面(例えば底面)で出力する。電力段の下にインターポーザ106を含めることができる。インターポーザは共通ダイの反対側面で共通ダイの出力電圧に結合される出力インダクタ118及び必要に応じ出力キャパシタ120を含む。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

アクティブ発振防止付き複合半導体デバイス

【課題】アクティブ発振防止付き複合半導体デバイスを提供する。

【解決手段】本明細書は、アクティブ発振制御付き複合半導体デバイスの種々の実現を開示する。1つの好適な実現では、ノーマリオフ複合半導体デバイスが、ノーマリオンIII-窒化物パワートランジスタ、及びこのノーマリオンIII-窒化物パワートランジスタとカスコード接続された低電圧(LV)デバイスを具えて、ノーマリオフ複合半導体デバイスを形成する。このLVデバイスは、例えば修正したボディ打込み領域により低減した出力抵抗、及び例えば修正した酸化物の厚さにより低減したトランスコンダクタンスの一方または両方を含むように構成されて、複合半導体デバイスのゲインを約10,000以下にすることができる。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

半導体装置、及び半導体装置の製造方法

【課題】BiFETデバイスに含まれるFETのオン抵抗の悪化を抑制する。

【解決手段】共通基板1上に第1SL10及び第2SL20積層体が順に形成された半導体装置であって、第2積層体が除去されて残存する第1積層体は、電界効果型トランジスタを構成し、第1積層体上に積層された第2積層体は、電界効果型トランジスタとは異なる素子(バイポーラトランジスタ)を構成し、電界効果型トランジスタを構成する第1積層体は、第1積層体に形成されるリセスの停止位置を規定し、かつInGaPから成るエッチング停止層10と、リセス内に配置されるゲート電極25の下方に配置され、かつAlGaAsから成る下部化合物半導体層8と、エッチング停止層10と下部化合物半導体層8との間に挿入され、エッチング停止層に含まれるリンが下部化合物半導体層まで熱拡散し、下部化合物半導体層を構成する元素と化合することを抑止するスペーサ層9とを含む。

(もっと読む)

電界効果トランジスタ

【課題】エンハンスメントモードトランジスタデバイスと、デプレッションモードトランジスタデバイスにおいて、エッチングストッパ層の選択エッチング性を改善し歩留り向上を図る。

【解決手段】チャネル層20の上に、エンハンスメントモードトランジスタデバイスの、InGaPエッチストップ/ショットキーコンタクト層が配置され、その上に、InGaPとは異なる第1の層26が配置され、第1の層の上に、デプレッションモードトランジスタデバイスエッチストップ層28が配置され、エッチストップ層の上に第2の層30が配置される。デプレッションモードトランジスタデバイスは、第2の層及びエッチストップ層を貫通し第1の層で終止するゲートリセスを有する。エンハンスメントモードトランジスタデバイスは、第2の層、デプレッションモードトランジスタデバイスエッチストップ層、第1の層を貫通しInGaP層で終止するゲートリセスを有する。

(もっと読む)

半導体装置

【課題】同一基板上にヘテロ接合バイポーラトランジスタ(HBT)と電界効果トランジスタ(FET)とが形成され、HBTのコレクタ抵抗が低減されてHBTの特性が向上され、かつFETのゲートリセスのエッチング精度が良好で、FETのオン抵抗が低い半導体装置を安定的に提供する。

【解決手段】HBT101Aにおいては、サブコレクタ層が複数の半導体層13〜15の積層構造からなり、かつ、サブコレクタ層においてコレクタ層17より張り出した部分上にコレクタ電極28が形成されている。FET101B、101Cにおいては、HBT101Aのサブコレクタ層をなす複数の半導体層のうち半導体基板1側の少なくとも1層の半導体層13が、キャップ層の少なくとも一部の層を兼ねている。HBTサブコレクタ層の総膜厚が500nm以上であり、FETキャップ層の総膜厚が50nm以上300nm以下である。

(もっと読む)

凹部バリア層を備えた高電子移動度トランジスタ

【課題】高電子移動度トランジスタ(HEMT)で、凹部バリア層を備え、バリア層間にゲート電極を形成することにより、エンハンスメント型FETを提供する。

【解決手段】基板上104上にバッファ108層を形成し、バッファ層上にスペーサ層112を形成し、スペーサ層上にバリア層116を形成する。バリア層内に凹部を形成し、凹部を通して、少なくてもその一部が前記スペーサ層上に配置されるようにゲート構造140を形成する。

(もっと読む)

窒化物半導体デバイス

【課題】 窒化物半導体デバイスを提供する。

【解決手段】 一実施形態では、デバイスはIII族窒化物チャネル層(3)とIII族窒化物チャネル層(3)上のIII族窒化物障壁層(4)とを含み、III族窒化物障壁層(4)は第1部分(4−1)と第2部分(4−2)とを含み、第1部分(4−1)は第2部分(4−2)より薄い厚さを有する。pドープIII族窒化物ゲート層部(5)は、III族窒化物障壁層(4)の少なくとも第1部分(4−1)上に配置され、ゲートコンタクト(10)はpドープIII族窒化物ゲート層部(5)上に形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート−ソース間およびゲート−ドレイン間のキャパシタンスの低減と、JFETをオンさせる際に必要なゲート印加電圧が高電圧になることを抑制する。

【解決手段】n-型チャネル層2の表面に直接p+型ゲート領域4を形成し、p+型ゲート領域4のうちn-型チャネル層2と接する部分と比較して、n-型チャネル層2から離れた部分が幅広となるようにする。そして、p+型ゲート領域4のうち幅広とされた部分がn-型チャネル層2から所定距離離れるようにする。例えば、n-型チャネル層2に凹部2aを形成し、この凹部2a内にp+型ゲート領域4を形成する。

(もっと読む)

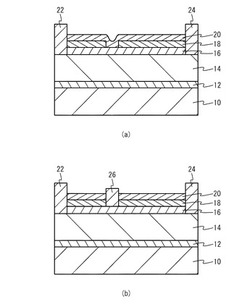

半導体装置およびその製造方法

【課題】DモードとEモードの素子を組み合わせた半導体装置およびその製造方法を提供する。

【解決手段】DモードとEモードのJFETにおけるチャネル領域を設定する場所にそれぞれ凹部2aと凸部2bを備えることで、同一基板上に厚みが異なるn型チャネル層3を形成する。そして、このような厚みが異なるn型チャネル層3によってDモードとEモードで作動するJFETを同一基板上に備えることができるため、SiCでもDモードとEモードのJFETを組み合わせたSiC半導体装置を実現することが可能となる。

(もっと読む)

半導体装置

【課題】低電圧時の電流が適度に大きく、高電圧時の電流が小さい半導体装置を提供する。

【解決手段】半導体装置100は、整流素子D1と、抵抗R1と、nチャネルディプリーショントランジスタDTと、アノード電極パッド7bとが直列接続された構成を有する半導体装置100であって、nチャネルディプリーショントランジスタDTのゲート電位を抵抗R1の両端の電位差により生成し、かつゲート電位によってnチャネルディプリーショントランジスタDTのチャネル91に空乏層Dを生じさせるよう構成されている。

(もっと読む)

高電圧耐久III族窒化物半導体デバイス

【課題】高電圧の印加時に、電荷キャリアを導電領域内に抑制して、高電圧耐久性を呈する、HEMTのようなIII族窒化物半導体デバイスを提供する。

【解決手段】高電圧耐久III族窒化物半導体デバイスは、(100)シリコン層14、該(100)シリコン層14上の絶縁体層18、及び該絶縁体層18上のP型導電性の(111)シリコン層16を有する支持基板を備える、高電子移動度トランジスタ(HEMT)を備える。高電圧耐久HEMTは、P型導電性の(111)シリコン層16上に形成したIII族窒化物半導体本体12であって、HEMTのヘテロ接合を形成する、III族窒化物半導体本体も備える。

(もっと読む)

半導体装置および電子機器

【課題】ノーマリーオフ動作を実現するとともに製造コストの増大を防ぐことが可能な半導体装置および電子機器を提供する。

【解決手段】半導体装置101は、第1の電界効果トランジスタF1の制御電極と第2電源ノードN2との間に接続され、第1の電界効果トランジスタF1の制御電極における電圧が所定値以上になると第1の電界効果トランジスタF1の制御電極から第2電源ノードN2への方向に導通するスイッチ素子ZDを備え、第1の電界効果トランジスタF1は、エピタキシャル成長用基板と、エピタキシャル成長用基板の主表面上に形成された半導体層とを含み、第1の電界効果トランジスタF1の第1導通電極、第2導通電極および制御電極は半導体層上に形成され、半導体層と電気的に接続され、第1の電界効果トランジスタF1の制御電極および半導体層によってショットキー接合が形成されている。

(もっと読む)

エンハンスメント型窒化ガリウム高電子移動度トランジスタ

実施形態には、これに限定されないが、第1バリア層と、該第1バリア層上の窒化ガリウムチャネル層と、該窒化ガリウムチャネル層上に存在し、第1サブレイヤーと第2サブレイヤーと第3サブレイヤーとを備える第2バリア層と、を有するヘテロ構造を備える装置とシステムが含まれる。該第1バリア層、第1サブレイヤーおよび第3サブレイヤーは各々アルミニウムを含んでいてもよい。他の実施形態も、本明細書に記載され特許請求される。 (もっと読む)

ワイドバンドギャップ半導体パワーJFETのための高温ゲートドライバ及びそれを含む集積回路

高い周囲温度環境において作動することが可能なワイドバンドギャップ(例えば、>2eV)半導体接合形電界効果トランジスタ(JFET)のためのゲートドライバについて記載される。ワイドバンドギャップ(WBG)半導体デバイスは、炭化ケイ素(SiC)及び窒化ガリウム(GaN)を含む。ドライバは、入力、出力、第1供給電圧を受け取るための第1基準線、第2供給電圧を受け取るための第2基準線、グランド端子、6つの接合形電界効果トランジスタ(JFET)を有する非反転ゲートドライバであり得、第1JFETおよび第2JFETは、第1反転バッファを形成し、第3JFETおよび第4JFETは、第2反転バッファを形成し、及び第5JFET及び第6JFETは、高温パワーSiC JFETを駆動させるために使用され得るトーテムポールを形成する。反転ゲートドライバも記載される。 (もっと読む)

半導体装置

【課題】高耐圧化及び高温動作を実現できる、HBTとFETを備える半導体装置を提供する。

【解決手段】本発明に係る半導体装置100は、基板101の上に順時積層されたn+型GaN層103及びn型GaN層104と、p型InGaN層105と、アンドープGaN層106及びn型AlGaN層107と、HBT領域121のn+型GaN層103と電気的に接続されたコレクタ電極114と、HBT領域121のp型InGaN層105と電気的に接続されたベース電極113と、HBT領域121のn型AlGaN層107と電気的に接続されたエミッタ電極112と、HFET領域120のn型AlGaN層107と電気的に接続されたソース電極109及びドレイン電極111と、n型AlGaN層107の上に形成されたゲート電極110とを備える。

(もっと読む)

1 - 20 / 79

[ Back to top ]