Fターム[5F102GC05]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | デュァルゲート、多ゲート (121)

Fターム[5F102GC05]に分類される特許

1 - 20 / 121

三次元配置部品を有する化合物半導体集積回路

半導体装置

【課題】ノーマリオフで動作するとともに、高い耐圧と低いオン抵抗を具備した半導体装置を提供すること。

【解決手段】 半導体装置1では、ドレイン電極21が第1ヘテロ接合面32に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ソース電極29が第1ヘテロ接合面32に形成される2次元電子ガス層から電気的に絶縁可能に構成されているとともに第2ヘテロ接合面34に形成される2次元電子ガス層に対して電気的に接続可能に構成されており、ゲート部28が第2ヘテロ接合面34に対向しており、導通電極25が第1ヘテロ接合面32及び第2ヘテロ接合面34に形成される2次元電子ガス層の双方に対して電気的に接続可能に構成されている。第1ヘテロ接合面32に形成される2次元電子ガス層の電子濃度は、第2ヘテロ接合面34に形成される2次元電子ガス層の電子濃度よりも濃い。

(もっと読む)

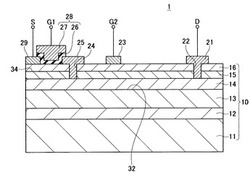

半導体装置

【課題】複数のチャネルを有する窒化物半導体装置において、ノーマリオフかつ低オン抵抗を実現する技術を提供する。

【解決手段】第1の窒化物半導体層3,5,7と、第1の窒化物半導体層よりも禁制帯幅が大きい第2の窒化物半導体層5,6,8とが積層されたヘテロ接合体を少なくとも2つ以上有する窒化物半導体積層体10を備え、窒化物半導体積層体10に設けられたドレイン電極14と、ソース電極13と、ドレイン電極14とソース電極13の両者に対向して設けられたゲート電極15,16とを有し、ドレイン電極14とソース電極13は、窒化物半導体積層体10の表面または側面に配置され、ゲート電極15,16は、窒化物半導体積層体10の深さ方向に設けられた第1ゲート電極15と、該第1ゲート電極15と窒化物半導体積層体10の深さ方向の配置深さが異なる第2ゲート電極16とを有する。

(もっと読む)

窒化物半導体装置

【課題】櫛型形状のソース電極とドレイン電極が交差指状に配置された電極構造を有し、各櫛形電極の先端部での電界集中が緩和された窒化物半導体装置を提供する。

【解決手段】ゲート電極5と電気的に接続され、ゲート電極5とドレイン電極4間で絶縁膜7上に配置されたゲートフィールドプレート50と、ソース電極3と電気的に接続され、絶縁膜8を介して窒化物半導体層と対向するようにゲートフィールドプレート50とドレイン電極4間の上方に配置されたソースフィールドプレート30とを備え、ゲート電極5とドレイン電極4間の距離、ゲートフィールドプレート50のドレイン側端部とゲート電極5のドレイン側端部間の距離、及びソースフィールドプレート30のドレイン側端部とゲートフィールドプレート50のドレイン側端部間の距離の少なくともいずれかが、ソース電極3とドレイン電極4の、歯部分の直線領域よりも歯部分の先端領域において長い。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

窒化物半導体装置

【課題】内蔵する環流ダイオードの順方向電圧が低く、高耐圧で、低オン抵抗の、ノーマリオフ型の窒化物半導体装置を提供する。

【解決手段】窒化物半導体装置は、基板1、第1の窒化物半導体層3、第2の窒化物半導体層4、及び第2の窒化物半導体層上4に設けられた、ソース電極5、ドレイン電極6、第1のゲート電極9、ショットキー電極10、第2のゲート電極12、を備える。第2の窒化物半導体層4と第1の窒化物半導体層3との界面には、2次元電子ガスが形成される。第1のゲート電極9はノーマリオフ型FET20のゲート電極であり、ソース電極5とドレイン電極6との間に設けられる。ショットキー電極10は、第1のゲート電極9とドレイン電極6との間に設けられる。第2のゲート電極12はノーマリオン型FET21のゲート電極であり、ショットキー電極10とドレイン電極6との間に設けられる。

(もっと読む)

ワイドバンドギャップ半導体デバイス

【課題】製造が容易であり、デバイス特性の変動を抑制できるワイドバンドギャップ半導体デバイスを得る。

【解決手段】SiC基板1上にAlN格子緩和層2、GaNチャネル層3、及びAlGaN電子供給層4が順に設けられている。これらは、1.42eVより広いバンドギャップを持つ半導体材料からなる。AlGaN電子供給層4に、トランジスタを含む活性領域9が設けられている。SiC基板1は、光学的な不純物又は格子欠陥により着色され、可視光領域の光を吸収する。従って、このデバイスは波長360nm〜830nmの可視光領域の光に対して不透明である。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】高濃度接合リークが発生することを抑制する。

【解決手段】第2ゲート領域8が備えられるトレンチ6の先端部においてJFET構造が形成されないように凹部13を形成する構造において、凹部13の底面と側面との境界部となるコーナ部にp型層16を形成するようにする。これにより、p型層16とp+型の第1ゲート領域3もしくは第2ゲート領域8とが同じ導電型となり、これらの間において高濃度接合が構成されないようにできる。したがって、ドレイン電位が第1ゲート領域3上に表出して、ゲート−ドレイン間耐圧を低下させてしまうことを防止でき、高濃度接合リーク(ゲートリークやドレインリーク)が発生することを防止することができる。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

窒化物半導体装置

【課題】ダイオード等の保護素子の外付けによる部品点数の増加及び占有面積の増大を抑えた、双方向に高いアバランシュエネルギー耐量を有する窒化物半導体装置を提供する。

【解決手段】半導体基板10は、第1のn型領域12A、第2のn型領域12Bとともにトランジスタ11を構成する。半導体基板10の裏面には、裏面電極13が接合され、また、半導体基板10の上には、HFET21が形成されている。HFET21は、AlGaN層23A及びGaN層23Bを備える半導体層積層体23と、第1のオーミック電極24A、第2のオーミック電極24B、第1のゲート電極25A、第2のゲート電極25Bにより構成されている。第1のオーミック電極24Aと第1のn型領域12A、第2のオーミック電極24Bと第2のn型領域12Bはそれぞれ電気的に接続されている。

(もっと読む)

スイッチ装置

【課題】スイッチ素子のオン抵抗をより一層小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ素子10は、半導体基板104に絶縁膜15を介して接合された電界印加電極14を有している。駆動回路20の電界制御部22は、スイッチ素子10の電界印加電極14およびソース電極13に接続されており、電界印加電極14−ソース電極13間にバイアス電圧Veを印加する。電界制御部22は、閾値を超えるバイアス電圧Veをスイッチ素子10に印加することによって、電界印加電極14から半導体基板104のヘテロ接合界面に電界を印加する。要するに、スイッチ素子10がオン状態で、電界印加電極14から半導体基板104に印加される電界は、電界効果によってチャネル領域の電子濃度を高くし、スイッチ素子10のオン抵抗を小さくするように作用する。

(もっと読む)

スイッチ装置

【課題】スイッチ素子のオン抵抗をより一層小さく抑えることができるスイッチ装置を提供する。

【解決手段】スイッチ素子10は、半導体基板104に直接接合された注入用電極14を具備するホール注入部140を有している。駆動回路20の注入駆動部22は、スイッチ素子10の注入用電極14およびソース電極13に接続されており、注入用電極14−ソース電極13間に注入電圧Vinを印加する。注入駆動部22は、閾値を超える注入電圧Vinをスイッチ素子10に印加することによって、ホール注入部140から半導体基板104のヘテロ接合界面にホールを注入する。注入されたホールは、ヘテロ接合界面に同量の電子を引き寄せるので、チャネル領域として2次元電子ガスの濃度が高くなり、スイッチ素子10のオン抵抗は小さくなる。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】チャネルとなるナノワイアの周囲をゲート電極が取り巻いて形成されているFETが、より容易に高い精度で製造できるようにする。

【解決手段】被覆ナノワイア103を配置した基板121のゲート電極形成領域の上に、被覆ナノワイア103に交差して下部ゲート電極122に重なる上部ゲート電極124を形成する。上部ゲート電極124の形成は、公知のリソグラフィー技術とリフトオフとにより行えばよい。例えば、被覆ナノワイア103が下部ゲート電極122と交差して配置されている基板121の上に、電子ビーム露光により電極形成部に開口を備えるレジストパターンを形成し、この上に、電極材料を堆積する。この後、先に形成してあるレジストパターンを除去すれば、上部ゲート電極124が形成できる。

(もっと読む)

電動機駆動装置

【課題】装置全体としての長寿命化を図りつつ、装置全体としての小型化を可能とする電動機駆動装置を提供する。

【解決手段】駆動部12は、横型半導体素子からなる1回路2接点式の切替素子16,17を2つ有している。第1の切替素子16は、コモン端子160を電動機11に接続し、第1の端子161および第2の端子162を電源部15に接続する。第2の切替素子17は、コモン端子170を電動機11に接続し、第1の端子171および第2の端子172を電源部15に接続する。制御部14は、各切替素子16,17において、コモン端子160,170が、第1の端子161,171および第2の端子162,172に対して択一的に接続されるように、各切替素子16,17を個別に切替制御する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】オン抵抗が低く、かつ、耐圧が高いノーマリーオフの半導体装置を提供する。

【解決手段】基板102の上方に形成された、III−V族化合物半導体からなるバックバリア層106と、バックバリア層106上に形成され、バックバリア層よりバンドギャップエネルギーが小さいIII−V族化合物半導体からなるチャネル層と108、チャネル層108にオーミック接続された第1の電極116,118と、チャネル層の上方に形成された第2の電極120と、を備え、バックバリア層106は第2の電極120の下方に設けられ、かつ、第2の電極120の下方から第1の電極の116,118下方まで連続して設けられていない半導体装置を提供する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

1 - 20 / 121

[ Back to top ]