Fターム[5F102GC09]の内容

接合型電界効果トランジスタ (42,929) | ゲート配置 (2,808) | 縦型FETの切込みゲート (58)

Fターム[5F102GC09]に分類される特許

1 - 20 / 58

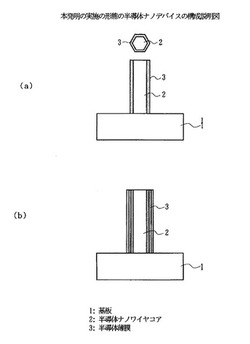

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

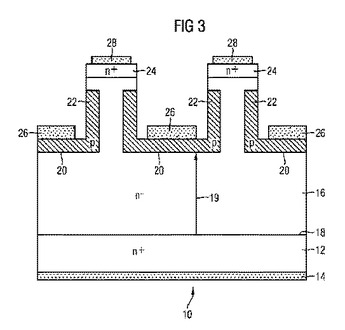

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

非晶質酸化物を利用した半導体デバイス

【課題】透明酸化物膜を用いた半導体デバイスや回路を提供する。

【解決手段】電子キャリア濃度が1015/cm3以上、1018/cm3未満である、In―Zn―Ga酸化物、In―Zn―Ga―Mg酸化物、In―Zn酸化物、In―Sn酸化物、Sn−In−Zn酸化物、In酸化物、Zn―Ga酸化物、及びIn―Ga酸化物のうちのいずれかである非晶質酸化物を、N型半導体として用いたN型TFTを含む回路を構成要素としており、前記N型TFTは、ゲート電圧無印加時のソース−ドレイン端子間の電流が10マイクロアンペア未満であり、電界効果移動度が1cm2/(V・秒)超であることを特徴とする集積回路。

(もっと読む)

ワイドバンドギャップ半導体における常時オフ集積JFET電源スイッチおよび作成方法

【課題】常時オフVJFET集積電源スイッチを含むワイドバンドギャップ半導体デバイスの提供。

【解決手段】電源スイッチは、モノリシックまたはハイブリッドに実装され得、シングルまたはマルチチップのワイドバンドギャップ電源半導体モジュールにビルトインされた制御回路と一体化され得る。該デバイスは、高電力で温度に対する許容性があり、耐放熱性のエレクトロニクスコンポーネントにおいて用いられ得る。該デバイスを作成する方法もまた、記述される。

(もっと読む)

パワー半導体素子

【課題】窒化物化合物半導体を用いたパワーダイオード、パワーMOSFET等のパワー

半導体素子について、クラックフリーで形成されて従来よりも厚い窒化物化合物半導体層

を使用して耐圧を向上することである。

【解決手段】シリコン基板1上に厚さ10μm以上の凸状に選択成長された窒化物化合物

半導体からなるキャリア移動層3と、キャリア移動層3上に形成された電極4とを有し、

1つのパワー半導体素子は1つのキャリア移動層3から構成されている。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

III族窒化物半導体装置

【課題】p型III族窒化物半導体62の上面からn型III族窒化物半導体64に到達する溝が形成されている場合、p型III族窒化物半導体の側面62aが露出する。p型III族窒化物半導体の露出面62aはn型化しやすく、露出面に沿ってリーク電流が流れやすい。

【解決手段】p型III族窒化物半導体62中に存在する正孔を露出面62aに誘導する正孔誘導手段を設ける。例えば、露出面62aを被覆する絶縁膜66に負電荷蓄積領域68を設ける。負電荷蓄積領域68が、p型III族窒化物半導体中に存在する正孔を露出面62aに誘導し、露出面がn型化して露出面に沿ってリーク電流が流れることを防止する。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】チャネル層のキャリア濃度が増大することを避けてリークを低減できる構造を有する、窒化物電子デバイスを提供する。

【解決手段】半導体積層15の斜面15a及び主面15cは、それぞれ、第1及び第2の基準面R1、R2に対して延在する。半導体積層15の主面15cは六方晶系III族窒化物のc軸方向を示す基準軸Cxに対して5度以上40度以下の範囲内の角度で傾斜すると共に、第1の基準面R1の法線と基準軸Cxとの成す角度は第2の基準面R2の法線と基準軸Cxとの成す角度より小さいので、チャネル層19の酸素濃度を1×1017cm−3未満にすることができる。これ故に、チャネル層19において、酸素添加によりキャリア濃度が増加することを避けることができ、チャネル層を介したトランジスタのリーク電流を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】炭化珪素基板を用いた接合型FETにおいて、ゲート・ソース間のpn接合領域において生じるリーク電流を低減する。

【解決手段】炭化珪素基板を用いたトレンチ型接合FETにおいて、トレンチ5の側壁および底面に窒素を導入することにより、トレンチ5の表面にn型層8およびn+型層9を形成する。これによりp+型ゲート領域4とn+型ソース領域3との接合領域であるpn接合領域はダメージの多いトレンチ5の側壁ではなく半導体基板21の主面において露出し、また、その露出する領域は狭まるため、pn接合領域におけるリーク電流を低減することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 サージ電圧等に対するバイパス用の保護部を備え、耐圧性能および低いオン抵抗(低いオン電圧)を実現し、かつ、構造が簡単な、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】 支持基体上にオーミック接触するGaN層を有するn+型GaN基板1と、第1領域R1上におけるn−型GaNドリフト層2を有するFETと、第2領域R2においてn−型GaNドリフト層2にショットキー接触するアノード電極を有するSBDとを備え、FETとSBDとは並列配置されており、n+型GaN基板1の裏面に、FETのドレイン電極DおよびSBDのカソード電極Cを備えることを特徴とする。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部の周辺を含めてn+型SiC基板1の外縁部においてn+型ソース領域4が除去されると共に、トレンチ6の先端部においてn-型チャネル層7および第2ゲート領域8が除去された凹形状とする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

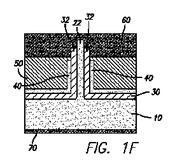

打込みされた側壁を有する半導体デバイスを製造する方法およびそれによって製造されたデバイス

半導体デバイスおよびそのデバイスを製造する方法が提供される。デバイスは、接合型電界効果トランジスタ(JFET)、または接合型バリアショットキー(JBS)ダイオードまたはPiNダイオードのようなダイオードであり得る。デバイスは、打込みマスクを用いる選択的イオン注入を使用して製造される。デバイスは、打込みマスクからの通常の入射イオンの散乱によって形成された打込み側壁を有する。長いチャネル長の縦型接合型電界効果トランジスタが記載される。デバイスは、シリコンカーバイド(SiC)のようなワイドバンドギャップ半導体材料から製造されることができ、高温および高出力の用途において使用することができる。 (もっと読む)

半導体装置およびその製造方法

【課題】オン抵抗を低く、移動度を高く、かつピンチオフ特性を良好にした上で、ドレイン電圧を増大させてもキンク現象が生じない、大電流用の、半導体装置およびその製造方法を提供する。

【解決手段】開口部28が設けられたGaN系積層体15と、チャネルを含む再成長層27と、ゲート電極Gと、ソース電極Sと、ドレイン電極Dとを備え、再成長層27は電子走行層22および電子供給層26を含み、GaN系積層体には再成長層に開口部でその端面が被覆されるp型GaN層6が含まれ、そのp型GaN層にオーミック接触するp部電極11を備えることを特徴とする。

(もっと読む)

単極半導体部品と半導体装置の製造方法

本発明は、ドリフト層(16)を有する単極半導体部品の製造方法であって、少なくとも1つの広いバンドギャップ材料を含むドリフト層(16)の材料のエピタキシャル析出を手段として、ドリフト層(16)の成長方向(19)に沿って連続的に低下する電荷キャリアドーピング(n)の濃度を有するドリフト層(16)を形成する工程を含む方法に関する。エピタキシャル析出により形成されるドリフト層(16)に炭化ケイ素を使用することにより、下流工程におけるドープ材原子の拡散による電荷キャリアドーピング(n)の連続的に低下する濃度のその後の変化を抑制する。製造方法は特に、単純なおよび/または費用効果的なやり方で、ドリフト層(16)を含む単極半導体部品であって比較的低い順方向損失と比較的高い逆バイアス電圧との有利な比を有する単極半導体部品を実装するために使用されることができる。単極半導体部品は能動半導体部品または受動半導体部品であることができる。本発明はさらに、半導体装置(10)に関する。  (もっと読む)

(もっと読む)

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られるデバイス

パッシベートされたシリコンナノワイヤーの製造方法およびこれにより得られる電子構造体について記載する。こうした構造体は、金属−酸化物−半導体(MOS)構造を含むことができ、構造体はMOS電界効果トランジスタ(MOSFET)または光電子スイッチに用いることができる。  (もっと読む)

(もっと読む)

イオン注入せずに縦型接合形電界効果トランジスタおよびバイポーラ接合トランジスタを製造する方法およびそれによって製造されたデバイス

縦型接合形電界効果トランジスタ(VJFET)またはバイポーラ接合トランジスタ(BJT)のような半導体デバイスを製造する方法が記載される。その方法はイオン注入を必要としない。VJFETデバイスは、エピタキシャル成長した埋め込みゲート層のみでなく、エピタキシャル再成長したn型チャネル層及びエピタキシャル再成長したp型ゲート層も有する。その方法で製造されたデバイスも記載される。 (もっと読む)

1 - 20 / 58

[ Back to top ]