Fターム[5F102GD00]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160)

Fターム[5F102GD00]の下位に属するFターム

MES型(ショットキ・ゲート型) (1,993)

pn接合型 (421)

その他(MOS、擬似MIS) (744)

Fターム[5F102GD00]に分類される特許

1 - 2 / 2

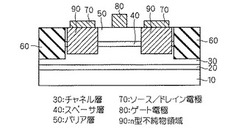

ヘテロ接合電界効果型トランジスタおよびその製造方法

【課題】ソース/ドレイン電極の下側のポテンシャル障壁を低くして、ソース/ドレイン電極下側の寄生抵抗を低減することを目的とする。

【解決手段】本発明に係るヘテロ接合電界効果型トランジスタは、窒化物半導体からなるヘテロ接合電界効果型トランジスタであって、チャネル層30と、チャネル層30上にスペーサ層40を介して形成されたバリア層50とを備える。バリア層50上に形成されたゲート電極80と、バリア層50上に、ゲート電極80を挟んで形成されるソース/ドレイン電極70とを備える。そして、ソース/ドレイン電極70下側の少なくとも一部の領域、例えば、バリア層50、スペーサ層40、チャネル層30のに形成されるn型不純物領域90を備える。

(もっと読む)

化合物半導体デバイス用基板およびそれを用いた化合物半導体デバイス

【課題】窒化物半導体単結晶膜を有する化合物半導体デバイスにおいて、高耐圧かつ低損失であり、HEMT等に好適に用いられる化合物半導体デバイス用基板およびそれを用いた化合物半導体デバイスを提供する。

【解決手段】導電性SiC単結晶2上に、厚さ3〜250nmのAlxGa1-xN単結晶層(0<x≦1)3aおよび厚さ3〜250nmのAlyGa1-yN単結晶層(0≦y<1、x≠y)3bが交互に5〜500組繰り返し積層されている多層単結晶層3と、厚さ0.5〜5μmのGaN単結晶層4と、デバイス活性層5とを順次積層した化合物半導体デバイス用基板に、ショットキー電極およびオーミック電極6を形成する。

(もっと読む)

1 - 2 / 2

[ Back to top ]