Fターム[5F102GD04]の内容

接合型電界効果トランジスタ (42,929) | ゲート接合のタイプ (3,160) | pn接合型 (421)

Fターム[5F102GD04]の下位に属するFターム

ヘテロゲート (33)

Fターム[5F102GD04]に分類される特許

1 - 20 / 388

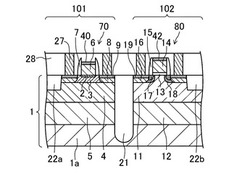

炭化珪素半導体装置およびその製造方法

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】ノーマリーオフ特性を具現すると共にゲートリーク電流を抑制する窒化物半導体素子及びその製造方法を提供する。

【解決手段】第1の窒化物層31とその材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、その上にオミック接触されたソース電極50と、これから離間して窒化物半導体30層上にオミック接触されたドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に、これらから離間して形成されたP型窒化物層40と、この上に形成されたN型窒化物層140と、ソース側の側壁が、P型窒化物層40及びN型窒化物層140のソース側の側壁と整列するようにN型窒化物層140上に接触させたゲート電極70とを含む。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート領域近傍のチャネル部分の抵抗を低減することにより、従来よりも特性オン抵抗が低い炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを有している。炭化珪素層4は、チャネル層13と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、厚さ方向に沿って主表面13Aからチャネル層13中に突き出るように延びるゲート領域16とを含んでいる。ゲート領域16の対向方向に沿った寸法は、主表面13Aから離れるにつれて小さくなっている。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】耐圧を高めた窒化物半導体素子及び製造方法を提供する。

【解決手段】第1の窒化物層31と該第1の窒化物層31の材料より広いエネルギバンドギャップを有する材料を含む第2の窒化物層33とが異種接合され、該接合界面寄りに2次元電子ガス(2DEG)チャネルが形成された窒化物半導体層30と、窒化物半導体層30上にオーミック接触されるソース電極50とドレイン電極60と、ソース電極50とドレイン電極60との間の窒化物半導体層30上に形成され、ソース電極50から所定距離だけ離間された第1の側壁からドレイン側へ長く形成された多数のP型窒化物半導体セグメント80と、ソース電極50とドレイン電極60との間でソース電極50に近く形成され、多数のP型窒化物半導体セグメント80間の窒化物半導体層30上及びP型窒化物半導体セグメント80上に接触されるゲート電極70とを含む。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ノーマリオフ動作を実現しながら良好な伝導性能を得ることができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、電子供給層5とゲート電極11gとの間に形成されたp型半導体層8と、電子供給層5とp型半導体層8との間に形成され、電子供給層5よりもバンドギャップが大きい正孔障壁層6と、が設けられている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体層と電極との間に絶縁膜を介するMIS構造を採用するも、オン抵抗の上昇及び閾値の変動を抑止し、信頼性の高い半導体装置を得る。

【解決手段】AlGaN/GaN・HEMTは、化合物半導体積層構造2と、化合物半導体積層構造2の表面と接触する挿入金属層4と、挿入金属層4上に形成されたゲート絶縁膜7と、挿入金属層4の上方でゲート絶縁膜7を介して形成されたゲート電極8とを含み構成される。

(もっと読む)

スイッチング素子

【課題】逆ピエゾ効果が効果的に抑制され、オフ時の高電界状態であっても、ゲート電極近傍でクラックの発生が抑止されたスイッチング素子を提供する。

【解決手段】スイッチング素子1は、電子走行層13と、電子走行層13の上面に形成され、バンドギャップが電子走行層13より大きく電子走行層13とヘテロ接合する電子供給層14と、ソース電極15とドレイン電極16と、ソース電極15とドレイン電極16の間に配置されたゲート電極17とを備え、ゲート電極の下方に、電子供給層14に替えて、逆ピエゾ抑制層20を配置してなる。逆ピエゾ抑制層20は、ヘテロ接合よりも格子不整合が緩和された状態で電子走行層13と接合するように、その組成等が調整されており、ゲート電極17との接触領域A2のドレイン電極16側境界B4を跨ぐように配置される。

(もっと読む)

窒化ガリウム結晶、ホモエピタキシャル窒化ガリウムを基材とするデバイス、及びその製造方法

【課題】ホモエピタキシャルLED、LD、光検出器又は電子デバイスを形成するために役立つGaN基板の形成方法の提供。

【解決手段】約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板上に配設された1以上のエピタキシャル半導体層を含むデバイス。かかる電子デバイスは、発光ダイオード(LED)及びレーザーダイオード(LD)用途のような照明用途、並びにGaNを基材とするトランジスター、整流器、サイリスター及びカスコードスイッチなどのデバイスの形態を有し得る。また、約104/cm2未満の転位密度を有し、傾角粒界が実質的に存在せず、酸素不純物レベルが1019cm−3未満の窒化ガリウムからなる単結晶基板を形成し、該基板上に1以上の半導体層をホモエピタキシャルに形成する方法及び電子デバイス。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

高速回復整流器構造体の装置および方法

【課題】高速回復整流器構造体の装置および方法を提供する。

【解決手段】具体的には構造体は第1のドーパントの基板(120)を含む。第1のドーパントが低濃度ドープされた第1のエピタキシャル層(140)が基板に結合されている。第1の金属層(190)が第1のエピタキシャル層に結合されている。複数のトレンチ(175)が第1のエピタキシャル層内に窪んでおり、その各々が金属層と結合している。装置は各々第2のドーパント型がドープされた複数のウェルも含み、各ウェルは対応するトレンチの下に且つ隣接して形成されている。複数の酸化物層(170)が対応するトレンチの壁および底部上に形成されている。第1のドーパントがドープされた複数のチャネル領域が、2つの対応するウェル間の第1のエピタキシャル層内に形成されている。複数のチャネル領域(150)の各々は第1のエピタキシャル層より高濃度に第1のドーパントがドープされている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】多様な構造を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1の上方に形成された化合物半導体層2と、が設けられている。化合物半導体層2には、第1の不純物の活性化により発生した第1導電型のキャリアを含む第1の領域2aと、第1の不純物と同一種類の第2の不純物の活性化により発生したキャリアを、第1の領域2aよりも低濃度で含有する第2の領域2bと、が設けられている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】高濃度接合リークが発生することを抑制する。

【解決手段】第2ゲート領域8が備えられるトレンチ6の先端部においてJFET構造が形成されないように凹部13を形成する構造において、凹部13の底面と側面との境界部となるコーナ部にp型層16を形成するようにする。これにより、p型層16とp+型の第1ゲート領域3もしくは第2ゲート領域8とが同じ導電型となり、これらの間において高濃度接合が構成されないようにできる。したがって、ドレイン電位が第1ゲート領域3上に表出して、ゲート−ドレイン間耐圧を低下させてしまうことを防止でき、高濃度接合リーク(ゲートリークやドレインリーク)が発生することを防止することができる。

(もっと読む)

窒化物系半導体装置

【課題】ダイオード部とトランジスタ部の面積比率を自由に設定することが可能な窒化物系半導体装置を提供することを目的とする。

【解決手段】第1HEMT部30及び第2HEMT部31から成るトランジスタ部1と、第1電極24と電気的に短絡された第1ショットキー電極28及び第1ゲート電極26と電気的に第2ショットキー電極29から成るダイオード部2と、を備えて構成されている。また、第1電極24と第2電極25との間の領域に第1電極24に沿って、第1ゲート電極26及び第1ショットキー電極28が交互に形成され、かつ、第2電極25に沿って、第2ゲート電極27及び第2ショットキー電極29が交互に形成されている。さらに、第1ゲート電極26と第2ゲート電極27とは、対向して形成されており、第1ショットキー電極28と第2ショットキー電極29とは対向して形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

炭化珪素半導体装置

【課題】オン抵抗が低く高速動作が可能でありノーマリオフ特性を有し、かつ一の基板を用いて構成された炭化珪素半導体装置を提供する。

【解決手段】第1、第2、第4および第5不純物領域11、12、21、22は第1導電型を有し、第3不純物領域13は第2導電型を有する。第1〜第3不純物領域11〜13は第1導電型の第1層34に達する。第4および第5不純物領域21、22は第2層35上に設けられている。第1〜第5電極S1、D1、G1、S2、D2は第1〜第5不純物領域のそれぞれの上に設けられている。第1および第5電極S1、D2の間と、第3および第4電極G1、S2の間とは電気的に接続されている。第4および第5不純物領域21、22の間を覆うゲート絶縁膜I2上に第6電極G2が設けられている。

(もっと読む)

1 - 20 / 388

[ Back to top ]