Fターム[5F102GK00]の内容

接合型電界効果トランジスタ (42,929) | バッファ層(中間層) (2,318)

Fターム[5F102GK00]の下位に属するFターム

単一半導体層 (1,628)

多層構造(起格子を含む) (565)

格子定数のずれ、格子歪の利用 (111)

半導体以外の材料 (8)

Fターム[5F102GK00]に分類される特許

1 - 6 / 6

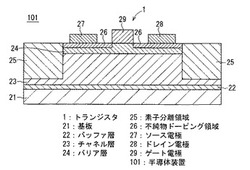

半導体装置およびその製造方法

【課題】ゲート電極に臨む領域の半導体層へのダメージ層の形成を抑制して、ノーマリオフ動作を実現することができるヘテロ接合電界効果型トランジスタを備える半導体装置およびその製造方法を提供する。

【解決手段】チャネル層23とヘテロ接合を形成するバリア層24のうち、ゲート電極29に臨む領域を除く他の領域に、バリア層24の伝導帯から、チャネル層23とバリア層24とのヘテロ界面のバンド不連続量ΔEcと、バリア層24に発生する分極によるバリア層24のゲート電極29側とヘテロ界面側とのエネルギー差ΔEpとを足し合わせたエネルギー(ΔEc+ΔEp)までのエネルギー深さのバンドギャップ中に準位を形成する不純物をドーピングして、不純物ドーピング領域26を形成する。

(もっと読む)

ZnOデバイス

【課題】 ZnOトランジスタ又はHEMTのようなZnOデバイスにおいて、ソース・ドレインのコンタクト抵抗を減少させることを課題とする。

【解決手段】 Zn極性面を有するアンドープZnO層をチャンネル層とし、該Zn極性面を有するZnO層上には、極性面反転層を介して、ソース・ドレインに接続されたO極性高濃度n型ZnO層が、選択的に形成されていることを特徴とするZnOデバイスである。

(もっと読む)

III−V族化合物半導体装置及びその製造方法

【課題】バッファリーク電流を十分に抑制可能なIII−V族化合物半導体装置及びその製

造方法を提供する。

【解決手段】単結晶基板(11)とチャネル層(13)との間に無添加バッファ層(12)を含むIII

−V族化合物半導体装置(1)において、前記単結晶基板(11)と前記無添加バッファ層(12)

の界面に、前記無添加バッファ層(12)の前記単結晶基板(11)側の界面に、又は前記無添加バッファ層(12)中に、酸素δドーピング層(12a)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】GaN系半導体層とSiC基板との接触抵抗を小さくすること、および高耐圧化すること。

【解決手段】本発明は、3C−SiCからなる基板(10)と、基板(10)上に設けられたGaN系半導体層(18)と、GaN系半導体層(18)上に設けられた第1電極(24)と、基板(10)に設けられた第2電極(28)と、第1電極(24)と第2電極(28)との間に流れる電流を制御する制御電極(26)と、を具備することを特徴とする半導体装置半導体装置およびその製造方法である。

(もっと読む)

半導体素子

【課題】電流コラプスを悪化させることなくバッファ層を高抵抗化し、バッファ層中に発生するリーク電流を低減させること。

【解決手段】HEMT1は、基板2上に、それぞれGaN系化合物半導体からなる低温バッファ層3、バッファ層4、電子走行層5および電子供給層6を、この順に積層して備える。バッファ層4は、炭素が添加され、この添加される炭素濃度は、この炭素濃度に対して電流コラプスが急激に変化する濃度以下であり、かつこの炭素濃度に対してHEMT1の耐圧が急激に変化する濃度以上とされる。また、電子走行層5の層厚は、この層厚に対して電流コラプスが急激に変化する厚さ以上であり、かつこの層厚に対してHEMT1の耐圧が急激に変化する厚さ以下とされる。

(もっと読む)

エピタキシャル基板およびそれを用いた半導体装置並びにその製造方法

【課題】窒化物系レーザダイオードの低閾値化、窒化物系半導体発光ダイオードの高効率化、エンハンスメント型窒化物系半導体電界効果トランジスタの実現のためには、R面サファイア基板上に成長すれば可能であるが、従来技術では、表面平坦性や多数の欠陥が入る問題があり、また、その結晶性を向上させる方法として、選択横方向成長という方法があるが、コスト、量産性の面で大きな問題があった。

【解決手段】R面サファイア基板上に作製した窒化物系半導体に、歪を導入することおよび成長条件を最適化することによって、結晶成長中に自発的に周期10nmから10μm、高さ10nmから10μmの凹凸を形成し、その後平坦化することにより貫通転位密度、積層欠陥密度の低減が可能であり、且つ、表面平坦性の良好な半導体基板の作製が低コストかつ簡便に作製可能であり、また、この基板を用いること。

(もっと読む)

1 - 6 / 6

[ Back to top ]