Fターム[5F102GL02]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 単一半導体層 (2,547) | 4族 (280)

Fターム[5F102GL02]の下位に属するFターム

Si (112)

Fターム[5F102GL02]に分類される特許

1 - 20 / 168

炭化珪素半導体装置およびその製造方法

炭化珪素半導体装置およびその製造方法

【課題】ゲート領域近傍のチャネル部分の抵抗を低減することにより、従来よりも特性オン抵抗が低い炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを有している。炭化珪素層4は、チャネル層13と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、厚さ方向に沿って主表面13Aからチャネル層13中に突き出るように延びるゲート領域16とを含んでいる。ゲート領域16の対向方向に沿った寸法は、主表面13Aから離れるにつれて小さくなっている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

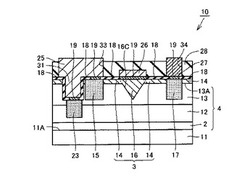

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】高濃度接合リークが発生することを抑制する。

【解決手段】第2ゲート領域8が備えられるトレンチ6の先端部においてJFET構造が形成されないように凹部13を形成する構造において、凹部13の底面と側面との境界部となるコーナ部にp型層16を形成するようにする。これにより、p型層16とp+型の第1ゲート領域3もしくは第2ゲート領域8とが同じ導電型となり、これらの間において高濃度接合が構成されないようにできる。したがって、ドレイン電位が第1ゲート領域3上に表出して、ゲート−ドレイン間耐圧を低下させてしまうことを防止でき、高濃度接合リーク(ゲートリークやドレインリーク)が発生することを防止することができる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

低マイクロパイプの100mm炭化ケイ素ウェハ

【課題】種結晶を用いた昇華システムにおいて形成された結晶の欠陥レベルが低く、より大きく、高品質のSiC単結晶ウェハを製造する方法を提供する。

【解決手段】少なくとも約100mmの直径と、約25cm−2未満のマイクロパイプ密度とを有し、また、3C、4H、6H、2Hおよび15Rポリタイプからなる群から選択されるポリタイプを有するSiC単結晶ウェハ。なお、マイクロパイプ密度は、表面上にある全マイクロパイプの総数を、ウェハの表面積で割ったものを表す。

(もっと読む)

半導体デバイス、半導体基板、半導体基板の製造方法および半導体デバイスの製造方法

【課題】単一基板上にソース・ドレインを同一工程で同時形成したIII−V族半導体のnMISFETおよびIV族半導体のpMISFETのソース・ドレイン領域抵抗または接触抵抗を小さくする。

【解決手段】第1半導体結晶層104に形成された第1チャネル型の第1MISFET120の第1ソース124および第1ドレイン126が、第1半導体結晶層104を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、またはニッケル原子とコバルト原子との化合物からなり、第2半導体結晶層106に形成された第2チャネル型の第2MISFET130の第2ソース134および第2ドレイン136が、第2半導体結晶層106を構成する原子と、ニッケル原子との化合物、または、コバルト原子との化合物、または、ニッケル原子とコバルト原子との化合物からなる。

(もっと読む)

半導体装置の製造方法

【課題】設計の自由度を損なわずに、高いオン特性とオフ特性を持つ半導体装置を容易に製造する。

【解決手段】可視光に対して透明な半導体基板1の表面にソース電極2及びドレイン電極3を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間に表側ゲート電極4を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間以外の領域に合わせマーク5を形成する。半導体基板1を透過して見える合わせマーク5に基づいて半導体基板1を位置合わせして、半導体基板1の裏面において表側ゲート電極4と対向する位置に裏側ゲート電極6を形成する。

(もっと読む)

半導体装置

【課題】 本発明の目的は、半導体装置単体で負電源を必要とせずにスイッチングが可能な素子を提供することである。

【解決手段】 この発明の半導体装置は、ノーマリオンFETと、一方の電極を前記FETのゲートに、他方の電極を入力端子に電気的に接続されたキャパシタと、アノード電極が前記FETのゲートに、カソード電極が前記FETのソースに電気的に接続されたダイオードと、を前記FETと同一チップ上に形成したことを特徴としており、さらに、前記キャパシタが、前記FETのゲート引き出し電極上に誘電体などの絶縁膜を形成し、形成した前記絶縁膜に金属膜を形成することにより形成されたことが好ましい。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】工程増を最小限とした簡便な手法で、素子形成領域における化合物半導体と同時に、しかもその結晶性を損なうことなく確実な素子分離を実現し、信頼性の高い化合物半導体装置を実現する。

【解決手段】Si基板1上の素子分離領域に初期層3を選択的に形成し、初期層3上を含むSi基板1上の全面に化合物半導体の積層構造4を形成して、積層構造4は、素子分離領域では初期層3と共に素子分離構造4Bとなり、素子形成領域ではソース電極5、ドレイン電極6及びゲート電極7が形成される素子形成層4Aとなる。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】所望の不純物濃度と、高い結晶性とを有するドリフト層を有する炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】バッファ層31は、基板30上に設けられ、不純物を含有する炭化珪素から作られ、1μmより大きく7μmより小さい厚さを有する。ドリフト層32は、バッファ層31上に設けられ、バッファ層31の不純物濃度よりも小さい不純物濃度を有する炭化珪素から作られている。

(もっと読む)

ノーマリオフ型パワーJFETの製造方法

【課題】SiC系JFETにおいて、トレンチゲート領域間を高精度に制御するため、ソース領域内にゲート領域を形成する必要がある。これにより増加するソース領域、ゲート領域間高濃度PN接合による接合電流を削減できる半導体装置を提供する。

【解決手段】ノーマリオフ型パワーJFETの製造方法であって、N型SiC1sの表面に、Nエピタキシャル下層1ea、中層1eb、上層1ec等複数層を形成し、表面には複数のソース層9、及びPゲート領域4が設けられる。ゲート領域はアクティブ領域3の外端部に接するように、下層、中層、上層のPエッジターミネーション領域7a、7b、7cが設けられる。裏側種面には、高濃度ドレイン層8が形成される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制する。

【解決手段】トレンチ6の先端部に形成されたn-型チャネル層7がトレンチ6の長辺に位置する部分よりも膜厚が厚くなるため、そのトレンチ6の先端部においてJFET構造が構成されないようにする。例えば、トレンチ6の先端部をp+型領域20にて埋め尽くすようにする。これにより、トレンチ6の先端部のJFET構造の閾値がトレンチ6の長辺に位置する部分のJFET構造の閾値からずれることによる影響を受けることがない。したがって、ゲート電圧が閾値近傍に近づくときに発生する過剰なドレイン電流を抑制できる構造のSiC半導体装置とすることが可能となる。

(もっと読む)

炭化ケイ素金属半導体電界効果トランジスタ及び炭化ケイ素の金属半導体電界効果トランジスタを製造する方法

【課題】深いレベルのドーパントがほとんど存在しない半絶縁性のSiC基板上にMESFETを形成することにより、バックゲート効果が減少された、SiCのMESFETを提供する。

【解決手段】半絶縁性の基板上10に選択的にドープされたP型の炭化珪素の層13、及びN型のエピタキシャル層14を積層し、背面ゲート効果を減少させる。また2つの凹部を有するゲート構造体も備える。これにより、出力コンダクタンスを1/3に減少することができ、また電力のゲインを3db増加することができる。クロム42をショットキーゲート接点として利用することもでき、酸化物−窒化物−酸化物(ONO)の保護層60を利用して、MESFET内の表面効果を減少させる。また、ソース及びドレインのオーム接点をn型チャネル層上に直接形成して、これにより、n+領域を製造する必要がなくなる。

(もっと読む)

ブール成長された炭化ケイ素ドリフト層を使用してパワー半導体デバイスを形成する方法、およびそれによって形成されるパワー半導体デバイス

【課題】炭化ケイ素の好ましい電気特性にもかかわらず、その中においてより厚い電圧サポート領域を有する炭化ケイ素パワーデバイスの必要性が引き続き存在している。

【解決手段】高電圧炭化ケイ素パワーデバイスを形成する方法は、法外に高いコストのエピタキシャル成長された炭化ケイ素層の代わりに、高純度炭化ケイ素ウエハ材料から得られる高純度炭化ケイ素ドリフト層を利用している。本方法は、約100μmより厚い厚みを有するドリフト層を使用して10kVを超えるブロッキング電圧をサポートすることができる少数キャリアパワーデバイスと多数キャリアパワーデバイスの両方を形成することを含んでいる。これらのドリフト層は、その中に約2×1015cm−3未満である正味n型ドーパント濃度を有するブール成長炭化ケイ素ドリフト層として形成される。このn型ドーパント濃度は、中性子変換ドーピング(NTD)技法を使用して実現することができる。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

接合型電界効果トランジスタを備えた半導体装置およびその製造方法

【課題】埋込ゲート層とゲート配線とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置を提供する。

【解決手段】埋込ゲート層10とゲート配線12との電気的な接続をトレンチ13内に形成したp+型コンタクト埋込層14によって行うようにする。これにより、p+型コンタクト埋込層14のみしか配置されないトレンチ13の幅を、従来の半導体装置のように層間絶縁膜やゲート配線などが配置されるトレンチと比較して、狭くすることが可能となる。したがって、埋込ゲート層10とゲート配線12とのコンタクト構造をより微細化できる構造としたJFETを有する半導体装置とすることが可能となる。

(もっと読む)

ソース領域の下にp型埋込み層を備えたトランジスタ及びその作製方法

【課題】本発明は、金属半導体電界効果トランジスタ(MESFET)を提供する。

【解決手段】このMESFETは、ソース(13)とドレイン(17)とゲート(24)とを備えている。このゲート(24)を、ソース(13)とドレイン(17)の間及びn導電型チャネル層(18)上に設ける。ドレイン(17)に向かって延びている端部を備えるp導電型領域(14)をソースの下に設ける。このp導電型領域(14)をn導電型チャネル領域(18)から隔ててソース(13)に電気的に結合させる。

(もっと読む)

1 - 20 / 168

[ Back to top ]