Fターム[5F102GL09]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 格子定数のずれ、格子歪の利用 (42)

Fターム[5F102GL09]に分類される特許

1 - 20 / 42

半導体装置

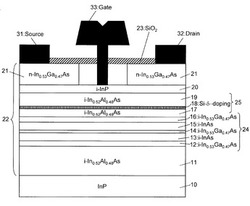

【課題】電子が第1励起準位に存在する割合が増えても、量子井戸層の中の電子の有効質量が軽くなる井戸層にできるだけ多くの電子が存在するようにして、より一層の高速化を実現する。

【解決手段】半導体装置を、基板10の上方に設けられた第1半導体層11と、第1半導体層11の上側に接する電子走行層24と、電子走行層24の上側に接する第2半導体層17(25)とを備えるものとし、電子走行層を24、第1井戸層13、中間障壁層14、第2井戸層15を順に積層させた構造を含む2重量子井戸層とし、中間障壁層14の伝導帯のエネルギーが、第1半導体層11及び第2半導体層17(25)の伝導帯のエネルギーよりも低くなり、第1井戸層13及び第2井戸層15の中に基底準位が形成され、2重量子井戸層の中に第1励起準位が形成されるようにする。

(もっと読む)

化合物半導体基板

【課題】化合物半導体層全体の膜厚を抑制しつつ、半導体素子の高い性能と信頼性を両立することのできる化合物半導体基板を提供する。

【解決手段】シリコン単結晶の基板12と、基板上に形成される化合物半導体の第1の半導体層16と、第1の半導体層上に形成され、第1の半導体層よりもバンドギャップエネルギーの大きい、化合物半導体の障壁層18と、障壁層上に形成され、障壁層よりもバンドギャップエネルギーの小さい化合物半導体の第2の半導体層20と、第2の半導体層上に形成され、第2の半導体層よりもバンドギャップエネルギーの大きい化合物半導体の第3の半導体層22とを有することを特徴とする化合物半導体基板。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】チャネル層及びバリア層のAl組成差を増大させてトランジスタ特性を改善可能な構造を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】第1の半導体層13は、歪みを含む。第1の半導体層13の歪んだAlYGa1−YNの格子定数d(13)は、無歪みのAlYGa1−YNに固有の格子定数d0(13)とAlXGa1−XNの格子定数d(21)との間の中間値を有する。歪んだAlYGa1−YNの格子定数d(13)と無歪みのAlZGa1−ZNに固有の格子定数d0(15)との差△1は、格子定数d0(15)と格子定数d0(13)との差△2より小さくなる。差分(△2−△1)に応じて、歪んだAlYGa1−YN上に成長可能な歪んだAlZGa1−ZNのAl組成を増加でき、AlYGa1−YNとAlZGa1−ZNのAl組成差を0.5以上にできる。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】半導体積層内の電流経路からゲート電極を隔てる半導体層を厚くできるIII族窒化物半導体電子デバイスを提供する。

【解決手段】第2の半導体層15は第1の半導体層13上に設けられる。ゲート電極17は第2の半導体層15の上に設けられる。第1の半導体層13は、AlXGa1−XN(0<X≦1)からなる半導体表面21aの上に設けられる。第2のIII族窒化物半導体材料のバンドギャップE15は第1のIII族窒化物半導体材料のバンドギャップE13より大きい。第1の半導体層13の第1のIII族窒化物半導体材料はAlXGa1−XNと異なり、第1の半導体層13は歪みを内包する。また、第2の半導体層15の厚さT15は、無歪みの第1のIII族窒化物半導体材料の組成と、第2のIII族窒化物半導体の組成により規定される臨界膜厚より大きい。また、第1の半導体層13は、歪みを内包すると共に、半導体表面21aのAlXGa1−XNの上において格子緩和している。

(もっと読む)

基板上に堆積された窒化ガリウムフィルムにおける応力の制御方法

【課題】シリコンおよび炭化ケイ素基板上に堆積されたGaNフィルムにおける応力の制御方法、およびこれによって生成されたGaNフィルムを提供する。

【解決手段】典型的な方法は、基板を供給すること、および供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上にグレーデッド窒化ガリウム層を堆積させることを含む。典型的な半導体フィルムは、基板と、供給の中断をまったく伴なわず、成長チャンバへの少なくとも1つの先駆物質の供給によって形成された、当初組成物から最終組成物までの実質的に連続したグレードの様々な組成物を有する基板上に堆積されたグレーデッド窒化ガリウム層とを含む。

(もっと読む)

電界効果トランジスタ

【課題】エンハンスメントモードトランジスタデバイスと、デプレッションモードトランジスタデバイスにおいて、エッチングストッパ層の選択エッチング性を改善し歩留り向上を図る。

【解決手段】チャネル層20の上に、エンハンスメントモードトランジスタデバイスの、InGaPエッチストップ/ショットキーコンタクト層が配置され、その上に、InGaPとは異なる第1の層26が配置され、第1の層の上に、デプレッションモードトランジスタデバイスエッチストップ層28が配置され、エッチストップ層の上に第2の層30が配置される。デプレッションモードトランジスタデバイスは、第2の層及びエッチストップ層を貫通し第1の層で終止するゲートリセスを有する。エンハンスメントモードトランジスタデバイスは、第2の層、デプレッションモードトランジスタデバイスエッチストップ層、第1の層を貫通しInGaP層で終止するゲートリセスを有する。

(もっと読む)

半導体装置

【課題】二次元電子ガスの濃度を高めることが可能な半導体装置を提供すること。

【解決手段】本発明は、GaNからなるチャネル層14と、チャネル層14上に設けられ、下側がInxAl1−xN(0≦x<1)からなり、上側がInxAl1−xN(0<x<1)からなる電子供給層16と、電子供給層16上に設けられ、GaNからなるキャップ層18と、を具備する半導体装置である。本発明によれば、チャネル層14と電子供給層16との界面に発生する二次元電子ガスの濃度を高めることができる。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

半導体装置およびその作製法

【課題】チャネル層半導体として用いるInN系半導体において、高濃度の残留背景電子が存在していても、ピンチオフ特性が得られ、InN系半導体の優れた電子輸送特性(高い電子移動度および高い飽和電子速度)が活用可能となる、窒化物半導体を用いた導体装置およびその作製法を提供すること。

【解決手段】ソース電極1にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるソース側へテロ接合構造、および、ドレイン電極3にオーミック接触する障壁層半導体とオーミック領域チャネル層半導体とから形成されるドレイン側へテロ接合構造が形成され、それぞれのへテロ接合構造が、InN系チャネル層半導体(#)と接し、それぞれのへテロ接合構造において、ヘテロ接合界面近傍のみに伝導電子が局在し、ヘテロ接合界面の垂直方向位置が、InN系チャネル層半導体(#)の層内位置に存在することを特徴とする半導体装置を構成する。

(もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネルの高い移動度と、優れた縦方向耐圧とを得た上で、安定して低いオン抵抗を確保することができる、半導体装置等を提供する。

【解決手段】本発明の半導体装置は、n型ドリフト層4/p型層6/n型表層8を含むGaN系積層体15、に形成され、GaN系積層体には、開口部5が設けられ、再成長層27と、ゲート電極11と、ソース電極31と、ドレイン電極39とを備え、再成長層27は電子走行層22および電子供給層26を含み、チャネルが二次元電子ガスであり、p型層6とn型表層8との間、および開口部を囲むGaN系積層体の端面と再成長層との間、の少なくとも一方に、GaNよりも格子定数が小さいエピタキシャル層が挿入されていることを特徴とする。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

半導体装置

【課題】GaNを含む基板上において、バッファリークを低減したデバイスを得ること。

【解決手段】窒化ガリウム(GaN)を含む基板(11)上に、緩衝層(12)を介して、化学式AlxMyGa1−x−yN(0≦x≦1、0≦y≦1、0≦x+y<1、ここで、MはIn、Bのうちの1種を少なくとも含む)で表される組成をもつ能動層(13、14)が形成された構成を具備し、該能動層において前記基板の基板面と平行な方向に電流が流されて動作する半導体装置(10)であって、

前記緩衝層は、化学式AlpIn1−pN(0≦p<1)で表される組成と前記基板よりも大きいバンドギャップとを有し、かつ、前記基板と格子整合することを特徴とする半導体装置。

(もっと読む)

化合物半導体電子デバイス、及び化合物半導体集積電子デバイス

【課題】ウルツ鉱構造の化合物半導体を用いてノーマリ・オフの化合物半導体電子デバイスを提供する。

【解決手段】キャリア走行半導体層15はスペーサ半導体層17と支持体13との間に位置する。基準軸Nxは、支持体13のウルツ鉱のc軸に直交する。電子デバイス11では、基準軸Nxに直交した基準平面R2に沿ってヘテロ接合が延びるので、ピエゾ電界Pzが基準平面R2に平行な方向に向く。ピエゾ電界Pzはヘテロ接合21に沿って延在する内部電界として働き、これはヘテロ接合21の二次元キャリアに作用して、ゲート電極19直下のヘテロ接合における電子濃度が調整される。内部電界の働きによりゲート電極19にゼロボルトが印加されるとき、二次元電子はゲート電極19直下のヘテロ接合21のバンドの屈曲部に実質的に蓄積されず、電子デバイス11はノーマリ・オフ特性を有する。

(もっと読む)

半導体ウェーハ及び半導体素子及びその製造方法

【課題】基板上に化合物半導体層を厚く形成することができ、バッファ領域内に生じる寄生容量を低減することができる半導体ウェーハ、半導体素子、及びその製造方法を提供する。

【解決手段】バッファ領域3は、第1の層6と第2の層7とが交互に複数配置された複数の多層構造バッファ領域5、5´と、複数の多層構造バッファ領域5、5´の相互間に配置され、第1の層6及び第2の層7よりも厚く形成され、且つ第1の層6を構成する材料の格子定数と第2の層7の格子定数との間の格子定数を有する化合物半導体から成る。

(もっと読む)

化合物半導体電子デバイス、化合物半導体集積電子デバイス及びエピタキシャル基板

【課題】ウルツ鉱構造の化合物半導体を用いてノーマリ・オフの化合物半導体電子デバイスを提供する。

【解決手段】キャリア走行半導体層15はスペーサ半導体層17と支持体13との間に位置する。電子デバイス11では、基準軸Cxに対して傾斜した基準平面R2に沿ってヘテロ接合が延びるので、ピエゾ電界Pzも基準平面R2に対して傾斜した方向に向く。ピエゾ電界の平行な成分Pz(T)はヘテロ接合21に沿って延在する内部電界として働く。この内部電界はヘテロ接合21の二次元キャリアに作用して、ゲート電極19直下のヘテロ接合におけるキャリア濃度が調整される。内部電界の働きにより、ゲート電極19にゼロボルトが印加されているとき、二次元キャリアは、ゲート電極19直下のヘテロ接合21のバンドの屈曲部に実質的に蓄積されない。電子デバイス11はノーマリ・オフ特性を有する。

(もっと読む)

電界効果半導体装置及びその製造方法

【課題】オン抵抗及びゲートリーク電流の小さいノーマリオフ特性を有し、且つ特性のばらつきが少ない電界効果半導体装置を提供する。

【解決手段】第1の半導体層4と、前記第1の半導体層上に配置され且つ前記第1の半導体層よりも格子定数が小さい材料で形成された第2の半導体層5aと、前記第2の半導体層上に配置され且つ前記第1の半導体層よりも格子定数が小さい材料で形成された第3の半導体層5bとを備える主半導体領域と、前記主半導体領域上に配置された第1の主電極6と、前記主半導体領域上に配置された第2の主電極7と、前記主半導体領域上における前記第1の主電極と前記第2の主電極との間に配置され且つ前記第3の半導体層を貫通する凹部と、前記凹部上に配置される金属酸化物半導体膜10と、前記金属酸化物半導体膜上に配置されるゲート電極8と、を備えることを特徴とする電界効果半導体装置。

(もっと読む)

窒化物半導体装置

【課題】高出力かつ高周波動作が可能な窒化物半導体装置を提供する。

【解決手段】基板上に、第1窒化物半導体材料で構成されるバッファ層と、AlとInとGaとNとを含み、GaNより大きな絶縁破壊電界を有し、GaNより大きな飽和電子速度を有し、第2窒化物半導体材料で構成されるチャネル層と、第2窒化物半導体材料よりも大きなバンドギャップを有する第3窒化物半導体材料で構成されるバリア層とを備えた窒化物半導体装置による。

(もっと読む)

半導体積層体を含む半導体装置の製造方法

【課題】 半導体下層と半導体上層が積層された半導体積層体において、半導体下層の表面に損傷を与えることなく、半導体下層の一部を露出させる技術を提供する

【解決手段】 半導体下層18の表面の一部に、半導体上層15とは格子定数の異なる格子不整合層30を形成する工程と、格子不整合層30の表面と格子不整合層30で被覆されていない半導体下層18の表面に、半導体上層15を結晶成長させる工程と、格子不整合層30上の半導体上層15に形成された転位40を介してウェットエッチング液を導入し、格子不整合層30とその格子不整合層30上の半導体上層15を除去して半導体下層18の一部を露出させる工程を備える。ドライエッチングにより半導体下層18に損傷を与えることなく、半導体下層18の一部を露出させることができる。

(もっと読む)

半導体装置

【課題】窒化物半導体からなるノーマリオフ型の半導体装置であって、電流コラプスを抑制し且つ大電流密度及び高耐圧特性を得られるようにする。

【解決手段】半導体装置は、基板101の上に形成されたアンドープGaN層103と、アンドープGaN層103の上に形成され、バンドギャップエネルギーがアンドープGaN層103よりも大きいアンドープAlGaN層104と、アンドープAlGaN層104の上に形成されたp型AlGaN層105及び高濃度p型GaN層106と、高濃度p型GaN層106の上に形成されたn型AlGaN層107とを有している。高濃度p型GaN層106におけるn型AlGaN層107に形成された開口部107aからの露出領域の上には、高濃度p型GaN層106とオーミック接触するゲート電極112が形成されている。

(もっと読む)

1 - 20 / 42

[ Back to top ]