Fターム[5F102GL14]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 材質が不均質なもの (162)

Fターム[5F102GL14]の下位に属するFターム

不純物濃度が不均一 (35)

組成(バンドギャップ)が不均一 (44)

厚さ方向(基板垂直)に変化 (41)

ソース、ドレイン方向(表面に平行)に変化 (22)

Fターム[5F102GL14]に分類される特許

1 - 20 / 20

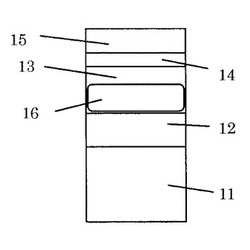

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコン基板上にバッファ層を介して形成されるGaN層を高品質にすることが可能な半導体装置およびその製造方法を提供すること。

【解決手段】本発明は、シリコン基板10上に設けられ、GaNよりもバンドギャップが大きいバッファ層16と、バッファ層16上に設けられた第1のGaN層18と、第1のGaN層18の上面に接して設けられた第2のGaN層20と、を有し、第1のGaN層18に含まれる炭素の濃度は、第2のGaN層20に含まれる炭素の濃度に比べて高い半導体装置である。

(もっと読む)

電界効果トランジスタ

【課題】III族窒化物半導体からなる電界効果トランジスタにおける高電圧スイッチング時の電流コラプスを効果的に抑制できるようにする。

【解決手段】第1の半導体層103は、少なくともゲート電極106におけるドレイン電極107側の端部の下側の領域において、炭素濃度が1×1017cm−3未満である低炭素濃度領域を有し、基板101の上面から第1の半導体層103及び第2の半導体層104を含むドレイン電極までの半導体層の厚さをd1(μm)とし、低炭素濃度領域の厚さをd2(μm)とし、動作耐圧をVm(V)としたとき、Vm/(110・d1)≦d2<Vm/(110・d1)+0.5の関係を満たし、且つ、緩和状態におけるオン抵抗をRon0とし、動作電圧Vmにおけるオフ状態からオン状態に遷移した100μs後のオン抵抗をRonとしたとき、電流コラプス値の指標とするRonとRon0との比の値が、Ron/Ron0≦3である。

(もっと読む)

電界効果型トランジスタ

【課題】正孔の蓄積によるキンク現象の発生および耐圧の低下を、効果的に抑制できるようにする。

【解決手段】半絶縁性のInPからなる基板101と、基板101の上に形成されて、炭素(C)がp形の不純物として導入されたGaAsSbからなる正孔走行層102と、正孔走行層102の上に形成されたInGaAsからなるチャネル層103と、チャネル層103の上に形成された電子供給層104と、電子供給層104の上に形成された障壁層105とを備える。

(もっと読む)

電界効果トランジスタ、電界効果トランジスタの製造方法、および電子装置

【課題】 高い閾値電圧と、低いオン抵抗とを両立可能であり、かつ、パラレル伝導を抑制できる電界効果トランジスタを提供する。

【解決手段】

基板601上に、III族窒化物のバッファ層602、チャネル層603、障壁層605、およびキャップ層606が、前記順序で積層され、

各半導体層の上面は、(0001)結晶軸に垂直なIII族原子面であり、

バッファ層602は、格子緩和され、

障壁層605は、引っ張り歪みを有し、

チャネル層603およびキャップ層606が圧縮歪みを有するか、または、チャネル層603が格子緩和され、キャップ層606が引っ張り歪みを有し、

障壁層605上の一部の領域に、キャップ層606、ゲート絶縁膜607、およびゲート電極608が、前記順序で積層され、他の領域に、ソース電極609とドレイン電極610が形成されていることを特徴とする電界効果トランジスタ。

(もっと読む)

デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法

【課題】デュアル・デプレションを示す高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】互いに異なる極性を有する複数の半導体層20,22を含み、ソース電極28とドレイン電極32との間にデュアル・デプレション領域が存在し、該複数の半導体層は、上部物質層26、中間物質層22、下部物質層20を含み、中間物質層の極性は、上部物質層及び下部物質層の極性と異なる高電子移動度トランジスタである。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】基板の放熱性が高くて基板に形成される窒化物半導体層の結晶欠陥が少ない窒化物半導体装置及びその製造方法を提供する。

【解決手段】

HEMT10の製造方法は、サファイア基板11の表面にGaNの薄膜12を形成する成膜工程と、薄膜12の上端からサファイア基板11の内部に達する深さの溝を形成する溝形成工程と、溝形成工程の後に、薄膜12を種結晶としてGaN層13を成長させる成長工程と、成長工程の前又は後に、サファイアよりも熱伝導性が高い高熱伝導性材料としてのAuを溝17に充填する充填工程とを備えている。

(もっと読む)

接合型電界効果トランジスタ

【課題】耐圧性に優れかつチャネル領域の不純物濃度やその厚さ等のばらつきの影響を受けにくいJFETを提供する。

【解決手段】SiC基板9の一方面上にはアルミニウム膜7が形成されている。そのアルミニウム膜7に接するように、そのアルミニウム膜7の両側に、SiC膜からなるチャネル領域4a、4bが設けられている。チャネル領域4a、4b上にはソース領域5a、5bを介してソース電極11a、11bが形成されている。チャネル領域4a、4bのアルミニウム膜7側と反対側にp型SiC膜2a、2bを介してゲート電極13が形成されている。SiC基板9の他方面上には、ドレイン領域6が形成されている。

(もっと読む)

電界効果トランジスタ、半導体基板及び電界効果トランジスタの製造方法

【課題】高いチャネル移動度を有する電界効果トランジスタを提供する。

【解決手段】ゲート絶縁層と、前記ゲート絶縁層に接する第1半導体結晶層と、第1半導体結晶層に格子整合または擬格子整合する第2半導体結晶層とを有し、前記ゲート絶縁層、前記第1半導体結晶層および前記第2半導体結晶層が、ゲート絶縁層、第1半導体結晶層、第2半導体結晶層の順に配置されており、前記第1半導体結晶層がInx1Ga1−x1Asy1P1−y1(0<x1≦1、0≦y1≦1)であり、前記第2半導体結晶層がInx2Ga1−x2Asy2P1−y2(0≦x2≦1、0≦y2≦1、y2≠y1)であり、前記第1半導体結晶層の電子親和力Ea1が前記第2半導体結晶層の電子親和力Ea2より小さい電界効果トランジスタを提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】チャネルにおけるキャリア移動度が高く、ノーマリオフを実現する半導体装置を提供する。

【解決手段】 n型GaNキャップ層18の開口部28との界面(開口部境界面)は、複数のほぼ鉛直な面S1と、各面S1の間を補完するように形成された傾斜した面S3により構成されている。傾斜面はドライエッチングにより形成し、異方性エッチングによりダメージ層を除去する。縦型FET1では、GaN基板10上に、六方晶のGaN、AlGaNを、{ 0 0 0 1}面を成長面として、エピタキシャル成長させており、n型GaNキャップ層18における鉛直な面S1は、{ 1-1 0 0}面(m面)となる。m面は、C面とは異なり無極性面であるので、m面を成長面として、GaN電子走行層22、AlGaN電子供給層26を再成長させると、ピエゾ電荷等の分極電荷がAlGaN/GaNヘテロ界面に生じない。よって、縦型FET1においては、よりノーマリオフに近づけることが可能となる。

(もっと読む)

希土類エンハンスト高電子移動度トランジスタ及びその製造方法

【課題】半導体活性領域からの電荷キャリアの脱出を阻止して、電荷キャリアのより有効な閉じ込めを示すHEMTを提供する。

【解決手段】希土類添加物をドープされた第1のIII−V族真性層209aを備えた高電子移動度トランジスタ(HEMT)200Aであって、前記真性層の上に形成された第2のIII−V族真性層210a及び該第2のIII−V族真性層の上に形成されたIII−V族半導体層220も備える。HEMTの製造方法は、第1のIII−V族真性層209aを形成し、該第1のIII−V族真性層に希土類添加物をドーピングして絶縁層を形成する。更に前記絶縁層の上に第2のIII−V族真性層210aを形成し、該第2のIII−V族真性層の上にIII−V族半導体層220を形成する。前記III−V族半導体層と前記第2のIII−V族真性層とのヘテロ接合界面に二次元電子ガス(2DEG)212が形成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】縦型構造のHEMTにおけるオン抵抗を低減することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】基板1と、基板1の上方に形成された電子供給層4及び電子走行層2と、電子供給層4及び電子走行層2の上方に形成されたソース電極21s及びゲート電極21gと、基板1の裏面に形成されたドレイン電極21dと、が設けられている。そして、電子供給層4の少なくとも一部と電子走行層2の少なくとも一部とが、基板1の表面に平行な面から傾斜した面を境にして互いに接している。

(もっと読む)

半導体装置とその製造方法

【課題】 転位の発生を抑制しながら、p型半導体領域に含まれるp型不純物が隣接する他の半導体領域に拡散する現象を抑制する技術を提供する。

【解決手段】 Mg(p型不純物)を含む窒化ガリウムのp型半導体領域24と、窒化ガリウムのn型半導体下領域20と、p型半導体領域24とn型半導体下領域20との間に設けられている不純物拡散抑制領域22を備えている。不純物拡散抑制領域22は、Inx1Al1-x1N(但し、0<X1<1)である。

(もっと読む)

GaN系電界効果トランジスタおよびその製造方法

【課題】低抵抗・高耐圧で電流コラプス現象の影響の小さいGaN系電界効果トランジスタおよびその製造方法を提供する。

【解決手段】GaN系電界効果トランジスタ(MOSFET)100は、基板101上に、p−GaNからなるチャネル層104、電子供給層106、電子供給層よりもバンドギャップエネルギーが小さい表面層107を順次積層し、電子供給層および表面層の一部をチャネル層に到る深さまで除去してリセス部108を形成したものである。表面層上には、リセス部を挟んでソース電極109およびドレイン電極110が形成され、表面層上およびチャネル層表面を含むリセス部内表面上にゲート絶縁膜111が形成され、さらにリセス部においてゲート絶縁膜上にはゲート電極112が形成されている。

(もっと読む)

ガリウムナイトライド系エピタキシャル結晶及びその製造方法

【課題】高い破壊耐圧、高い電子移動度及び低いゲート漏れ電流を併せ持つ高性能の電界効果トランジスタを提供すること。

【解決手段】GaN系FET用エピタキシャル結晶基板において、下地基板101の上に設けられるエピタキシャル結晶が、ゲート層108の下地基板側界面に接するチャネル層を含む高純度な第1の緩衝層107と、第2の緩衝層106と、開口部104Aを有する絶縁層104と、p伝導型半導体結晶層103とを有している。第1の緩衝層107をp伝導型半導体結晶層103に電気的に接続するための接続層105が開口部104Aに配されており、第1の緩衝層107に滞留する正孔を接続層105を介してp伝導型半導体結晶層103に引き抜くことができる。

(もっと読む)

窒化物半導体トランジスタ及びその製造方法

【課題】動作電流が大きく且つスイッチング特性に優れたノーマリオフ型の窒化物半導体トランジスタを実現できるようにする。

【解決手段】窒化物半導体トランジスタは、第1の窒化物半導体層13と、第1の窒化物半導体層13の上に形成され、第1の窒化物半導体層13と比べてバンドギャップが大きい第2の窒化物半導体層14と、第2の窒化物半導体層14の上に形成された第3の窒化物半導体層15とを備えている。第3の窒化物半導体層15におけるゲート電極20の下側の領域には、p型の導電性を有するコントロール領域15aが形成され、第3の窒化物半導体層におけるゲート電極15とソース電極18及びドレイン電極19との間の領域には、コントロール領域15aよりも抵抗値が高い高抵抗領域15bが形成されている。

(もっと読む)

窒化物半導体素子

【課題】ノーマリーオフ特性および低オン抵抗を有する窒化物半導体素子を提供する。

【解決手段】アンドープの窒化物半導体からなる第1の半導体層と、前記第1の半導体層の上に設けられ、前記第1の半導体層よりもバンドギャップが広く、アンドープもしくはn型の窒化物半導体からなる第2の半導体層と、前記第2の半導体層に選択的に形成されたp型領域と、前記p型領域の上に設けられたゲート絶縁膜と、前記p型領域の周囲の前記第2の半導体層の上に設けられたフィールド絶縁膜と、前記p型領域を挟んで第2の半導体層にそれぞれ接続された第1及び第2の主電極と、前記ゲート絶縁膜の上に設けられ、少なくともその一部が前記フィールド絶縁膜の上まで延在してなる制御電極と、を備えたことを特徴とする窒化物半導体素子が提供される。

(もっと読む)

リサーフ構造を用いた窒化物半導体ヘテロ接合トランジスタ

【課題】リサーフの効果を用いる構造により窒化物系ヘテロ接合トランジスタの高耐圧化を行う。

【解決手段】窒化物半導体により構成されるトランジスタにおいて、GaN層3とAlyGa1−yNバリアー層4のヘテロ接合に形成された二次元キャリアガスの特性を持つn型チャンネルに対して、AlxGa1−xNバリアー層2とGaN層3のヘテロ接合にp型の二次元状キャリアを持つ電界制御チャンネルを平行に形成し、チャンネルと電界制御チャンネルが空乏化したときの空間固定電荷の面密度が実質的に等しくなるトランジスタ構造とすることにより、リサーフ効果を持たせ、これにより、オン耐圧やオフ耐圧の向上を行う。

(もっと読む)

へテロ接合型のIII−V族化合物半導体装置とその製造方法

【課題】 ヘテロ接合型のIII-V族化合物半導体装置において、オフ時のリーク電流を抑制するとともにオン時の抵抗を低減する。

【解決手段】 GaNの下層46と、その下層46にヘテロ接合されており、下層46のバンドギャップよりも大きなバンドギャップを有するAlGaNの上層48と、上層48の表面の一部に形成されているソース電極54と、上層48の表面の他の一部に形成されているゲート電極52を備えており、前記下層46は、ヘテロ接合界面と平行な面内において、結晶欠陥高密度領域72と結晶欠陥低密度領域が分布しており、ソース電極54は、結晶欠陥低密度領域に対向する領域内に形成されており、ゲート電極52は、結晶欠陥高密度領域72に対向する領域に形成されているIII-V族化合物半導体装置。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】 電界緩和を図り高耐圧化を実現することに加え、デバイスサイズの更なる減少化、正孔の引き抜きを容易にして、信頼性の高い優れた化合物半導体装置を実現する。

【解決手段】 本発明の化合物半導体装置は、GaAs等の第1の化合物半導体層上に、電子に対する障壁が伝導帯にあり、且つ正孔に対する障壁が価電子帯にない、即ちタイプII構造のバンド構造を有する属元素と6属元素の化合物からなるアモルファス層、例えばアモルファスGaS層(a−GaS層)を有するものである。

(もっと読む)

1 - 20 / 20

[ Back to top ]