Fターム[5F102GL16]の内容

接合型電界効果トランジスタ (42,929) | チャネル層(主電流が流れる半導体層) (3,041) | 材質が不均質なもの (162) | 組成(バンドギャップ)が不均一 (44)

Fターム[5F102GL16]に分類される特許

1 - 20 / 44

化合物半導体装置及びその製造方法

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、オン抵抗を低くしつつ、閾値電圧を高くする。

【解決手段】キャップ層400と障壁層300の界面、及びチャネル層200とバッファ層100の界面には圧縮歪が生じており、障壁層300とチャネル層200の界面には引張り歪が生じている。このため、キャップ層400と障壁層300の界面、並びにチャネル層200とバッファ層100の界面において、負の電荷が正の電荷よりも多くなっており、障壁層300とチャネル層200の界面において、正の電荷が負の電荷よりも多くなっている。チャネル層200は、第1層、第2層、及び第3層の積層構造を有している。第2層は、第1層及び第3層よりも電子親和力が大きい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】窒化物半導体層をチャネルとして用いたトランジスタにおいて、閾値電圧を高くする。

【解決手段】第2窒化物半導体層200は、Alの組成比が互いに異なる複数の窒化物半導体層を順次積層した構造を有するため、Al組成が階段状に変化している。第2窒化物半導体層200を形成する複数の半導体層は、それぞれが同一方向に分極している。そしてゲート電極420に近い半導体層は、ゲート電極420から遠い半導体層よりも、分極の強度が強く(又は弱く)なっている。すなわち複数の半導体層は、ゲート電極420に近づくにつれて、分極の強度が一方向に変化している。この分極の方向は、複数の半導体層内の界面において負の電荷が正の電荷よりも多くなる方向である。

(もっと読む)

窒化物系半導体素子

【課題】本実施形態は、窒化物半導体層のクラックがほとんどなく、表面の粗度が極めて優秀であるので、全体的な安定性の向上された窒化物系半導体素子を提供する。

【解決手段】本実施形態の窒化物系半導体素子は、基板と、前記基板上に形成されるアルミニウムシリコンカーバイド(AlSixC1−x)前処理層と、前記前処理層上に形成されるAlがドーピングされたGaN層と、前記AlがドーピングされたGaN層上に形成されるAlGaN層とを含む。

(もっと読む)

窒化物半導体基板及びその製造方法

【課題】より高いしきい値電圧と電流コラプス改善を両立できる、ノーマリーオフ型の高耐圧デバイスに好適な窒化物半導体基板及びその製造方法を提供する。

【解決手段】基板1と、前記基板1の一主面上に形成されるバッファー層2と、前記バッファー層2上に形成される中間層3と、前記中間層3上に形成される電子走行層4と、前記電子走行層4上に形成される電子供給層5とを含む窒化物半導体基板10において、前記中間層3を厚さ200nm以上1500nm以下、炭素濃度5×1016atoms/cm3以上1×1018atoms/cm3以下のAlxGa1-xN(0.05≦x≦0.24)とし、前記電子走行層4が厚さ5nm以上200nm以下のAlyGa1-yN(0≦y≦0.04)とする。

(もっと読む)

III族窒化物半導体電子デバイス、エピタキシャル基板、及びIII族窒化物半導体電子デバイスを作製する方法

【課題】チャネル層及びバリア層のAl組成差を増大させてトランジスタ特性を改善可能な構造を有するIII族窒化物半導体電子デバイスを提供する。

【解決手段】第1の半導体層13は、歪みを含む。第1の半導体層13の歪んだAlYGa1−YNの格子定数d(13)は、無歪みのAlYGa1−YNに固有の格子定数d0(13)とAlXGa1−XNの格子定数d(21)との間の中間値を有する。歪んだAlYGa1−YNの格子定数d(13)と無歪みのAlZGa1−ZNに固有の格子定数d0(15)との差△1は、格子定数d0(15)と格子定数d0(13)との差△2より小さくなる。差分(△2−△1)に応じて、歪んだAlYGa1−YN上に成長可能な歪んだAlZGa1−ZNのAl組成を増加でき、AlYGa1−YNとAlZGa1−ZNのAl組成差を0.5以上にできる。

(もっと読む)

半導体積層体とこれを含むHFETおよびそれらの製造方法

【課題】半導体積層体に含まれるチャネル層下の化合物半導体層を不純物ドーピングでp型化することなく、その半導体積層体を含むHFETのリーク電流の低減や耐電圧の向上などを可能とする。

【解決手段】半導体積層体は、基板(11)上において順次堆積された第1、第2および第3の化合物半導体層(13、14、15)を少なくとも含み、その第1化合物半導体層(13)の少なくとも部分的層(16)は非晶質に改質されており、第2化合物半導体層(14)は第1化合物半導体層(13)に比べて小さなバンドギャップを有して光吸収層として作用し得る。

(もっと読む)

窒化物半導体基板

【課題】

しきい値電圧をより向上させることのできる、中間層とデバイス活性層の間にノーマリ

ーオフ作用をもつ窒化物半導体層を形成する。

【解決手段】

Si単結晶基板上に形成され窒化物半導体の積層構造からなる中間層と、中間層上に形成され、組成AlxGa1−xN(0≦x≦0.05)、厚さ200nm以上2000nm以下、炭素濃度1´1018atoms/cm3以上1´1021atoms/cm3以下の窒化物半導体からなる領域1と、領域1上に形成され、組成AlyGa1−yN(0.1≦y≦1)、厚さ0.2nm以上100nm以下、炭素濃度1´1018atoms/cm3以上1´1021atoms/cm3以下の窒化物半導体からなる領域2と、領域2上に形成される窒化物半導体のデバイス活性層からなる窒化物半導体基板。

(もっと読む)

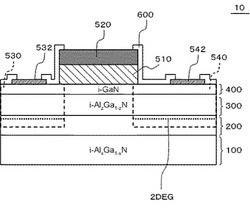

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

III族窒化物半導体からなる半導体装置およびその製造方法、電力変換装置

【課題】主面をm面とするIII 族窒化物半導体で構成されたHFETにおいて、正のしきい値電圧を高めること。

【解決手段】HFET100は、凹凸加工されたa面サファイア基板101上に、m面を主面とするGaNからなるバッファ層102、ノンドープのGaNからなるチャネル層103、ノンドープのAlGaNからなる障壁層104、酸素ドープのn−AlGaNからなるキャリア供給層105を有している。キャリア供給層105は2つの領域に分離して形成されている。キャリア供給層105は、障壁層104上に選択的に再成長させて形成した層である。ゲート電極109にバイアスを印加しない状態では、ゲート電極109直下に2DEGが形成されないため、正のしきい値電圧を高めることができる。

(もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

電界効果トランジスタ

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供すること。

【解決手段】この電界効果トランジスタは、略同一の第1、第2トランジスタ部11,12を備える。第1のトランジスタ部11は、ヘテロ接合を含むIII族窒化物半導体層構造、III族窒化物半導体層構造上に間隔をおいて配置されたソース電極5およびドレイン電極7、フィールドプレート91を有するゲート電極6、ドレイン電極7を被覆するように配置された絶縁体層8を有する。フィールドプレート91は、ドレイン電極7を覆うようにひさし状に延在する。第2のトランジスタ部12は、第1のトランジスタ部11と略面対称に配置されている。第1のトランジスタ部11のIII族窒化物半導体層構造、絶縁体層8およびドレイン電極7は、第2のトランジスタ部12において対応する構造または層と一体化されている。

(もっと読む)

半導体装置およびそれを備えた電子回路

【課題】同一のボンディングパッドに対して異なる金属のボンディングワイヤーを用いて信頼性の高い配線を行う。

【解決手段】窒化物半導体ヘテロ接合型電界効果トランジスタにおけるソース電極8,ドレイン電極9,ソースパッド8'およびドレインパッド9'をTi,Al,MoおよびAuを順次積層して形成し、ソースパッド8'およびドレインパッド9'の一部をエッチングによって開口して、Al露出部を形成している。したがって、ソースパッド8'またはドレインパッド9'におけるAu露出部に対しては、Auボンディングワイヤーを用いたワイヤーボンディングを行う一方、上記Al露出部に対しては、Alボンディングワイヤーを用いたワイヤーボンディングを行うことによって、優れた密着性とエレクトロマイグレーション耐性を得ることができる。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】トランジスタ中の電子移動度を向上させる上、デバイスの性能を向上させる高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタは、基板110と、基板110上に形成したバッファ層120と、複数のInGaAs薄膜と複数のInAs薄膜とを交互に積層して形成した超格子構造を含み、バッファ層120上に形成したチャネル層130と、チャネル層130上に形成したスペーサ層140と、スペーサ層140上に形成したショットキー層160と、ショットキー層160上に形成したキャップ層170とを備える。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】高電圧を印加しても壊れにくい電界効果トランジスタを提供する。

【解決手段】電界効果トランジスタは、基板1、チャネル層3及びバリア層4と、バリア層4上にこの順で離間して設けられたソース電極6、ゲート電極7およびドレイン電極8とを備え、ソース電極6の直下に第1のn型不純物拡散領域12が設けられ、ドレイン電極8の直下に第2のn型不純物拡散領域13が設けられ、第2のn型不純物拡散領域の下側の前記チャネル層3および第2のn型不純物拡散領域の前記ゲート電極側の前記チャネル層3および前記バリア層4に第3のn型不純物拡散領域15が設けられる。第3のn型不純物拡散領域15は第2のn型不純物拡散領域13よりも低いn型不純物濃度を有し、ゲート電極とドレイン電極との間に電圧が印加されたときバリア層4およびチャネル層3においてその絶縁破壊強度を超える電界集中が生じることを抑制する。

(もっと読む)

半導体素子用エピタキシャル基板、半導体素子、および、半導体素子用エピタキシャル基板の作製方法

【課題】ショットキーコンタクト特性が優れており、かつ、良好なデバイス特性を有する半導体素子を実現することができるエピタキシャル基板を提供する。

【解決手段】下地基板の上に、少なくともAlとGaを含む、Inx1Aly1Gaz1N(x1+y1+z1=1)なる組成の第1のIII族窒化物からなるチャネル層を形成し、チャネル層の上に、少なくともInとAlを含む、Inx2Aly2Gaz2N(x2+y2+z2=1)なる組成の第2のIII族窒化物からなる障壁層を、表面近傍部におけるIn組成比が表面近傍部以外の部分におけるIn組成比よりも小さくなるように形成する。

(もっと読む)

横方向を電流導通方向とする電子デバイス用エピタキシャル基板およびその製造方法

【課題】HEMTのシート抵抗を非接触で精度良く測定することができる横方向を電流導通方向とする電子デバイス用エピタキシャル基板およびこの電子デバイス用エピタキシャル基板を効率よく製造する方法を提供する。

【解決手段】高抵抗Si単結晶基板の一方の面上に、不純物拡散抑制層を形成する工程と、前記高抵抗Si単結晶基板の他方の面上に、絶縁層としてのバッファを形成する工程と、該バッファ上に、複数層のIII族窒化物層をエピタキシャル成長させて主積層体を形成してエピタキシャル基板を作製する工程と、該エピタキシャル基板の主積層体の抵抗を非接触で測定する工程とを具えることを特徴とする。

(もっと読む)

ヘテロ接合電界効果トランジスタ、その製造方法

【課題】ゲート電極下の電子の走行方向が基板表面に略平行であるようにデバイス構造を改良しながらも各種弊害を解消したヘテロ接合電界効果トランジスタを提供する。

【解決手段】n型導電層は選択的にイオン注入されているシリコン(Si)などのn型不純物をアニール処理で活性化することにより形成されており、n型導電層は、イオンが200keV以上の加速エネルギーで注入されており、p型窒化物半導体層より深く、かつドレイン電極114と導通する半導体層にまで注入イオンが達する選択的イオン注入によって形成されており、n型導電層とn型不純物が注入されていないチャネル領域との接続部115に注入されているn型不純物濃度が1×1018cm−3以下である。

(もっと読む)

半導体装置

【課題】層構造の設計指針を得ることにより、窒化物半導体チャネル層としてInN(あるいはInGaN、InAlN、InAlGaN)を用いた、高性能のInN系ヘテロ構造電界効果トランジスタ(チャネル層がInN系であるヘテロ構造電界効果トランジスタ)を実現させること。

【解決手段】窒化物チャネル層半導体1の上に窒化物障壁層半導体2を重ねてなるヘテロ構造上に、ソース電極3、ゲート電極4、ドレイン電極5が配置されてなるInN系ヘテロ構造電界効果トランジスタにおいて、窒化物チャネル層半導体1としてInN、InGaN、InAlN、あるいはInAlGaNが用いられ、窒化物障壁層半導体2としてInXAl1−XN(ここに、0<X≦0.66である)が用いられていることを特徴とするInN系ヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

電界効果半導体装置及びその製造方法

【課題】ノーマリオフのHEMTを得ることが困難であった。

【解決手段】本発明に従うヘテロ接合型電界効果半導体装置は、電子走行層31と、第1及び第2の電子供給層32,33と、キャップ層34と、ソース電極8と、ドレイン電極9と、ゲート電極10と、シリコン酸化物から成る絶縁膜11と、p型金属酸化物半導体膜12とを有している。第2の電子供給層33に凹部7が形成され、この凹部7に絶縁膜11とp型金属酸化物半導体膜12とゲート電極10との積層体が配置されている。正孔濃度の高いp型金属酸化物半導体膜12はノーマリオフ特性に寄与し且つゲートリーク電流の低減に寄与する。絶縁膜11はゲートリーク電流の低減に寄与する。

(もっと読む)

1 - 20 / 44

[ Back to top ]