Fターム[5F102GR01]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 素子形成にあたり、結晶軸、面方位を選択したもの (450)

Fターム[5F102GR01]に分類される特許

1 - 20 / 450

炭化珪素半導体装置およびその製造方法

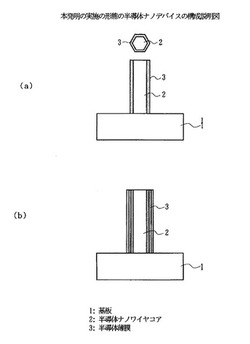

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

窒化物半導体エピタキシャル基板

【課題】オフ角を有するSi基板を用いて、反りが小さく結晶性の高い窒化物半導体基板を提供する。

【解決手段】(111)結晶方位面に対して2.0°以上6.0°以下のオフ角を有するSi基板Wと、Si基板W上に形成されAlN単結晶層20a上にAlxGa1−xN単結晶層(0<x<1)20bが積層された第一バッファ領域Aと、第一バッファ領域A上に形成され厚さが300nm以上450nm以下のAlyGa1−yN単結晶(0≦y<0.1)からなる第1単層30aと厚さが5nm以上20nm以下のAlzGa1−zN単結晶(0.9<z≦1)からなる第2単層30bとが交互に複数積層された第二バッファ領域Bと、第二バッファ領域B上に形成された窒化物半導体活性層50と、からなる窒化物半導体基板Z。

(もっと読む)

窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法

【課題】シリコン基板上に形成した、転位及びクラックの少ない窒化物半導体ウェーハ、窒化物半導体装置及び窒化物半導体結晶の成長方法を提供する。

【解決手段】実施形態によれば、シリコン基板と、その上に順次設けられた、下側歪緩和層、中間層、上側歪緩和層及び機能層と、を有する窒化物半導体ウェーハが提供される。中間層は、第1下側層と、第1ドープ層と、第1上側層と、を含む。第1下側層は、下側歪緩和層の上に設けられ、下側歪緩和層の格子定数よりも大きい格子定数を有する。第1ドープ層は、第1下側層の上に設けられ、第1下側層の格子定数以上の格子定数を有し1×1018cm−3以上1×1021cm−3未満の濃度で不純物を含有する。第1上側層は、第1ドープ層の上に設けられ、第1ドープ層の格子定数以上で第1下側層の格子定数よりも大きい格子定数を有する。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】GaNを用いた窒化物半導体装置において、電流が流れる経路に、再結晶成長などによる界面が存在することがない状態で、十分な耐圧が得られるようにする。

【解決手段】GaNからなるチャネル層(第2半導体層)101と、チャネル層101の一方の面であるN極性面に形成された第1障壁層(第1半導体層)102と、チャネル層101の他方の面であるIII族極性面に形成された第2障壁層(第3半導体層)103とを備える。第1障壁層102および第2障壁層103は、例えば、AlGaNから構成されている。また、ドレイン電極(第1電極)104が、第1障壁層102の上に形成され、ゲート電極105が、ドレイン電極104に対向して第2障壁層103の上に形成されている。ソース電極(第2電極)106は、ゲート電極105と離間して第2障壁層103の上に形成されている。

(もっと読む)

窒化物半導体構造の製造方法

【課題】平坦な表面を有し、結晶性の高い窒化物半導体下地層を、反りを抑えて、大きな成長速度で成長させることができる窒化物半導体構造の製造方法を提供する。

【解決手段】第3の窒化物半導体下地層を形成する工程において、第3の窒化物半導体下地層の成長時に単位時間当たりに供給されるV族原料ガスのモル量と単位時間当たりに供給されるIII族原料ガスのモル量との比であるV/III比を700以下とし、第3の窒化物半導体下地層の成長時の圧力を26.6kPa以上とし、第3の窒化物半導体下地層の成長速度を2.5μm/時以上とする、窒化物半導体構造の製造方法である。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】GaNを用いた縦型の電界効果トランジスタにおいて、素子の作製にコストの上昇を招くことなく、ドレイン電流密度を大きくできるようにする。

【解決手段】GaNからなるチャネル層101と、GaNより大きなバンドギャップエネルギーを有してアルミニウムを含む窒化物半導体から構成されてチャネル層101の一方の面に形成された障壁層102を備える。ここで、チャネル層101の一方の面は、N極性面とされ、他方の面はIII族極性面とされていればよい。また、チャネル層101の他方の面に形成されたドレイン電極103と、ドレイン電極103に対向して障壁層102の上に形成されたゲート電極104と、ゲート電極104と離間して障壁層102の上に形成されたソース電極105とを備える。

(もっと読む)

窒化物半導体素子の製造方法

【課題】窒化珪素層を形成した場合でも、窒化物半導体層の転移密度を低減することができるとともに、窒化物半導体層の表面モフォロジーを優れたものとすることができる窒化物半導体素子の製造方法を提供する。

【解決手段】斜めファセットを有する第2の窒化物半導体層を有機金属気相成長法により形成する工程において、有機金属気相成長装置の成長室に供給されるIII族元素ガスに対するV族元素ガスのモル流量比が240以下である窒化物半導体素子の製造方法である。

(もっと読む)

印刷可能な半導体構造、並びに関連する製造方法及び組立方法

【課題】選択された物理的寸法、形状、組成、及び、空間的配置を有する高品質印刷可能半導体素子の製造、転写、組み立てのための高歩留りの経路を与える。

【解決手段】大面積基板及び/又はフレキシブル基板を含む基板上へのミクロサイズ及び/又はナノサイズの半導体構造の配列の高精度の位置合わせ転写及び集積を行なう。また、バルクシリコンウエハ等の低コストバルク材料から印刷可能半導体素子を形成する方法、及び、広範囲の機能的な半導体デバイスを形成するための多目的で商業的に魅力的な印刷ベースの製造ブラットフォームを可能にするスマート材料処理を行う。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】薄いキャップ層を用いるも、応答速度が速く、ピンチオフ不良等のデバイス特性の劣化を抑止して安定なノーマリオフ動作を実現する信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】Si基板1上に化合物半導体積層構造2が形成され、化合物半導体積層構造2は、電子走行層2aと、電子走行層2aの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたキャップ層2dとを有しており、キャップ層2dは、電子走行層2a及び電子供給層2cと分極が同方向である第1の結晶2d1と、電子走行層2a及び電子供給層2cと分極が逆方向である第2の結晶2d2とが混在する。

(もっと読む)

窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

(もっと読む)

窒化物半導体素子及び製造方法

【課題】耐圧が高く、かつ、リーク電流が効果的に低減された窒化物半導体素子及びその製造方法を提供する。

【解決手段】ベース基板210と、ベース基板の上方に形成されたバッファ層280と、バッファ層280上に形成された活性層290と、活性層の上方に形成された少なくとも2つの電極292および294とを備え、バッファ層280は格子定数の異なる複数の窒化物半導体層を含む複合層を1層以上有し、複合層の少なくとも1層は、複数の窒化物半導体層のうち格子定数が最も大きい窒化物半導体層のキャリア領域に予め定められた濃度の炭素原子及び予め定められた濃度の酸素原子が意図的にドープされている窒化物半導体素子。

(もっと読む)

不純物濃度を選択的に減少させたIII−V族デバイス構造

【課題】HEMT及びその他の高速スイッチングデバイスにおいて、意図しない不純物のドープはを防ぎ高性能なデバイスを提供する。

【解決手段】半導体構造は、基板、基板上方の遷移体、及び遷移体上方に底面を有するIII−V族中間体を備える。半導体構造はさらに、III−V族中間体の頂面上方にIII−V族デバイス層を備える。III−V族中間体213は、前記底面211において高く、前記頂面213において低くなる形で連続的に減少された不純物濃度を有する。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】窒化物半導体を用いた電界効果トランジスタのしきい値電圧がより容易に制御できるようにする。

【解決手段】基板101の上に形成されたGaNからなる緩衝層102と、緩衝層102の上に形成されたAlGaNからなる障壁層103と、障壁層103の上に形成されたゲート電極104とを備える。また、障壁層103の上にゲート電極104を挟んでゲート電極104とは離間して形成されたソース電極105およびドレイン電極106を備える。加えて、障壁層103とゲート電極104との間に形成されたInAlNからなるキャップ層107を備える。

(もっと読む)

1 - 20 / 450

[ Back to top ]