Fターム[5F102GR06]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876)

Fターム[5F102GR06]の下位に属するFターム

不純物領域 (317)

絶縁領域(高抵抗領域を含む) (273)

エッチングストッパとなる層 (162)

Fターム[5F102GR06]に分類される特許

1 - 20 / 124

化合物半導体装置及びその製造方法

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

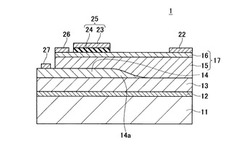

半導体装置とその製造方法

【課題】信頼性の高いヘテロ接合を有するノーマリオフ型の半導体装置を提供すること。

【解決手段】半導体装置1は金属膜22を備えている。金属膜22は、ゲート部30とドレイン電極24及び/又はソース電極26の間の半導体積層体10の表面の少なくとも一部に設けられている。金属膜22は、半導体積層体10の表面部に窒素空孔を形成することが可能な材料である。

(もっと読む)

ワイドバンドギャップ半導体デバイス

【課題】製造が容易であり、デバイス特性の変動を抑制できるワイドバンドギャップ半導体デバイスを得る。

【解決手段】SiC基板1上にAlN格子緩和層2、GaNチャネル層3、及びAlGaN電子供給層4が順に設けられている。これらは、1.42eVより広いバンドギャップを持つ半導体材料からなる。AlGaN電子供給層4に、トランジスタを含む活性領域9が設けられている。SiC基板1は、光学的な不純物又は格子欠陥により着色され、可視光領域の光を吸収する。従って、このデバイスは波長360nm〜830nmの可視光領域の光に対して不透明である。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極によるチャネルのポテンシャル制御性を大幅に向上させ、信頼性の高い所期の高耐圧及び高出力を得ることのできる化合物半導体装置を実現する。

【解決手段】AlGaN/GaN・HEMTは、Si基板1と、Si基板1の上方に形成された電子走行層2bと、電子走行層2bの上方に形成された電子供給層2cと、電子供給層2cの上方に形成されたソース電極4、ドレイン電極5及びゲート電極6とを含み構成されており、電子走行層2cは、平面視でソース電極4とドレイン電極5とを結ぶ方向と交差する方向に並ぶ複数の段差、例えば第1の段差2ca、第2の段差2cb、第3の段差2ccを有する。

(もっと読む)

化合物半導体基板

【課題】化合物半導体層全体の膜厚を抑制しつつ、半導体素子の高い性能と信頼性を両立することのできる化合物半導体基板を提供する。

【解決手段】シリコン単結晶の基板12と、基板上に形成される化合物半導体の第1の半導体層16と、第1の半導体層上に形成され、第1の半導体層よりもバンドギャップエネルギーの大きい、化合物半導体の障壁層18と、障壁層上に形成され、障壁層よりもバンドギャップエネルギーの小さい化合物半導体の第2の半導体層20と、第2の半導体層上に形成され、第2の半導体層よりもバンドギャップエネルギーの大きい化合物半導体の第3の半導体層22とを有することを特徴とする化合物半導体基板。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

テラヘルツ波素子

【課題】テラヘルツ波を発生又は検出するテラヘルツ波素子において、単色性が良いテラヘルツ波を効率良く出射する。

【解決手段】テラヘルツ波素子は、基板101の上に形成された第1の半導体層102と、第1の半導体層102の上に形成された第2の半導体層104と、第2の半導体層104の上に形成されたゲート電極106と、第2の半導体層104の上にゲート電極106を挟んで対向するように形成されたソース電極107及びドレイン電極108と、第2の半導体層104の上におけるゲート電極106とソース電極107との間及びゲート電極106とドレイン電極108との間に形成され、複数の金属膜109が周期的に配置された周期構造を有する周期金属膜109A,109Bと、ゲート電極106及び複数の金属膜109の上方に配置された第1のミラー111と、基板101の下に形成された第2のミラー112とを備えている。

(もっと読む)

ノーマリオフ型ヘテロ接合電界効果トランジスタ

【課題】p型不純物のドーピングおよびそのp型不純物の活性化を必要とすることなく、簡便かつ低コストでノーマリオフ型HFETを提供する。

【解決手段】ノーマリオフ型HFETは、厚さt1のアンドープAlxGa1−xN層(11)、この層(11)へ電気的に接続されかつ互いに隔てられて形成されたソース電極(21)とドレイン電極(22)、これらソース電極とドレイン電極との間でAlxGa1−xN層上に形成された厚さt2のアンドープAlyGa1−yN層(12)、ソース電極とドレイン電極との間においてAlyGa1−yN層の部分的領域上でメサ型に形成された厚さt3のアンドープAlzGa1−zN層(13)、およびAlzGa1−zN層上に形成されたショットキーバリア型ゲート電極(23)を含み、y>x>zおよびt1>t3>t2の条件を満たすことを特徴としている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

半導体回路

【課題】ON状態とOFF状態のコントラスト(High/Low比)が高く、消費電力が少なく、端子数および配線数が少ない回路を提供する。

【解決手段】半導体回路は、複数個のNOT回路が縦続接続され、最終段のNOT回路の出力端子と初段のNOT回路の入力端子とが接続されている。NOT回路は、ゲート11とソース13とが一体構造で形成され、ゲート10が入力端子3に接続され、ドレイン12が出力端子5に接続され、ゲート11およびソース13がグランド端子6に接続されたインプレーンダブルゲートトランジスター1と、ゲート20,21およびソース23が一体構造で形成され、ゲート20,21およびソース23がインプレーンダブルゲートトランジスター1のドレイン12に接続され、ドレイン22がバイアス端子4に接続された自己バイアス型インプレーントランジスター2とから構成される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】良好なノーマリ・オフ動作を可能とすることに加え、アバランシェ耐量が大きく、外部のダイオードを接続することを要せず、確実に安定動作を得ることができる信頼性の高い高耐圧のHEMTを得る。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成された電極用リセス2Dを、少なくとも電極用リセス2Dの底面で化合物半導体積層構造2と直接的に接するように電極材料で埋め込み、化合物半導体積層構造2とショットキー接触するフィールドプレート電極8を形成する。

(もっと読む)

テラヘルツ波素子

【課題】単色性が強く、高効率にテラヘルツ波を発生または検出することができるテラヘルツ波素子を提供する。

【解決手段】テラヘルツ波素子100は、バッファ層102と電子供給層104とのヘテロ接合を含む半導体多層構造101〜104と、半導体多層構造101〜104上に形成されたゲート電極105、ドレイン電極106およびソース電極107とを有し、ゲート電極105とヘテロ接合界面との間の静電容量は、ドレインとソースとの間を流れる電流の方向と直交する方向に周期的に、第1の静電容量と第1の静電容量の値と異なる第2の静電容量とを有している。

(もっと読む)

p型のIII族窒化物半導体層を含む半導体装置とその製造方法

【課題】p型のIII族窒化物半導体層を含む積層構造を利用して複数個の半導体装置を製造し、エッチング等して個々の半導体装置に分割すると、個々の半導体装置の側面に露出するp型のIII族窒化物半導体層の表面に沿ってリ−ク電流が流れてしまう。

【解決手段】p型のIII族窒化物半導体層8を含む積層構造の表面または裏面からp型のIII族窒化物半導体層8に達しない深さまでエッチングまたはダイシングし、残った厚みをへき開して個々の半導体装置に分割する。半導体装置の側面に露出するp型のIII族窒化物半導体層8の表面はへき開面となり、結晶欠陥が少なく、側面に沿ってリ−ク電流が流れることを防止する。

(もっと読む)

半導体素子

【課題】低オン抵抗および高信頼性を有する半導体素子を提供する。

【解決手段】半導体素子1Aは、第1導電形層11が表面に選択的に設けられた半絶縁性基板10と、前記半絶縁性基板および前記第1導電形層の上に設けられたノンドープAlXGa1−XN(0≦X<1)を含む第1半導体層15と、前記第1半導体層上に設けられたノンドープもしくは第2導電形のAlYGa1−YN(0<Y≦1、X<Y)を含む第2半導体層16とを備える。半導体素子は、前記第2導電形層11に接続された第1主電極20と、前記第2半導体層16に接続された第2主電極と21、前記第1主電極と、前記第2主電極と、のあいだの前記第2半導体層の上に設けられた制御電極30とを備える。前記第1導電形層11は、前記制御電極30の下に設けられている。

(もっと読む)

半導体装置及びその製造方法、電源装置

【課題】半導体装置において、セルフターンオンが発生しないようにし、安定した動作を実現する。

【解決手段】半導体装置を、基板1と、基板の上方に設けられ、電子走行層6及び電子供給層7を含む半導体積層構造2と、半導体積層構造の上方に設けられたゲート電極3、ソース電極4及びドレイン電極5と、ゲート電極、ソース電極及びドレイン電極の上方に設けられ、ゲート電極、ソース電極及びドレイン電極のそれぞれに接続されたゲートパッド10、ソースパッド11及びドレインパッド12と、ゲートパッド、ソースパッド及びドレインパッドの下方に設けられた導電層1とを備えるものとし、ゲートパッドとソースパッドとの間の距離を、ゲートパッドとドレインパッドとの間の距離よりも小さくする。

(もっと読む)

窒化物半導体装置

【課題】ゲート電極から染み出した金属がドレイン電極に到達することを抑制して、ドレイン−ゲート間の絶縁破壊を抑制する窒化物半導体装置を提供する。

【解決手段】ゲート電極5の直下に位置するAlGaN層22と、このAlGaN層22の直上に位置する絶縁膜30との間の界面Sに、ゲート電極5とドレイン電極1との間に位置するように、溝50を設けている。ゲート電極5から界面Sを伝ってドレイン電極1側へ染み出した金属を、溝50によって、堰き止めることができる。

(もっと読む)

化合物半導体装置

【課題】電流コラプス現象が抑制され、且つフィールドプレート電極による電界集中を緩和する効果の低下が抑制された化合物半導体装置を提供する。

【解決手段】III族窒化物半導体層と、III族窒化物半導体層上に配置された絶縁膜7と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたドレイン電極4と、III族窒化物半導体層の上面から膜厚方向に第1の距離T1の位置に絶縁膜を介して配置されたソース電極3と、ドレイン電極とソース電極間においてIII族窒化物半導体層の上面から膜厚方向に第2の距離T3の位置に絶縁膜を介して配置されたゲート電極5と、ドレイン電極とゲート電極間においてIII族窒化物半導体層の上面から膜厚方向に第1の距離T1より短い第2の距離T2の位置に絶縁膜を介して配置されたフィールドプレート電極6とを備える。

(もっと読む)

炭化珪素半導体装置

【課題】従来よりオン抵抗が低くかつ高い耐圧を有する炭化珪素半導体装置を提供する。

【解決手段】この発明に従ったJFET10は、n型基板11と、p型層2、12と、n型層13と、ソース領域15と、ドレイン領域17と、ゲート領域16とを備える。n型基板11は、{0001}面に対するオフ角が32°以上である主表面11Aを有し、炭化珪素(SiC)からなる。p型層2、12は、n型基板11の主表面11A上に形成され、導電型がp型である。n型層13は、p型層2、12上に形成され、導電型がn型である。ソース領域15およびドレイン領域17は、n型層13において、互いに間隔を隔てて形成され、導電型がn型である。ゲート領域16は、n型層13において、ソース領域15とドレイン領域17との間の領域に形成され、導電型がp型である。

(もっと読む)

半導体装置およびその製造方法

【課題】 開口部が設けられ、当該開口部に二次元電子ガスで形成されるチャネルを備える縦型半導体装置の耐圧性能を向上させることを目的とする。

【解決手段】開口部28が設けられたGaN系積層体15を備える縦型の半導体装置であって、n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を備え、開口部を覆うように電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、再成長層上に位置するゲート電極Gとを備え、ゲート電極Gは、p型GaNバリア層の厚み範囲に対応する部分を覆い、かつ開口部の底部から離れた位置の壁面内で終端している。

(もっと読む)

1 - 20 / 124

[ Back to top ]