Fターム[5F102GR08]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 半導体基体内に付加領域を設けたもの (876) | 不純物領域 (317) | ウェル領域 (42)

Fターム[5F102GR08]に分類される特許

1 - 20 / 42

トランジスタ装置及びトランジスタ装置製造方法

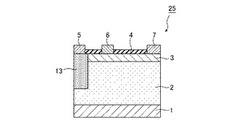

【課題】トラップの影響を低減し、過渡応答を改善するトランジスタ装置及びトランジスタ装置製造方法を提供する。

【解決手段】ソース電極5とゲート電極6との間のGaNチャネル2における一部に形成された、不純物濃度が高い領域である高不純物領域13を含み、高不純物領域13は、ゲート電極6とドレイン電極7との間より不純物濃度が高い。

(もっと読む)

窒化物半導体電界効果トランジスタ

【課題】通常の極性面上(すなわちc軸方向)に形成するエンハンスメント型の窒化物半導体電界効果トランジスタとして、高い密度のドレイン電流を実現することが可能にする。

【解決手段】窒化物半導体からなるチャネル層半導体6の上方の極性面方向に、チャネル層半導体6よりもバンドギャップの大きい窒化物半導体からなる障壁層半導体5が積層され、ゲート電極2の下方に存在する素子領域のうち少なくとも一部の素子領域を覆う第1領域21内に存在する障壁層半導体5の層厚が、第1領域21以外の素子領域を覆う第2領域22内に存在する障壁層半導体5の層厚よりも薄く形成されるか、または、第1領域21内には障壁層半導体5が存在しない状態で形成されるとともに、第2領域22内に存在する障壁層半導体5中に、障壁層半導体5よりもバンドギャップが小さい単一層の量子井戸7または多重層の多重量子井戸を挿入した量子井戸構造が形成される構造にする。

(もっと読む)

へテロ接合電界効果型トランジスタ及びその製造方法

【課題】本発明は、電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果型トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明のヘテロ接合電界効果型トランジスタは、バリア層4及びバリア層4上に形成されたキャップ層5を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして窒化物半導体層上に設けられたゲート電極10と、ゲート電極10の両側に離間して夫々設けられたドレイン電極8及びソース電極9とを備える。ゲート電極10のドレイン電極8側端面とソース電極9側端面のうち少なくともドレイン電極8側端面は、キャップ層5と少なくとも部分的に乖離しており、当該乖離部分が空隙である。

(もっと読む)

ヘテロ接合電界効果トランジスタ及びその製造方法

【課題】電流コラプスを抑制し、且つゲートリーク電流を低減するヘテロ接合電界効果トランジスタとその製造方法の提供を目的とする。

【解決手段】本発明に係るヘテロ接合電界効果トランジスタは、バリア層40及びバリア層40上に形成されたキャップ層50を含む窒化物半導体層と、前記窒化物半導体層に下部を埋没するようにして前記窒化物半導体層上に設けられたゲート電極90と、前記窒化物半導体層上に形成されたSiを含まない絶縁膜からなる表面保護膜100とを備える。

(もっと読む)

半導体装置およびその作製法

【課題】窒化物半導体を用いたヘテロ構造電界効果トランジスタにおいて、オーミック接触抵抗を大きく低減し、同時に、ソース電極2からチャネルまでの抵抗(アクセス抵抗)を大きく低減し、その結果として、高速化および低損失化(低消費電力化)が可能となる半導体装置およびその作製法提供すること。

【解決手段】ソース電極2とドレイン電極4とに、それぞれオーミック接触し、チャネル層窒化物半導体よりも小さいバンドギャップを有する再成長窒化物半導体(2)と、前記チャネル層窒化物半導体との間を、再成長組成傾斜窒化物半導体(1)を介して接続することによって、ソース電極2とチャネルとの間、および、ドレイン電極4とチャネルとの間を、それぞれ結ぶ電路中の半導体バンドギャップの不連続が解消されていることを特徴とするヘテロ構造電界効果トランジスタを構成する。

(もっと読む)

窒化物半導体装置及び窒化物半導体装置の製造方法

【課題】基板の放熱性が高くて基板に形成される窒化物半導体層の結晶欠陥が少ない窒化物半導体装置及びその製造方法を提供する。

【解決手段】

HEMT10の製造方法は、サファイア基板11の表面にGaNの薄膜12を形成する成膜工程と、薄膜12の上端からサファイア基板11の内部に達する深さの溝を形成する溝形成工程と、溝形成工程の後に、薄膜12を種結晶としてGaN層13を成長させる成長工程と、成長工程の前又は後に、サファイアよりも熱伝導性が高い高熱伝導性材料としてのAuを溝17に充填する充填工程とを備えている。

(もっと読む)

モノリシック集積複合III−V族及びIV族半導体デバイス、並びにその製造方法

【課題】単一のダイの上にIII−V族半導体デバイスをIV族半導体デバイスと共に集積する、複合デバイスの製造方法を提供する。

【解決手段】IV族半導体基板202上にIII−V族半導体本体274a,274bを形成するステップと、III−V族半導体本体にトレンチを形成し、トレンチ内にIV族半導体本体232を形成するステップとを有する。この方法は、IV族半導体本体内に少なくとも1つのIV族半導体デバイス272を製造するステップと、III−V族半導体本体内に少なくとも1つのIII−V族半導体デバイス274を製造するステップも含む。III−V族半導体本体の上面とIV族半導体本体の上面とを平坦化して、それぞれの上面をほぼ同一平面にするステップをさらに含む。一実施形態では、トレンチの側壁に隣接する、前記IV族半導体本体の欠陥領域に、少なくとも1つの受動デバイスを製造するステップをさらに含む。

(もっと読む)

集積半導体基板構造の製造方法

【課題】GaN素子およびCMOS素子の両方を備えた集積回路を製造するための改善した方法を提供する。

【解決手段】集積半導体基板構造100は、基板11と、GaNヘテロ構造20と、半導体基板層30とを備える。GaNヘテロ構造20は、第1素子エリアに存在し、少なくとも部分的に保護層8で覆われている。半導体基板層30は、CMOS素子の区画のための第2素子エリアに存在する。GaNヘテロ構造20および半導体基板層30の少なくとも1つが、基板11の少なくとも1つの溝内をエピタキシャル成長して形成され、GaNヘテロ構造20および半導体基板層30は横方向に並置される。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】オン抵抗を大幅に低減し、十分な高電圧動作且つ高出力を得ることができる信頼性の高い化合物半導体装置を実現する。

【解決手段】ソース電極12及びドレイン電極13の下方の凹部7,8を充填し、電子供給層4の上方を覆う、Siを含むn−GaN層9が形成されており、n−GaN層9は、ソース電極12の下方及びドレイン電極13下方に含まれるSiの方が、ゲート電極15の近傍に含まれるSiよりも濃度が大きくなるように、Si添加量を漸減させながら成長形成される。

(もっと読む)

ヘテロ接合電界効果トランジスタ、その製造方法

【課題】ゲート電極下の電子の走行方向が基板表面に略平行であるようにデバイス構造を改良しながらも各種弊害を解消したヘテロ接合電界効果トランジスタを提供する。

【解決手段】n型導電層は選択的にイオン注入されているシリコン(Si)などのn型不純物をアニール処理で活性化することにより形成されており、n型導電層は、イオンが200keV以上の加速エネルギーで注入されており、p型窒化物半導体層より深く、かつドレイン電極114と導通する半導体層にまで注入イオンが達する選択的イオン注入によって形成されており、n型導電層とn型不純物が注入されていないチャネル領域との接続部115に注入されているn型不純物濃度が1×1018cm−3以下である。

(もっと読む)

増幅素子

【課題】ECMのインピーダンス変換および増幅に、J−FETを入力としバイポーラトランジスタを出力とする増幅素子に、バックゲート構造のJ−FETを用いると、バックゲート−半導体基板間の容量が、増幅素子の入出力間の寄生容量(ミラー容量)となり、増幅素子の入力ロスが増大する問題に対し有効な半導体装置を提供する。

【解決手段】接地されたp型半導体基板11にp型半導体層12を積層し、p型半導体層12にn型チャネル領域22を有するJ−FETと、n型コレクタ領域33bを有するバイポーラトランジスタを設けた増幅素子とする。これにより、増幅素子の入出力間の寄生容量が発生しなくなるため、ミラー容量による入力ロスの増大を防止できる。また、J−FETのチャネル領域は、エミツタ拡散31と同時に形成できるため、IDSSSや、ピンチオフ電圧が安定し、増幅素子としての消費電流のばらつきが低減し、生産性が向上する。

(もっと読む)

横型HEMTおよび横型HEMTの製造方法

【課題】高いアバランシュブレークダイン強度を有する横型HEMTと、その製造方法を提供する。

【解決手段】基板10と、基板上に配置された、第1導電型のチヤネルとなる第1層11、少なくとも部分的に上記第1層11の上に配置された電子供給層となる第2層12を有する。さらに、上記横型HEMTは、上記第1導電型に対して相補的な第2導電型の半導体物質を有し、少なくとも部分的に上記第1層11の中に配置された第3層13を有する。このためPNダイオードが上記第1層および第3層の間で形成され、PNダイオードは横型HEMTより低いブレークダウン電圧を有することにより、HEMTを高い電界から保護することができ、HEMTの劣化を防止できる。

(もっと読む)

集積回路構造

【課題】III−V族化合物半導体を含むトランジスタとその形成方法を提供する。

【解決手段】基板20、前記基板上にあり、III族とV族元素を含む第1のIII−V族化合物半導体材料で形成されたチャネル層26、前記チャネル層の上方の高ドープ半導体層30、前記高ドープ半導体層を穿通して形成され前記高ドープ半導体層の側壁に接触したゲート誘電体50、及び前記ゲート誘電体の下部部分上のゲート電極52を含み、ゲート誘電体50が前記ゲート電極の側壁上の側壁部分を有している集積回路構造。

(もっと読む)

電界効果トランジスタおよび電界効果トランジスタ製造方法

【課題】ゲート電極材料の耐熱上の問題を克服し、ソース抵抗の低減が可能な電界効果トランジスタを提供する。

【解決手段】ゲート電極9を挟んでソース電極8、ドレイン電極10をそれぞれ形成するソース領域3、ドレイン領域6のいずれか一方または双方の領域にイオンを注入し活性化した第1の高濃度キャリア領域6と、ゲート電極9の直下に形成したチャネル領域4と第1の高濃度キャリア領域6との間の領域に、熱処理によりキャリアを拡散させた熱拡散領域7の第2の高濃度キャリア領域とを形成し、第1の高濃度キャリア領域6は、チャネル領域4と互いに隣接して形成される第2の高濃度キャリア領域7と隣接および/または一部重複し、かつ、チャネル領域4以上に深く形成した第2の高濃度キャリア領域7よりも深く形成する。第1の高濃度キャリア領域6のキャリア濃度を、チャネル領域4よりも高濃度の第2の高濃度キャリア領域7よりさらに高くする。

(もっと読む)

半導体装置とその製造方法

【課題】 転位の発生を抑制しながら、p型半導体領域に含まれるp型不純物が隣接する他の半導体領域に拡散する現象を抑制する技術を提供する。

【解決手段】 Mg(p型不純物)を含む窒化ガリウムのp型半導体領域24と、窒化ガリウムのn型半導体下領域20と、p型半導体領域24とn型半導体下領域20との間に設けられている不純物拡散抑制領域22を備えている。不純物拡散抑制領域22は、Inx1Al1-x1N(但し、0<X1<1)である。

(もっと読む)

半導体装置

【課題】ノーマリオフ特性が実現され、飽和電流値低下が生じず、ゲート電圧に対するドレイン・ソース間電流特性が良好なHEMTを実現する半導体装置を提供する。

【解決手段】第1半導体層131と、第1半導体層131の主面135上に積層され、第1半導体層131の主面135側に2DEG層137を生じさせる第2半導体層133と、第1半導体層131及び第2半導体層133と比して電子親和力χが大きい半導体材料からなり、2DEG層137と電気的に接続された第3半導体層139と、第2半導体層133及び第3半導体層139上に設けられた絶縁膜157と、第3半導体層139にオーミック接続される第1電極151と、第2半導体層133及び第3半導体層139上に絶縁膜157を介して設けられた第2電極153と、第1電極151との間に第2電極153を介在させ、2DEG層137と電気的に接続された第3電極155とを備える。

(もっと読む)

半導体装置の製造方法

【課題】 結晶成長させたp型窒化物半導体領域をエッチングすることなく、n型半導体層とp型半導体層が隣接する構造を有する半導体装置の製造方法を提供する。

【解決手段】 本半導体装置の製造方法は、n型半導体層22の表面の一部をエッチングして溝17を形成する溝形成工程と、溝17の内外に亘るn型半導体層22の表面上にp型窒化物半導層16を結晶成長させるp型窒化物半導体層形成工程と、溝形成工程でエッチングされなかった範囲のn型半導体層22の上部に位置するp型窒化物半導体層16の少なくとも一部にn型不純物を注入し、p型窒化物半導体層16の表面からn型半導体層22に達するn型領域10を形成するn型領域工程を備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】GaN系電界効果トランジスタをノーマリオフで動作させつつ、チャネルの電流密度を増加する。

【解決手段】窒素を含む3−5族化合物半導体のチャネル層と、前記チャネル層に電子を供給する電子供給層と、前記電子供給層の前記チャネル層に対向する面の反対面に形成された、窒素を含む3−5族化合物の真性またはn形の半導体層と、前記半導体層と接して形成された、または、前記半導体層との間に中間層を介して形成された制御電極と、を備えた半導体装置を提供する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】GaN系電界効果トランジスタをノーマリオフで動作させつつ、チャネルの電流密度を増加する。

【解決手段】窒素を含む3−5族化合物半導体のチャネル層と、前記チャネル層に電子を供給する電子供給層であって前記チャネル層に対向する面の反対面に溝部を有する電子供給層と、前記電子供給層の前記溝部に形成されたp形半導体層と、前記p形半導体層と接して形成された、または、前記p形半導体層との間に中間層を介して形成された制御電極と、を備えた半導体装置を提供する。

(もっと読む)

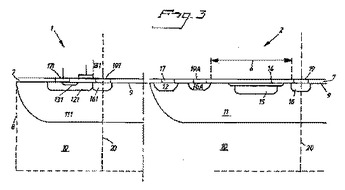

第1絶縁ゲート電界効果トランジスタが第2電界効果トランジスタと直列に接続された半導体デバイス

第1絶縁ゲート電界効果トランジスタ(1)が第2電界効果トランジスタFET(2)と直列に接続された半導体デバイスであって、前記第1絶縁ゲート電界効果トランジスタの厚くドープされたドレイン接点領域(191)へ電気的に接続されている厚くドープされたソース領域(19A)を前記第2電界効果トランジスタ(2)が有し、更に第2電界効果トランジスタ(2)のピンチ電圧Vpよりも前記第1絶縁ゲート電界効果トランジスタ(1)のブレークスルー電圧の方が高い前記半導体デバイス。  (もっと読む)

(もっと読む)

1 - 20 / 42

[ Back to top ]