Fターム[5F102GR11]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | 非対称構造 (606)

Fターム[5F102GR11]の下位に属するFターム

S−G電極間とD−G電極間の距離が異なるもの (319)

ソースとドレインの形状、不純物濃度が異なるもの (111)

Fターム[5F102GR11]に分類される特許

1 - 20 / 176

化合物半導体装置及びその製造方法

ヘテロ接合電界効果型トランジスタおよびその製造方法

電界効果トランジスタ

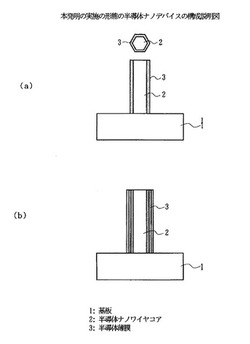

半導体ナノデバイス

【課題】 半導体ナノデバイスに関し、基板上における臨界膜厚を超えた厚さの歪のある半導体薄膜を形成してデバイス領域とする。

【解決手段】 長径が1μm未満の半導体ナノワイヤコアと、前記半導体ナノワイヤコアの側壁に形成され、前記半導体ナノワイヤコアの構成材料との歪εが1%以上異なる半導体材料からなり、且つ、膜厚t〔nm〕と歪ε〔%〕とが、

−0.720+0.0988ε−1.2<t≦−0.705+0.227ε−1.2

の関係を満たす少なくとも一層の半導体薄膜との接合界面或いは前記半導体薄膜同士の接合界面を機能領域とする。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

窒化物半導体装置

【課題】櫛型形状のソース電極とドレイン電極が交差指状に配置された電極構造を有し、各櫛形電極の先端部での電界集中が緩和された窒化物半導体装置を提供する。

【解決手段】ゲート電極5と電気的に接続され、ゲート電極5とドレイン電極4間で絶縁膜7上に配置されたゲートフィールドプレート50と、ソース電極3と電気的に接続され、絶縁膜8を介して窒化物半導体層と対向するようにゲートフィールドプレート50とドレイン電極4間の上方に配置されたソースフィールドプレート30とを備え、ゲート電極5とドレイン電極4間の距離、ゲートフィールドプレート50のドレイン側端部とゲート電極5のドレイン側端部間の距離、及びソースフィールドプレート30のドレイン側端部とゲートフィールドプレート50のドレイン側端部間の距離の少なくともいずれかが、ソース電極3とドレイン電極4の、歯部分の直線領域よりも歯部分の先端領域において長い。

(もっと読む)

半導体装置

【課題】VIAホールを高密度に形成したとしても半導体素子が割れやすくなるのを防止し、素子の形成歩留りを向上させることができる半導体装置を提供する。

【解決手段】半導体装置は、基板110と、基板の第1表面に配置され、それぞれ複数のフィンガーを有するゲート電極124、ソース電極120およびドレイン電極122と、ソース電極120の下部に配置されたVIAホールSCと、基板の第1表面とは反対側の第2表面に配置され、VIAホールを介してソース電極に接続された接地電極とを備え、VIAホールSCは、基板110を形成する化合物半導体結晶のへき開方向とは異なる方向に沿って配置される。

(もっと読む)

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

高電子移動度トランジスタ

【課題】電子移動度を低下させることなく、電子密度を高くできる高電子移動度トランジスタを提供する。

【解決手段】Si基板100上に形成されたバッファ層10と、バッファ層10上に形成されたGaN層11と、GaN層11上に形成されたAlGaN層12と、AlGaN層12内に形成されると共に、互いに間隔をあけて形成されたソース電極13とドレイン電極14と、AlGaN層12上かつソース電極13とドレイン電極14との間に形成されたゲート電極15と、ソース電極13とドレイン電極14およびゲート電極15が形成されたAlGaN層12の一部を覆うように形成された絶縁膜16とを備える。上記絶縁膜16中にCsの原子が2×1013cm−2以上存在する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

(もっと読む)

高速回復整流器構造体の装置および方法

【課題】高速回復整流器構造体の装置および方法を提供する。

【解決手段】具体的には構造体は第1のドーパントの基板(120)を含む。第1のドーパントが低濃度ドープされた第1のエピタキシャル層(140)が基板に結合されている。第1の金属層(190)が第1のエピタキシャル層に結合されている。複数のトレンチ(175)が第1のエピタキシャル層内に窪んでおり、その各々が金属層と結合している。装置は各々第2のドーパント型がドープされた複数のウェルも含み、各ウェルは対応するトレンチの下に且つ隣接して形成されている。複数の酸化物層(170)が対応するトレンチの壁および底部上に形成されている。第1のドーパントがドープされた複数のチャネル領域が、2つの対応するウェル間の第1のエピタキシャル層内に形成されている。複数のチャネル領域(150)の各々は第1のエピタキシャル層より高濃度に第1のドーパントがドープされている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置について、小型化を図りつつ、ドレイン耐圧を向上する。

【解決手段】ゲート電極20と、ゲート電極20と離間するソース電極24と、平面視でゲート電極20からみてソース電極24の反対側に位置し、かつゲート電極20と離間するドレイン電極22と、平面視でゲート電極20とドレイン電極22の間に位置し、絶縁膜26を介して半導体基板10上に設けられ、かつゲート電極20、ソース電極24およびドレイン電極22と離間する少なくとも一つのフィールドプレート電極30と、絶縁膜26中に設けられ、かつフィールドプレート電極30と半導体基板10を接続する少なくとも一つのフィールドプレートコンタクト40と、を備え、平面視でフィールドプレート電極30は、フィールドプレートコンタクト40からソース電極24側またはドレイン電極22側の少なくとも一方に延伸している。

(もっと読む)

半導体装置及びその製造方法

【課題】電極端部への電界集中を抑えるとともに、ゲート電極の変形や、ゲート−フィールドプレート間に生じる容量による特性劣化を抑える。

【解決手段】半導体装置において、第1の基板と、第1の基板表面に形成された素子領域と、素子領域と接続され、第1の基板上に形成されたゲート電極、ソース電極及びドレイン電極と、第1の基板と、第1の面で積層される第2の基板と、第2の基板を貫通し、電極上に配置されるビアホールと、ビアホール内に形成され、電極と接続される金属層と、第2の基板に設けられ、ゲート電極、ソース電極及びドレイン電極のいずれかと接続されるフィールドプレート電極と、を備える。

(もっと読む)

高電子移動度トランジスタとその製造方法

【課題】高電子移動度トランジスタにおいて、ゲート部のドレイン側端部における電界集中を緩和する。

【解決手段】高電子移動度トランジスタ10は、導電体部23と第1抵抗部R1と第2抵抗部R2を備えている。導電体部23は、ドレイン電極21とゲート部26の間に設けられている。第1抵抗部R1は、一端がドレイン電極21に電気的に接続されており、他端が導電体部23に電気的に接続されている。第2抵抗部R2は、一端がソース電極28に電気的に接続されており、他端が導電体部23に電気的に接続されている。

(もっと読む)

半導体素子および半導体素子の製造方法

【課題】バッファ層を有する半導体素子において、チャネルの基準電位を固定する半導体素子及びその製造方法を提供する。

【解決手段】基板10と、基板上に設けられ、エネルギーギャップの異なる複数種類の窒化物半導体が積層された積層体を少なくとも1層有するバッファ層20と、バッファ層上に設けられた窒化物半導体のチャネル層30と、バッファ層の側面に電気的に接続された側面電極60と、チャネル層の上方に形成され、チャネル層と電気的に接続されたチャネル電極52,56とを備える半導体素子。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】斜めイオン注入を行わなくても、外周耐圧構造を形成でき、かつ、高いドレイン耐圧が得られるようにする。

【解決手段】凹部16の底面に形成されたP型領域18と、トレンチ13内に配置されたP+型層15、および、凹部17の底面に形成されたP型領域19とによってP型リサーフ層20を構成することで電界緩和構造とする。P型リサーフ層20がトランジスタセル領域R1の周囲を囲むような構成とされることから、外周耐圧構造領域R2に延びる電界をさらにトランジスタセル領域R1の外周側に延ばすことが可能となり、ブレークダウン位置を凹部17の底面におけるN-型ドリフト層2にシフトできるため、電界緩和を行うことが可能となる。したがって、ドレイン耐圧を向上させることが可能となる。

(もっと読む)

シリコンカーバイドから製造されるモノリシックな縦型接合型電界効果トランジスタおよびショットキーバリアダイオード、および、その製造方法

【課題】縦型接合型電界効果トランジスタ(JFET)およびショットキーバリアダイオード(SBD)を備えるスイッチング素子を提供すること。

【解決手段】自己整合縦型接合型電界効果トランジスタを、エッチング注入ゲートおよび集積逆並列ショットキーバリアダイオードと組み合わせたスイッチング素子が、記載されている。ダイオードのアノードは、漂遊インダクタンスによる損失を低減するために、デバイスレベルでトランジスタのソースに接続される。SBDアノード領域におけるSiC表面は、SBDのターンオン電圧と関連するパワー損失が低減されるよう低いショットキーバリア高さを達成するために、乾式エッチングによって調整される。

(もっと読む)

パワーモジュールおよび電力変換回路

【課題】電力変換回路の性能を高める。

【解決手段】ユニット10は、半導体スイッチ素子1,2と、ダイオード3,4とを備える。ダイオード3は、半導体スイッチ素子2がオン状態である時に逆バイアスされ、半導体スイッチ素子2がオフ状態である時に導通する。ダイオード4は、半導体スイッチ素子1がオン状態である時に逆バイアスされ、半導体スイッチ素子1がオフ状態である時に導通する。ダイオード3,4は、窒化ガリウム(GaN)ダイオードまたはダイヤモンドダイオードである。ユニット10を備えるパワーモジュールは、コンバータ、インバータ等の電力変換回路に適用される。

(もっと読む)

半導体装置

【課題】ソース・ドレイン間容量の低下と、電流コラプスの抑制とを両立することが可能な半導体装置を提供すること。

【解決手段】基板10と、基板10上に形成された窒化物半導体層11と、窒化物半導体層11上に設けられたソース電極24、ゲート電極28、及びドレイン電極26と、ゲート電極28、及びゲート電極28とドレイン電極26との間の窒化物半導体層11の表面を覆う絶縁膜20と、窒化物半導体層11上であって、ゲート電極28とドレイン電極26との間に設けられたフィールドプレート30と、を具備し、ゲート電極28とドレイン電極26との間の領域の絶縁膜20上におけるフィールドプレート30の幅Wは0.1μm以上であり、フィールドプレート30のドレイン電極26側の端部と、ドレイン電極26のゲート電極28側の端部との距離L1は、3.5μm以上であり、動作周波数が4GHz以下である半導体装置である。

(もっと読む)

1 - 20 / 176

[ Back to top ]