Fターム[5F102GR15]の内容

接合型電界効果トランジスタ (42,929) | 素子構造 (2,911) | ソース、ドレインの不純物プロファイル又は形状 (109)

Fターム[5F102GR15]の下位に属するFターム

Fターム[5F102GR15]に分類される特許

1 - 20 / 97

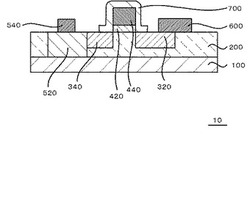

半導体装置及び半導体装置の製造方法

【課題】装置面積を増大させることなく、保護素子を有する半導体装置を提供する。

【解決手段】P型のIII族窒化物半導体からなる第1P型層200と、第1P型層200の一部上には、ゲート絶縁膜420およびゲート電極440とが設けられている。第1P型層200内のうち、ゲート電極440の両脇には、N型のソース領域340およびドレイン領域320が設けられている。また、第1P型層200の下には、N型のIII族窒化物半導体からなる第1N型層100が設けられている。基板内には、N型のIII族窒化物半導体とオーミック接続する材料からなるオーミック接続部(たとえばN型GaN層520)が、ソース領域340および第1N型層100と接するように設けられている。また、ドレイン電極600は、ドレイン領域320および第1P型層200と接するように設けられている。

(もっと読む)

半導体装置、及びその製造方法

【課題】低消費電力・低電圧動作で、高利得・低歪特性を有し、かつ低コスト化が実現可能な半導体装置とその製造方法を提供する。

【解決手段】本発明に係る半導体装置のpチャネルFET2は、ソース/ドレインを形成する高濃度p型半導体層33と、その直下層に配設された低濃度p型半導体層32と、高濃度p型半導体層33上に形成された第1電極層41と、低濃度p型半導体層32の下方に形成され、ゲートとなる高濃度n型半導体層22と、その上に形成された第2電極層42とを備える。nチャネルFET3は、ソース/ドレインを形成する高濃度n型半導体層22と、ゲートを形成する高濃度p型半導体層33と、その下方に形成された低濃度n型半導体層21と、第1電極層42と、第2電極層42とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】開口部にチャネルを備える縦型半導体装置において、高周波特性を向上することができる半導体装置およびその製造方法を提供する。

【解決手段】 n型GaN系ドリフト層4/p型GaN系バリア層6/n型GaN系コンタクト層7、を有し、開口部28は表層からn型GaN系ドリフト層内にまで届いており、該開口部を覆うように位置する電子走行層22および電子供給層26を含む再成長層27と、ソース電極Sと、ドレイン電極Dと、再成長層上に位置するゲート電極Gとを備え、ソース電極を一方の電極とし、またドレイン電極を他方の電極としてコンデンサを構成するとみて、該コンデンサの容量を低下させる容量低下構造を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 p型GaNバリア層の電位を確実に固定することでピンチオフ特性、耐圧性能の向上を安定して得ることができる縦型の半導体装置を提供する。

【解決手段】 GaN系積層体15に開口部28が設けられており、開口部の壁面を覆うように位置するチャネルを含む再成長層27と、ソース電極Sとオーミック接触するn+型ソース層8と、p型GaNバリア層6と、その間に位置するp+型GaN補助層7とを含み、p型GaNバリア6の電位をソース電位に固定するために、p+型GaN補助層7が、n+型ソース層8とトンネル接合を形成することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】低いオン抵抗を得ながら、優れた耐圧性能を持つ、縦型の半導体装置およびその製造方法を提供する。

【解決手段】開口部28はn−型GaNドリフト層4にまで届いており、開口部の壁面を覆うように位置する再成長層27と、p型GaNバリア層6と、ゲート電極Gと、ソース電極Sとを備え、チャネルが電子走行層22内の電子供給層26との界面に生じる二次元電子ガスにより形成され、p型GaNバリア層6がGaN系積層体15の表層をなし、かつソース電極Sが、再成長層27およびp型GaNバリア層6に接して位置することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、SBD、HEMT等のデバイスに逆方向電圧をかけたときの電極端部に生じる電界集中を緩和して電流コラプス、及び長期信頼性の問題を解決した半導体装置を提供する。

【解決手段】窒化物化合物半導体層を有する電子走行層11と、前記電子走行層11に形成された窒化物化合物半導体からなる電子供給層12と、前記電子供給層12上に形成された第1電極13と、前記電子供給層12上に前記第1電極13と離間して形成された第2電極14と、前記電子走行層11および前記電子供給層12を挟んで前記第1電極13に対向して形成された、前記第1電極13と同電位の第1導電体14と、前記電子走行層11および前記電子供給層12を挟んで前記第2電極14に対向して形成された、前記第2電極14と同電位の第2導電体16とを有する半導体装置1を提供する。

(もっと読む)

半導体装置およびその製造方法

【課題】 縦型GaN系半導体装置において、p型GaNバリア層による耐圧性能の向上を得ながら、オン抵抗を低くできる半導体装置を提供する。

【解決手段】 開口部28壁面に位置するチャネルを含む再成長層27と、端面が被覆されるp型バリア層6と、p型バリア層上に接するソース層7と、再成長層の上に位置するゲート電極Gと、開口部の周囲に位置するソース電極Sとを備え、ソース層が超格子構造で構成され、該超格子構造が、p型バリア層よりも小さい格子定数を持つ第1の層(a層)と、該第1の層よりも格子定数が大きい第2の層(b層)との積層体である、ことを特徴とする。

(もっと読む)

電界効果トランジスタ

【課題】 本発明は、低消費電力で動作する論理回路に応用できる電界効果トランジスタを提供することを目的とするものである。

【解決手段】 ソース電極とソース電極が接する半導体の伝導帯又は価電子帯との間に障壁を有しており、ソース電極から障壁を通して流れ込む電子又はホールをゲート電圧により調整できる構成を有することを特徴とするnチャンネル又はpチャンネルの電界効果トランジスタ。

(もっと読む)

半導体装置及びその製造方法

【課題】GaAsデバイスにおいて、空洞上に浮遊するGaAs層に素子形成を行うことにより、浮遊容量を抑え、高速化・低電力化を図ることが可能な半導体装置とその製造方法を提供する。

【解決手段】本発明の実施形態は、半導体基板11上に形成される空洞14と、空洞14上に形成されるGaAsエピタキシャル層13と、GaAsエピタキシャル層13上に形成されるゲート電極15と、それぞれGaAsエピタキシャル層13上に形成され、隣接するゲート電極15を挟むように形成される一対のソース電極16及びドレイン電極17と、を備える。

(もっと読む)

電界効果トランジスタ

【課題】電界効果トランジスタにおけるソースの高キャリア濃度化をプロセス面での負荷を抑えつつ実現する。

【解決手段】ゲート絶縁膜30は、3−5族化合物半導体のチャネル層20の第1面のゲート領域に形成される。ソースコンタクト層34およびドレインコンタクト層38は、チャネル層20の第1面にゲート領域を挟むように位置するドレイン領域およびソース領域それぞれに形成される。裏面絶縁膜50は、チャネル層20の第1面と反対側の第2面側に形成される。ソース下面電極52は、裏面絶縁膜50のチャネル層20と反対の面側に、ソースコンタクト層34と対向する領域に形成される。

(もっと読む)

化合物半導体エピタキシャルウェハ及びその製造方法

【課題】面内にわたって表面抵抗率を均一化し、得られるHEMT素子の製品抵抗のバラツキを低減した化合物半導体エピタキシャルウェハ及びその製造方法を提供する。

【解決手段】GaAsからなる基板1上に、少なくともAlGaAsからなるバッファ層3、AlGaAsからなる下部電子供給層4、GaAsもしくはInGaAsからなる電子走行層5、AlGaAsからなる上部電子供給層6、AlGaAsからなるショットキー層7、及びn型不純物を含有するGaAsからなるオーミックコンタクト層8が順次形成された化合物半導体エピタキシャルウェハ10において、オーミックコンタクト層8の外周部のキャリア濃度を中心部のキャリア濃度より高くしたものである。

(もっと読む)

半導体装置

【課題】作製プロセスに起因する特性劣化を生ぜず、ボンディングパッドの電位変化による特性変化を受け難い小型化した半導体装置を提供する。

【解決手段】半導体装置10は、アクティブ領域12と、アクティブ領域12を覆う第1の絶縁層13と、第1の絶縁層13上に形成されるフローティング導体14と、第1の絶縁層13上およびフローティング導体14上に形成される第2の絶縁層15と、第2の絶縁層17上に形成されたボンディングパッド18と、アクティブ領域12とボンディングパッド18を電気的に接続する導通ビア19,20と、を有する。

(もっと読む)

半導体トランジスタおよびその製造方法

【課題】FETの閾値電圧のばらつきのない半導体トランジスタおよびその製造方法を提供する。

【解決手段】半導体トランジスタ100は、基板1と、基板1の上方に形成された第1化合物半導体層103と、第1化合物半導体層103上に形成され、第1化合物半導体層103よりもバンドギャップの大きい第2化合物半導体層104と、第2化合物半導体層104内の少なくとも一部に、酸素がドープされた酸素ドープ領域105と、第2化合物半導体層104上に形成された第3化合物半導体層106と、第1化合物半導体層103に電気的に接続されたソース電極107およびドレイン電極109と、酸素ドープ領域105の上方に、酸素ドープ領域105に接するように形成されたゲート電極108とを有する。

(もっと読む)

半導体装置

【課題】円弧状の部分を有する電極と先端部分を有する電極での円弧状の部分と先端部分との間で流れる電流密度を均一化するために、電極の先端部分における電流集中を緩和させ、電流集中に起因する半導体装置の破壊を防止できる半導体装置を提供する。

【解決手段】半導体装置は、基板と、基板上に形成され、かつヘテロ接合に基づくキャリア走行層を有する化合物半導体層と、化合物半導体層上に形成される第1の主電極14と、化合物半導体層上において平面的に見て第1の主電極14を包囲するように形成され、かつ直線領域と円弧領域とを有する第2の主電極15と、化合物半導体層上において第1の主電極及び第2の主電極に対向するように形成された制御電極16と、を備え、第1の主電極及び第2の主電極の間に電流が流れる半導体装置であって、第1の主電極と第2の主電極の円弧領域との間に電流制限部19を設けた。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、Al2O3−Ga2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

半導体基板および半導体装置

【課題】高いしきい値電圧と低いリーク電流のノーマリーオフの半導体素子を提供する。

【解決手段】基板2の上に少なくともAlを含むIII族窒化物からなる下地層(バッファー層)3を設けた上で、III族窒化物、好ましくはGaNからなる第1の半導体層(チャネル層)4と、少なくともAlを含むIII族窒化物、好ましくはAlxGa1−xNであってx≧0.2である第2の半導体層(電子供給層)6が積層されてなる半導体層群からなるHEMT構造の半導体素子の上に、AlN−Al2O3の混晶からなる絶縁膜7を形成し、その上にゲート電極9を形成した。

(もっと読む)

III族窒化物半導体電子デバイス、III族窒化物半導体電子デバイスを作製する方法

【課題】Id―max特性低下を低減可能なIII族窒化物半導体電子デバイスが提供される。

【解決手段】III族窒化物半導体電子デバイス11では、チャネル層21はAlGaNからなると共に、バリア層23はチャネル層21より大きなバンドギャップのAlGaNからなる。チャネル層21が、GaNではなく、AlGaNからなるので、III族窒化物半導体電子デバイス11においてId―max特性低下を低減可能である。また、第1及び第2の電極17、19は、それぞれ、チャネル層21の第1及び第2の部分21a、21b上に設けられる。チャネル層21において第1の部分21aの不純物濃度が第2の部分21bの不純物濃度と同じであるから、チャネル層21における第1の部分にイオン注入が行われていない。半導体積層15に部分的にイオン注入を行っていない。このイオン注入の使用回避により、Id―max特性低下を更に低減可能である。

(もっと読む)

窒化物半導体素子

【課題】ノーマリオフ特性を有する低オン抵抗で高耐圧の窒化物半導体素子を提供する。

【解決手段】基板上に設けられた第1導電型の窒化物半導体からなる第1半導体層5と、前記第1半導体層の上に設けられ、前記第1半導体層のシートキャリア濃度と同量のシートキャリア濃度を有する第2導電型の窒化物半導体からなる第2半導体層6と、を備える。前記第2半導体層の上には、前記第2半導体層よりも禁制帯幅が広い窒化物半導体からなる第3半導体層7が設けられる。前記第2半導体層に電気的に接続された第1主電極10と、前記第1主電極と離間して設けられ、前記第2半導体層に電気的に接続された第2主電極20と、をさらに備え、前記第1主電極と前記第2主電極との間において、前記第3半導体層および前記第2半導体層を貫通して前記第1半導体層に達する第1のトレンチの内部に絶縁膜33を介して設けられた制御電極30を備える。

(もっと読む)

HFET

【課題】耐圧が高いHFET(Heterojunction−FET)を提供する。

【解決手段】ヘテロ接合16aに生じる2次元電子ガスをチャネルとするHFET10であって、第1半導体領域16と、第1半導体領域16上で第1半導体領域16とヘテロ接合している第2半導体領域18と、第2半導体領域18上に形成されたソース電極20、ドレイン電極22及びゲート電極24と、第1半導体領域16と接しており、ソース電極20と導通しているp型の第3半導体領域14を有している。ゲート電極24とドレイン電極22の間の第2半導体領域18の上面のうちの、ゲート電極24に隣接する範囲の上面は、第1表面準位密度を有する第1領域40であり、第1領域40に隣接する範囲の上面は、第1表面準位密度より低い第2表面準位密度を有する第2領域42である。第3半導体領域14は、第2領域42の下側で第1半導体領域16に接している。

(もっと読む)

半導体装置

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

1 - 20 / 97

[ Back to top ]