Fターム[5F102HA04]の内容

接合型電界効果トランジスタ (42,929) | セルフアライン (39) | ダミーゲートがマスク (10)

Fターム[5F102HA04]の下位に属するFターム

ソース、ドレイン領域形成 (5)

ソース、ドレイン電極形成 (3)

Fターム[5F102HA04]に分類される特許

1 - 2 / 2

半導体装置およびその製造方法

【課題】閾値電圧を制度良く制御することが可能な半導体装置及びその製造方法を提供する。

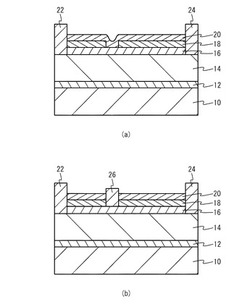

【解決手段】基板10上に、窒化物半導体からなるチャネル層14と、チャネル層14よりもバンドギャップエネルギーの大きい第1窒化物半導体層16と、を順次形成する工程と、第1窒化物半導体層16上であって、ゲート電極26を形成すべき領域にダミーゲートを形成する工程と、ダミーゲートを形成した後、第1窒化物半導体層16上のダミーゲート以外の領域に、チャネル層14のバンドギャップエネルギー以上の大きさのバンドギャップエネルギーを有する第2窒化物半導体層18を再成長する工程と、ダミーゲートを除去した後、ダミーゲートを除去した領域の第1窒化物半導体層16上にゲート電極26を形成する工程と、を有する半導体装置の製造方法。

(もっと読む)

半導体装置及びその製造方法

【課題】III族窒化物半導体から構成されるHEMTに於いて、電流コラプスの低減化と、ゲート−ドレイン間等の寄生容量の低減化とを両立化させて、利得向上による高周波化を可能にする。

【解決手段】半導体装置は、AlxInyGa1-x-yN(0≦x<1, 0≦y<1)のチャネル層2上に、AlzGa1-zN(Al組成zは0≦z≦1)の電子供給層3から成るヘテロ接合を形成したIII族窒化物半導体ヘテロ接合電界効果型トランジスタである。ゲート電極5の側面5S1,5S2から、ドレイン電極4b及びソース電極4a側に向かって、それぞれ誘電率がε1、ε2、…、εn(n≧2)(ε1>ε2>…>εn)を有するn個の絶縁膜7a,7b, …,7nが、当該順序で、ゲート電極5とドレイン電極4b間及びゲート電極5とソース電極4a間に位置する電子供給層3の表面領域上に形成されている。

(もっと読む)

1 - 2 / 2

[ Back to top ]