Fターム[5F102HC00]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778)

Fターム[5F102HC00]の下位に属するFターム

エピタキシャル成長(分子線エピ、MOCVD等) (1,679)

デルタドープ、プレーナドープ (52)

拡散(固相拡散) (29)

イオン注入 (502)

蒸着、スパッタ (562)

エッチング (1,013)

側壁の形成(被着部を凸部側面に残す) (19)

リフトオフ (344)

反転マスクの形成 (1)

熱処理(アニール) (453)

陽極酸化 (4)

多孔質化 (2)

露光 (14)

メッキ (48)

Fターム[5F102HC00]に分類される特許

1 - 20 / 56

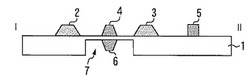

半導体装置の製造方法

【課題】設計の自由度を損なわずに、高いオン特性とオフ特性を持つ半導体装置を容易に製造する。

【解決手段】可視光に対して透明な半導体基板1の表面にソース電極2及びドレイン電極3を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間に表側ゲート電極4を形成する。半導体基板1の表面においてソース電極2とドレイン電極3との間以外の領域に合わせマーク5を形成する。半導体基板1を透過して見える合わせマーク5に基づいて半導体基板1を位置合わせして、半導体基板1の裏面において表側ゲート電極4と対向する位置に裏側ゲート電極6を形成する。

(もっと読む)

化合物半導体基板、エピタキシャル基板、化合物半導体基板の製造方法及びエピタキシャル基板の製造方法

【課題】 表面において所望の電気特性を有する化合物半導体基板、エピタキシャル基板、化合物半導体基板の製造方法及びエピタキシャル基板の製造方法を提供する。

【解決手段】 化合物半導体基板10aは、p型の化合物半導体からなる基板12と、基板12の表面12aに結合しておりp型の不純物原子を含む物質14とを備える。

(もっと読む)

大面積シリコン基板及びその他の基板上の多層III族窒化物バッファの成長

【課題】半導体基板上に第1エピタキシャル層を形成し且つ該層をエッチングして複数の分離領域を形成することを包含する方法を提供する。

【解決手段】本方法は、エッチングした第1エピタキシャル層106a上に第2エピタキシャル層106bを形成することを含む。106a,b層は少なくとも1個のIII族窒化物を含み、106a,b層は一緒になって1個のバッファ106を形成する。本方法は、更に、該バッファ上に装置層108を形成し、且つ該装置層を使用して半導体装置を製造することを包含している。106b層は、実質的に106a領域上にのみ存在する106b領域を包含することが可能である。106b層は、又、106a領域及び該基板を被覆することが可能であり、且つ106b層はエッチングするか又はしない場合がある。該装置層は106b層を形成するために使用するのと同じ操作期間中に形成することが可能である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、剥離液の残渣を除去できる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板上に開口を有するレジストマスクを形成する工程と、該基板のうち該開口により露出した部分に所定の処理を施す工程と、アリールスルホン酸を含む剥離液を用いて該レジストマスクを剥離する工程と、リンス液を用いて該剥離液の残渣を除去する工程と、該基板上に膜を形成する工程と、を備える。そして、該リンス液の溶解度パラメータは12.98から23.43までのいずれかの値であることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】GaAsを材料として用いた基板の基板厚さのばらつきを抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】GaAs基板29上に、AlGaAsからなる基板厚制御層18を形成する工程と、基板厚制御層18上にGaAsからなるバッファ層17を形成する工程と、このバッファ層17上に電界効果トランジスタ16を形成する工程と、次亜塩素酸ナトリウム水溶液を用いて、GaAs基板29を、基板厚制御層18が露出するまで研磨する工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】簡便に半導体集積回路を小領域に電気的に分離する。

【解決手段】厚さが150〜600μm程度のInP基板、GaAs基板等の化合物半導体基板1の表面に半導体集積回路2を形成し、化合物半導体基板1の裏面(半導体集積回路2が形成された表面とは反対側の面)に、直角に交わっている複数の切込溝3を設け、半導体集積回路2の表面から切込溝3の底面までの距離を50〜150μmとし、切込溝3内にAu等の金属4を埋め込み、金属4を化合物半導体基板1の裏面全面にも設ける。

(もっと読む)

半導体装置、半導体ウェハ、半導体装置の製造方法及び半導体ウェハの製造方法

【課題】ダイシング工程における半導体装置の歩留低下が抑制できる半導体ウェハ及び半導体装置を安価に提供することを目的とする。

【解決手段】基板1と、前記基板1上に形成され且つ素子形成領域2を有する化合物半導体層3と、前記素子形成領域2に形成された少なくとも1つの半導体素子と、を備える半導体装置であって、前記化合物半導体層3が、前記基板1上において選択的に形成された低結晶膜31と、前記基板1上に隣接して形成され且つ前記素子形成領域2を有する第1の化合物成長層32と、平面的に見て前記素子形成領域2を包囲するように前記低結晶膜31上に隣接して形成され且つ前記第1の化合物成長層32よりも低い結晶性を有する第2の化合物成長層33と、を備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】放熱性に優れ、製造歩留まりの向上を図ることができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】

半導体装置は、基板1の上方に設けられた化合物半導体層2,3,4と、化合物半導体層2,3,4の上方に設けられた複数のソース電極7及び複数のドレイン電極9と、化合物半導体層2,3,4を貫通し、複数のソース電極7のそれぞれに接続される複数のビア配線22と、化合物半導体層2,3,4を貫通し、複数のドレイン電極9のそれぞれに接続される複数のビア配線23と、複数のビア配線22に接続され、基板1に埋め込まれたソース共通配線18と、複数のビア配線23に接続され、基板1に埋め込まれたドレイン共通配線20とを有する。

(もっと読む)

半導体装置の製造方法

【課題】 半導体装置のビアホールにおける残渣物の残留を抑制することができ、かつ、半導体装置のデバイス特性不良、信頼性不良等を抑制することができる、半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、GaN系半導体層(11)が設けられたSiC基板(10)の第1主面の反対側の第2主面上にCuあるいはCu合金からなり部分的に開口を有するエッチングマスク(50)を形成する工程と、エッチングマスク(50)を利用したドライエッチングを実施し、底部の厚さ方向にGaN系半導体層(11)が残存したビアホールを形成する第1エッチング工程と、第1エッチング工程の後にエッチングマスク(50)を除去する除去工程と、除去工程の後に残存したGaN系半導体層(11)に対してドライエッチングを実施する第2エッチング工程と、を含む。

(もっと読む)

ヘテロ接合トランジスタ、及びヘテロ接合トランジスタを作製する方法

【課題】チャネル層内の抵抗の不均一を避けることを可能にする構造を有するヘテロ接合トランジスタを提供する。

【解決手段】半導体積層15が、半極性を示すIII族窒化物主面13a上に設けられ、半導体積層15が主面13aに到達する開口16を有する。開口16の側面16aは、III族窒化物半導体のa面に対して大きな角度を成すと共にIII族窒化物半導体のm面に対しても大きな角度を成して、III族窒化物半導体のc面に非常に近い面から構成される。開口16の側面16aの傾斜角は、m面やa面よりもc面に近い。この開口16の側面16aにドリフト層17及びチャネル層19が成長されるので、その成長中に不可避的に取り込まれる不純物量を小さくできる。これ故に、ドリフト層17及びチャネル層19における抵抗の不均一を避けることができる。

(もっと読む)

エピタキシャル基板の製造方法

【課題】インジウムを含有するIII族窒化物の膜の表面にインジウムを含有するパーティクルが付着することを抑制することができるエピタキシャル基板の製造方法及び気相成長装置を提供することを目的とする。

【解決手段】障壁層110を形成した後に、パーティクル抑制処理を行う(ステップS106)。パーティクル抑制処理は、原料の供給を停止した後に、窒素ガスの供給を継続することにより行う。

(もっと読む)

III族窒化物半導体からなるHFETの製造方法

【課題】III 族窒化物半導体からなるHFETの製造方法において、素子分離領域を容易に形成する方法を提供すること。

【解決手段】i−AlGaN層12表面側からレーザーを照射して、HFETとして動作させる素子領域を囲うようにして溝15を形成する(図2(c))。溝15の深さは、i−AlGaN層12表面からi−GaN層11に達する深さとする。この溝15によってi−AlGaN層12が取り除かれたため、この取り除かれた領域において2次元電子ガス層が消滅する。その結果、HFETとして動作させる素子領域は、溝15による素子分離領域によって電気的に分離される。

(もっと読む)

トランジスタ実装体及びその製造方法

【課題】チャネル抵抗を大幅に低減した電界効果トランジスタ実装体を実現できるようにする。

【解決手段】トランジスタ実装体の製造方法は、トランジスタ100を形成する工程(a)と、形成基板101を研磨する工程(b)と、形成基板101を研磨したトランジスタ100を保持基板200に固定する工程(c)とを備えている。工程(a)は、形成基板101の主面上に第1の半導体層及び該第1の半導体層よりもバンドギャップが大きい第2の半導体層を順次形成する。工程(b)は、形成基板101における主面と反対側の面を研磨する。工程(c)は、形成基板101の反りが小さくなる方向の応力を形成基板101に印加した状態でトランジスタ100を保持基板200の上に固定する。

(もっと読む)

III族窒化物基板、それを備える半導体デバイス、及び、表面処理されたIII族窒化物基板を製造する方法

【課題】 安定した表面を有するIII族窒化物基板を提供する。

【解決手段】 一実施形態に係るIII族窒化物基板は、表面層を有している。当該表面層は、3at.%の〜25at.%の炭素を含み、且つ、5×1010原子/cm2〜200×1010原子/cm2のp型金属元素を含んでいる。このIII族窒化物基板は、安定した表面を有するものとなる。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

高周波用半導体素子、高周波用半導体素子形成用のエピタキシャル基板、および高周波用半導体素子形成用エピタキシャル基板の作製方法

【課題】コストメリットがあり、かつ、特性の優れた高周波動作用の半導体素子を実現できるエピタキシャル基板を提供する。

【解決手段】導電性を有するSiCからなる基材の上に、バナジウムをドープすることによって比抵抗が1×106Ωcm以上の絶縁性を有するSiCからなる絶縁層を形成して、下地基板を得る。該下地基板の上に、AlNからなるバッファ層と、GaNからなるチャネル層と、AlxInyGazN(x+y+z=1)からなる障壁層とをエピタキシャル形成する。

(もっと読む)

薄膜半導体層の形成方法

【課題】 半導体層の表面に、その半導体層よりも非常にキャリア濃度の大きい半導体層を形成する高キャリア濃度の薄膜半導体層の形成方法を提供する。

【解決手段】 半導体層1表面の自然酸化膜または250℃以下の低温で生成した酸化膜4を還元して形成される活性化した金属元素と結合させることにより、半導体層1よりも高キャリア濃度で、かつ、バンドギャップが前記半導体層より大きい薄膜化合物半導体層2を形成する。この上に、SiN:Hからなる保護層3を設けることが薄膜を保護するために好ましい。

(もっと読む)

化合物半導体装置およびその製造方法

【課題】耐湿性を向上することのできる化合物半導体装置およびその製造方法を提供する。

【解決手段】化合物半導体装置は、オーミック電極OMEa〜OMEdと、絶縁膜ILと、金を含む配線IC1a〜IC1dと、金を含む配線IC2a〜IC2dとを備えている。絶縁膜ILはオーミック電極OMEa〜OMEdの一部上に形成されている。配線IC1a〜IC1dは、オーミック電極OMEa〜OMEd上で絶縁膜ILが形成されていない部分であって、絶縁膜ILの側面に接触する位置に形成されている。配線IC2a〜IC2dは、絶縁膜IL上および配線IC1a〜IC1d上に形成されている。

(もっと読む)

ワイドバンドギャップ半導体装置

【課題】JFETが形成されるセル領域とダイオード形成領域との間の絶縁耐圧を向上でき、耐圧の最適設計が行える構造のSiC半導体装置を提供する。

【解決手段】電界緩和領域R3に備えたp型領域9bとn型領域8bとにより構成されるPN分離部により、セル領域R1とダイオード形成領域R2の間の素子分離を行う。これにより、トレンチ内に酸化膜を配置して素子分離を行う場合と比べて、素子分離用の酸化膜が絶縁破壊されることが無いため、JFETが形成されるセル領域R1とダイオード形成領域R2との間の絶縁耐圧を向上できる。このため、素子分離に酸化膜を用いる場合と比べて耐圧の最適設計を行うことが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】ビアホールの形成に関連する歩留まりの低下を抑制し、また、スループットを向上することができる半導体装置の製造方法を提供する。

【解決手段】絶縁性基板1上にGaN層2及びn型AlGaN層3を形成し、その後、ゲート電極4g、ソース電極4s及びドレイン電極4dを形成する。次に、ソース電極4s、GaN層2及びn型AlGaN層3に、少なくとも絶縁性基板1の表面まで到達する開口部6を形成する。次いで、開口部6内にNi層8を形成する。その後、Ni層8をエッチングストッパとするドライエッチングを高速で行うことにより、絶縁性基板1に、その裏面側からNi層8まで到達するビアホール1sを、冷却等によりその側壁に化合物膜19を堆積させながら形成する。そして、ビアホール1s内から絶縁性基板1の裏面にわたってビア配線16を形成する。

(もっと読む)

1 - 20 / 56

[ Back to top ]