Fターム[5F102HC15]の内容

接合型電界効果トランジスタ (42,929) | 個別プロセス (4,778) | エッチング (1,013)

Fターム[5F102HC15]の下位に属するFターム

異方性エッチング、方向性エッチング (113)

オーバーエッチング、サイドエッチングの利用 (46)

Fターム[5F102HC15]に分類される特許

1 - 20 / 854

電界効果トランジスタ

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

グラフェン構造の製造方法及びこれを用いた半導体装置の製造方法

【課題】所望の位置にグラフェン膜を有するグラフェン構造及びこれを用いた半導体装置を提供する。

【解決手段】所定の基材3上において、炭素含有層4と、少なくともケイ素を含む炭素化合物層5とを順次に積層し、その上に絶縁膜層6を形成した後、絶縁膜層の一部をエッチングにより取り除いた基板に対してアニーリングを実施し、絶縁膜の除去部にのみグラフェン膜7を形成したグラフェン構造1を形成し、これを用いて表面にショットキー電極8、およびオーミック電極9,10を形成させて半導体装置2を作製する。

(もっと読む)

電極構造体、それを備える窒化ガリウム系の半導体素子及びそれらの製造方法

【課題】電極構造体、それを備える窒化ガリウム系の半導体素子及びそれらの製造方法を提供する。

【解決手段】GaN系の半導体層GL10と、GaN系の半導体層上に備えられた電極構造体500A,500Bと、を備え、電極構造体500A,500Bは、導電物質を含む電極要素50A、50Bと、電極要素50A,50BとGaN系の半導体層200との間に備えられた拡散層5A、5Bと、を備え、拡散層5A,5Bは、n型ドーパントを含み、n型ドーパントは、4族元素を含み、拡散層と接触したGaN系の半導体層200の領域は、n型ドーパント(例えば、4族元素)でドーピングされる窒化ガリウム系の半導体素子である。

(もっと読む)

集積型半導体装置

【課題】 従来に比べて小型で、素子機能部間で、高い周波数の信号を高精度に伝送することができる集積型半導体装置を提供する。

【解決手段】

サファイア単結晶基板10の一方主面10A上に配置された第1素子機能部26と、一方主面上10Aに配置された第1アンテナ部23と、他方主面10Bに配置された第2素子機能部36と、他方主面10B上に配置された第2アンテナ部33とを備え、第1素子機能部26が第1アンテナ部23に送信用電気信号を送り、第1アンテナ部23が送信用電気信号に応じた電波を発信し、第2アンテナ部33がサファイア単結晶基板10を透過した電波を受信することで、高い周波数の信号を基板の上下面で高精度に処理することができる。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】低周波雑音が低減されるとともに、素子面積の小さい半導体装置及びその製造方法を製造コストを増大させずに提供する。

【解決手段】半導体装置は、第1導電型の下部ゲート領域4と、第2導電型のチャネル領域3と、第1導電型の上部ゲート領域2と、チャネル領域3の両側に位置する第2導電型のソース及びドレイン領域8と、上部ゲート領域2上に形成されたゲート電極6と、ゲート電極6の両側面上に形成されたサイドウォールスペーサ7とを有するJFET70を備える。上部ゲート領域2とソース及びドレイン領域8とは、チャネル領域3のうちサイドウォールスペーサ7の下に位置する部分を挟んで互いに離間しており、ソース及びドレイン領域8は、ゲート長方向におけるゲート電極6の両側方であってサイドウォールスペーサ7の外側を含む領域に形成されている。

(もっと読む)

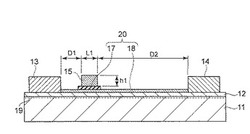

半導体装置および半導体装置の製造方法

【課題】性能の劣化を抑制することができる半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置10は、半導体層12、絶縁膜17、ゲート電極22、ドレイン電極19およびソース電極20、を具備する。半導体層12は、半絶縁性半導体基板11上に形成され、表面に、側壁が傾いたテーパ状のリセス領域18を有する。半導体層12は、活性層14を含む。絶縁膜17は、半導体層12上に形成されたものであり、リセス領域18を全て露出する貫通孔21を有する。貫通孔21は、側壁がリセス領域18の側壁の傾き角θ1より小さい角度θ2で傾いたテーパ状である。ゲート電極22は、リセス領域18および貫通孔21を埋めるように形成されたものである。ドレイン電極19およびソース電極20は、半導体層12上のうち、リセス領域18を挟む位置に形成されたものである。

(もっと読む)

半導体装置

【課題】耐圧を向上させることができる半導体装置を提供する。

【解決手段】半導体装置10は、ソース領域12a、複数の帯状のドレイン領域12b、チャネル領域、ソース電極16、ドレイン電極15、およびゲート電極17を具備する。ソース領域12aは、化合物半導体層11上に形成された平面状の領域である。複数の帯状のドレイン領域12bは、化合物半導体層11上に、互いに電気的に分離されるように形成される。チャネル領域は、ソース領域12aの一辺に接し、かつソース領域12aと複数のドレイン領域12bとの間に、互いに電気的に分離されるように形成される。ソース電極16は、ソース領域12a上の少なくとも一部に形成される。ドレイン電極15は、複数のドレイン領域12bに電気的に接続されるように形成される。ゲート電極17は、複数のチャネル領域に電気的に接続されるように形成される。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】閾値電圧のばらつきを低減できる炭化珪素半導体装置を提供する。

【解決手段】炭化珪素半導体装置10は、基板11と、基板11上に設けられ、主表面13Aと、主表面13Aと交差する厚さ方向とを有する炭化珪素層4とを含む。炭化珪素層4は、チャネル層7と、ソース領域15と、ドレイン領域17と、ソース領域15とドレイン領域17との間において、ゲート領域16Rとを含む。ゲート領域16Rはチャネル層7に対して、第1の導電型と異なる第2の導電型を有するようにエピタキシャル成長されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電極と化合物半導体層との界面に電極材料が到達することを抑止し、ゲート特性の劣化を防止した信頼性の高い高耐圧の化合物半導体装置を提供する。

【解決手段】化合物半導体積層構造2と、化合物半導体積層構造2上に形成され、貫通口6aを有するパッシベーション膜6と、貫通口6aを埋め込むようにパッシベーション膜6上に形成されたゲート電極7とを有しており、ゲート電極7は、相異なる結晶配列の結晶粒界101が形成されており、結晶粒界101の起点が貫通口6aから離間したパッシベーション膜6の平坦面上に位置する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、電極端における電界集中を緩和してデバイス特性の劣化を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を提供する。

【解決手段】HEMTは、SiC基板1上に、化合物半導体層2と、開口6bを有し、化合物半導体層2上を覆う、窒化珪素(SiN)の保護膜6と、開口6bを埋め込むように化合物半導体層2上に形成されたゲート電極7とを有しており、保護膜6は、その下層部分6aが開口6bの側面から張り出した張出部6cが形成されている。

(もっと読む)

化合物半導体装置の製造方法

【課題】化合物半導体積層構造上の絶縁膜に所期の微細な開口を形成するも、リーク電流を抑止した信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2上にパッシベーション膜6を形成し、パッシベーション膜6の電極形成予定位置をドライエッチングにより薄化し、パッシベーション膜6の薄化された部位6aをウェットエッチングにより貫通して開口6bを形成し、この開口6bを電極材料で埋め込むように、パッシベーション膜6上にゲート電極7を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】第1の極性を有する第1の化合物半導体層と共にこれと逆極性(第2の極性)の第2の化合物半導体層を用い、化合物半導体層の再成長をすることなく、第2の極性に対応した導電型の含有量が実効的に、容易且つ確実に所期に制御された、複雑な動作を可能とする信頼性の高い高耐圧の化合物半導体装置を得る。

【解決手段】第1の極性を有する電子走行層2bと、電子走行層2bの上方に形成された第2の極性を有するp型キャップ層2eと、p型キャップ層2e上に形成された第1の極性を有するn型キャップ層2fとを有しており、n型キャップ層2fは、厚みの異なる部位2fa,2fbを有する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】動作電圧の高電圧化を図るも、デバイス特性の劣化(化学的・物理的変化)を確実に抑止し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】本発明による化合物半導体装置では、化合物半導体層2上を均質な同一材料(ここではSiN)からなり誘電率が一様な第1の保護膜6が覆い、第1の保護膜6の開口6aの一端部分に酸素を含有する保護部、ここでは当該一端部分を覆う酸化膜である第2の保護膜7aが形成されており、開口6aを埋め込み第2の保護膜7aを包含するオーバーハング形状のゲート電極8が形成される。

(もっと読む)

窒化物半導体装置およびその製造方法

【課題】ノーマリオフ型のHEMT構造を有し、かつ優れたデバイス特性を有する窒化物半導体装置およびその製造方法を提供する。

【解決手段】窒化物半導体装置は、窒化物半導体からなる電子走行層3と、電子走行層3に積層され、電子走行層3とはAl組成が異なり、Alを含む窒化物半導体からなる電子供給層4と、電子供給層4と電子走行層3との界面に連続する界面を有し、電子走行層3上に形成された酸化膜11と、酸化膜11を挟んで電子走行層3に対向するゲート電極8とを含む。

(もっと読む)

窒化物半導体電子デバイス、窒化物半導体電子デバイスを作製する方法

【課題】チャネルリークを低減可能な窒化物半導体電子デバイスが提供される。

【解決手段】

【0097】ヘテロ接合トランジスタ11によれば、電流ブロック層27はp導電性を有する。ドープ半導体層17が開口部16の側面16aに設けられると共にドープ半導体層17が電流ブロック層27とチャネル層19との間に設けられるので、チャネル層19が、エッチングの際に開口部16の側面16aに形成されている可能性があるドナー性欠陥を含む半導体に直接に接触することがない。また、ドープ半導体層17は、電流ブロック層27とチャネル層19との間に設けられると共にチャネル層19はキャリア供給層21とドープ半導体層17との間に設けられるので、ドープ半導体層17の追加により、チャネル層19及びキャリア供給層21の配列は変更されることがない。

(もっと読む)

1 - 20 / 854

[ Back to top ]