Fターム[5F103AA04]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出方法 (899) | 蒸着 (423) | 分子ビーム(MBE)、原子ビーム (251)

Fターム[5F103AA04]の下位に属するFターム

有機金属分子ビーム(MOMBE) (11)

Fターム[5F103AA04]に分類される特許

181 - 200 / 240

半導体作製装置および半導体作製方法

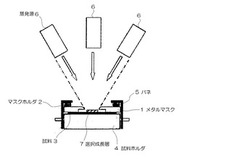

【課題】真空雰囲気下において脱着可能なメタルマスクを用いて、半導体基板上に半導体層を選択的に再現性よく形成することが可能な半導体作製装置を提供する。

【解決手段】半導体基板が搭載される試料ホルダと、半導体基板に選択的に結晶を成長させるための少なくとも1つ以上の第1の開口を有するマスクと、半導体基板およびマスクを試料ホルダとの間に挟み、試料ホルダと組み合わされるマスクホルダと、マスクとマスクホルダとの間に設けられた弾性体とを有する構成である。

(もっと読む)

III族窒化物化合物半導体積層構造体およびその成長方法

【課題】MBEやスパッタなどのラジカル化、プラズマ化または原子化された窒素源を用いたIII族窒化物半導体層の成膜法において、ドーパント元素の反応を抑制し、効率良くドーパントをドーピングする方法を提供すること。

【解決手段】ドーパント元素のみを供給するプロセスと、III族元素を含む化合物と窒素原料を同時に供給するプロセスを交互に繰り返すことからなる第一の工程を含む、ラジカル化、プラズマ化または原子化された窒素源を用いたIII族窒化物化合物半導体層の成長方法。

(もっと読む)

III−V/II−VI半導体インターフェイス製造法

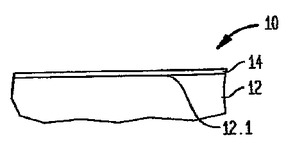

【課題】III−V/II−VI半導体インターフェイスを再現的に製造する。

【解決手段】III族元素ソース(68、170)、II族元素ソース(72、92’)、V族元素ソース(70、172)、及びVI族元素ソースを含む分子線エピタキシー(MBE)装置(50、150)を準備する。III−V半導体表面を有する基板(12)をMBE装置(50、150)内に位置決めする。基板(12)を次にIII−V半導体成長に適切な温度まで加熱し、結晶質III−V半導体バッファ層(14)を成長させる。基板の温度を交互分子線エピタキシーによってII−VI半導体成長に適切な温度まで調整し、結晶質II−VI半導体バッファ層(16)をIII−Vバッファ層上に成長させる。II族及びVI族ソースを操作して、III−Vバッファ層をVI族元素フラックスに暴露する前にII族元素フラックスに暴露させる。

(もっと読む)

ZnO系半導体素子

【課題】積層側の主面がc軸方向を向いているMgZnO基板上に平坦なZnO系半導体層を成長させることができるZnO系半導体素子を提供する。

【解決手段】+C面(0001)が少なくともm軸方向に傾斜した面を主面とするMgxZn1−xO(0≦x<1)基板1上に、ZnO系半導体層2〜6がエピタキシャル成長されている。そして、ZnO系半導体層6上にはp電極10が、MgxZn1−xO基板1の下側にはn電極9が形成されている。このようにして、MgxZn1−xO基板1の表面に、m軸方向に並ぶ規則的なステップを形成することで、ステップバンチングと呼ばれる現象を防ぎ、基板1上に積層される半導体層の膜の平坦性を向上させることができる。

(もっと読む)

半導体発光素子及びその製造方法

【課題】III族窒化物半導体を有する半導体発光素子において、動作電圧を低減するとともに発光効率を向上することが可能な技術を提供する。

【解決手段】n型III族窒化物半導体から成るn型基板1上には、n型クラッド層2と、n型光ガイド層3と、不純物がドーピングされていない多重量子井戸(MQW)活性層4と、p型電子障壁層5と、p型光ガイド層6と、p型クラッド層7と、p型コンタクト層8とがこの順で積層されている。p型電子障壁層5はp型Alx2Ga(1-x2)N(0<x2<1)から成り、p型クラッド層7はp型Alx3Ga(1-x3)N(0<x3<1)から成り、p型コンタクト層8はp型GaNから成る。p型電子障壁層5、p型クラッド層7及びp型コンタクト層8はそれぞれp型ドーパントとしてベリリウムを含んでいる。

(もっと読む)

pn接合ダイオード及びpn接合ダイオードの製造方法

【課題】GaNナノコラムから成るパワーデバイス用のpn接合ダイオードの提供を目的とする。

【解決手段】パワーデバイス用のpn接合ダイオード1aであって、第1電極4aと、第1電極4aの表面に立設されており第1導電型を示す複数の第1ナノコラム部6aと、複数の第1ナノコラム部6aの各端部に設けられており第2導電型を示す複数の第2ナノコラム部8aと、複数の第2ナノコラム部8a上に設けられており第2導電型を示す半導体部12aと、半導体部12a上に設けられた第2電極14aとを備え、第1ナノコラム部6a及び第2ナノコラム部8aは、GaNから成る。

(もっと読む)

酸化物半導体素子およびその製造方法

【課題】良好なpn接合を容易に形成することが可能なZnO系の酸化物半導体素子を提供する。

【解決手段】この酸化物半導体素子では、ZnOからなるn型の単結晶基板1の上面に、ZnOからなるp型の多結晶薄膜2が形成されている。また、n型の単結晶基板1の下面には、Alからなる電極8が形成されており、p型の多結晶薄膜2の上面には、Auからなる電極9が形成されている。

(もっと読む)

n型AlN結晶及びその製造方法

【課題】生産性とキャリア濃度が向上し、低抵抗n型AlN半導体結晶を得ることを目的とし、短波長発光素子やパワーデバイスを実現することを目的とする。

【解決手段】本発明によれば、AlN結晶のAl原子の一部を、IIIa族元素(Sc,Y,

La等)又は/及びIIIb族元素(B,Ga,In等)で置換し、隣接する窒素(N)1原

子を酸素(O)原子で置換することにより、浅い不純物準位が形成され、低抵抗n型AlN結晶を得ることができる。特にIIIa族元素又は/及びIIIb族元素の合計濃度(C3A)が1×1018cm-3以上であり、O濃度(Co)が、0.01C3A<Co<1.5C3Aである

ことが好ましい。またAlN結晶の製造方法としては、CVD法、MBE法や昇華法等公知の方法に採用できる。

(もっと読む)

半導体製造方法

本発明はIII−V族半導体の製造方法に関するものである。本発明によれば、前記方法は、電子アクセプタであるp型ドーパントで、原子価xが0と1の間に含まれる数を表す、一般式AlxGa1-xNの半導体をドーピングする、少なくとも一つのドーピング過程と、価電子帯の構造を変えることのできる共ドーパントによる共ドーピング過程とから成る。本発明は、半導体、ならびに電子産業または光電子産業におけるその使用にも関するものである。本発明はさらに、かかる半導体を使用するデバイスならびにダイオードに関するものである。 (もっと読む)

単結晶基板上にエピタキシャル成長したグラフェン層を含むデバイス

電子デバイスは、物質の主表面に単結晶領域を含む物質を含む。単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有し、グラフェンの少なくとも1つのエピタキシャル層がこの単結晶領域に配置される。現在好ましい実施形態では、単結晶領域は多層の六方晶BNを含む。このような電子デバイスの作製方法は、物質の主表面に単結晶領域を含む物質を提供し、単結晶領域は、グラフェンと実質的に格子整合している六方晶格子を有するステップ(a)と、この領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップ(b)を含む。現在好ましい実施形態では、ステップ(a)は、グラファイトの単結晶基板を提供するステップ(a1)と、基板に多層の単結晶六方晶BNをエピタキシャル形成するステップ(a2)とをさらに含む。六方晶BN層はグラフェンと実質的に格子整合した表面領域を有し、ステップ(b)は六方晶BN層の表面領域に少なくとも1つのグラフェン層をエピタキシャル形成するステップを含む。FETへの応用が説明されている。  (もっと読む)

(もっと読む)

原料物質とターゲットとの間の透視線を除去する坩堝

ターゲット基材上に堆積される物質を加熱するための坩堝は、原料物質を含むように構成されている胴部、胴部の第1の端部に形成された基部、および胴部の第2の端部に形成された放出オリフィスを含む。坩堝は、加熱された原料物質が放出オリフィスを通って通過する前に、中間オリフィスを通過し、そして少なくとも1回坩堝胴部の内側表面に衝突するように、少なくとも配置されかつ構成されている1つの中間オリフィスをさらに含む。  (もっと読む)

(もっと読む)

珪素用分子線セル坩堝

【課題】分子線セル坩堝にパイロリティックカーボンを被覆することにより、耐久性等に優れた珪素用分子線セル坩堝を提供する。

【解決手段】珪素用分子線セル坩堝は、グラファイト製の外管1と、パイロリティックカーボン4が被覆されたグラファイト製の内管とから構成された二重管である。前記内管は、開口管の上部3と、片閉口管の下部2とから構成され、この下部2は、下部2の深さdと内径D4の比が1以下であり、熱化学気相蒸着法によりパイロリティックカーボン4が被覆されている。

(もっと読む)

パージセル

【課題】 酸化物、窒化物、塩化物、フッ化物などの化合物の薄膜を分子線エピタキシー装置で作製する場合、気体材料がチャンバ内に雰囲気ガスとして残留し、他方の材料の分子線セルのるつぼに進入し、気体材料との化合物を作る。化合物になった分は材料の損失となる。材料損失が大きいと、原料の補填のためにたびたび超高真空チャンバを大気圧に戻さなければならず作業能率が悪くなる。

【解決手段】 るつぼ底部または上部に到るようにパージガス導入管を設け、パージガス導入管を通して、不活性ガスをるつぼ内へ吹き込み雰囲気ガスがるつぼ内の材料と接触しないように遮断する。

(もっと読む)

高絶縁性単結晶窒化ガリウム薄膜を有する半導体デバイス

【課題】 真性に近い単結晶GaN膜を有し、かつこの膜をn形又はp形に選択的にドー

プした半導体デバイスを提供する。

【解決手段】 次の要素を有する半導体デバイス:基板であって、この基板は、(100)シリコン、(111)シリコン、(0001)サファイア、(11−20)サファイア、(1−102)サファイア、(111)ヒ化ガリウム、(100)ヒ化ガリウム、酸化マグネシウム、酸化亜鉛、および炭化シリコンからなる群から選択される物質からなる;約200Å〜約500Åの厚さを有する非単結晶バッファ層であって、このバッファ層は前記基板の上に成長した第一の物質を含み、この第一の物質は窒化ガリウムを含む;および前記バッファ層の上に成長した第一の成長層であって、この第一の成長層は窒化ガリウムと第一のドープ物質を含む。

(もっと読む)

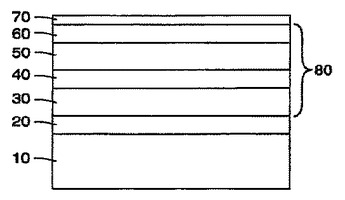

InP基板上のII−VI/III−V層状構造体

InP基板並びにII−VI及びIII−V材料の交番層を含む層状構造体が提供される。II−VI及びIII−V材料の交番層は、典型的にはInP基板に格子整合しているか又はシュードモルフィックである。典型的には、II−VI材料は、CdZnSe、CdMgZnSe、BeZnTe、又はBeMgZnTe合金から選択され、及び最も典型的にはCdxZn1−xSeであり、ここでxは0.55〜0.57である。典型的には、III−V材料は、InAlAs又はAlInGaAs合金から選択され、及び最も典型的には、InP又はInyAl1−yAsであり、ここでyは0.53〜0.57である。層状構造体は、1以上の分布ブラッグ反射器(DBR)を形成することができる。別の態様では、本発明は、InP基板及びエピタキシャル半導体材料の15層対以下を含む95%以上の反射率を有する分布ブラッグ反射器(DBR)を含む層状構造体を提供する。別の態様では、本発明は、層状構造体を含むレーザー又は光検知器を提供する。  (もっと読む)

(もっと読む)

分子線エピタキシャル装置および分子線エピタキシャル方法

【課題】成膜時間に関係なく一定の成膜レートを維持することのできるMBE装置等を提供する。

【解決手段】本発明のMBE装置100は、分子線発生部10a・10bと、真空計14a・14bと、光源ユニット6と受光ユニット7とを有する原子吸光式成膜モニタ8と、分子線発生部10a・10bの温度を制御する温度制御演算器13とを備えている。温度制御演算器13は、原子吸光式成膜モニタ8の測定結果が、真空計14a・14bの測定結果から算出した分子線源の残量より算出した原子吸光式成膜モニタ8の制御目標値となるように、分子線発生部10a・10bの温度を制御する。

(もっと読む)

酸化ガリウム単結晶複合体の製造方法、及びこれを用いた窒化物半導体膜の製造方法

【課題】最表面が立方晶窒化ガリウムからなる窒化ガリウム層又は最表面が六方晶窒化ガリウムからなる窒化ガリウム層を表層部に有した酸化ガリウム単結晶複合体の選択的製造方法、及び窒化物半導体膜の製造方法を提供する。

【解決手段】酸化ガリウム単結晶からなる基板の表層部に窒化ガリウム層を有する酸化ガリウム単結晶複合体の製造方法であって、上記基板の表面を窒素プラズマで窒化処理して窒化ガリウム層を形成する際に窒化処理の時間を制御することで、反射高速電子線回折によって測定される窒化ガリウム層の最表面が立方晶窒化ガリウムからなる窒化ガリウム層又は六方晶窒化ガリウムからなる窒化ガリウム層を選択的に製造する酸化ガリウム単結晶複合体の製造方法、及びこの複合体の表面に窒化物半導体膜を成長させる窒化物半導体膜の製造方法である。

(もっと読む)

鉄シリサイド層の製造方法並びに半導体基板及び光半導体装置

【課題】鉄シリサイド層の製造方法並びに半導体基板及び光半導体装置において、β−FeSi2の平坦で良質な連続膜を形成すること及び高キャリア移動度を得ること。

【解決手段】結晶面(001)を表面に有するSi基板1上にβ−FeSi2の鉄シリサイド層4bを成膜する方法であって、前記Si基板上に設けられたSiGe層上に、直接又は歪みSi層を介して前記鉄シリサイド層をエピタキシャル成長する鉄シリサイド層形成工程を有し、該鉄シリサイド層形成工程は、400℃以上940℃以下の成膜温度でFe原料とSi原料とを同時に供給して前記鉄シリサイド層の少なくとも一部を成膜する高温成膜工程を有する。

(もっと読む)

半導体結晶成長方法および半導体結晶成長装置

【課題】 半導体結晶成長処理されるべき基板を保持する基板ホルダが、大気に曝されることを防止し、基板ホルダに付着する堆積物を除去することによって、基板ホルダおよび堆積物が半導体結晶を成長させる際の酸素汚染源となることを防止し、特性に優れた半導体結晶を得る。

【解決手段】 半導体結晶の成長が完了した基板27の取外された基板ホルダ28が、基板導入室22の所定位置から取出されるとき、半導体結晶成長の過程において基板ホルダ28に付着した堆積物を基板ホルダ処理室26で除去するとき、および堆積物が除去された基板ホルダ28を基板導入室22の所定位置にセッティングするとき、のいずれのときにおいても、基板ホルダ28は、不活性ガス雰囲気または真空雰囲気中で取り扱われる。

(もっと読む)

ZnO結晶またはZnO系半導体化合物結晶の製造方法、及びZnO系発光素子の製造方法

【課題】 活性化率の高いZnO結晶、またはZnO系半導体化合物結晶を含むZnO系発光素子を製造する方法を提供する。

【解決手段】 (a)Zn極性面を備える基板のZn極性面上に、n型ZnOバッファ層を形成する。(b)n型ZnOバッファ層の表面上に、n型ZnO層を形成する。(c)n型ZnO層表面上に、n型ZnMgO層を形成する。(d)n型ZnMgO層表面上に、ZnO層とZnMgO層とが交互に積層されるZnO/ZnMgO量子井戸層を形成する。(e)ZnO/ZnMgO量子井戸層表面上に、p型ZnMgO層を形成する。(f)p型ZnMgO層表面上に、p型ZnO層を形成する。(g)n型ZnO層及びp型ZnO層上に電極を形成する。工程(b)において、Znリッチ条件で層形成を行う。

(もっと読む)

181 - 200 / 240

[ Back to top ]