Fターム[5F103AA04]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出方法 (899) | 蒸着 (423) | 分子ビーム(MBE)、原子ビーム (251)

Fターム[5F103AA04]の下位に属するFターム

有機金属分子ビーム(MOMBE) (11)

Fターム[5F103AA04]に分類される特許

61 - 80 / 240

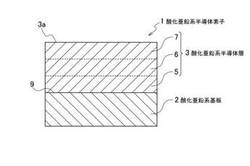

酸化亜鉛系基板及び酸化亜鉛系基板の製造方法

【課題】成長させた酸化亜鉛系半導体の不純物濃度を低減できる酸化亜鉛系基板を提供する。

【解決手段】酸化亜鉛系基板2は、IV族元素であるSi、C、Ge、Sn及びPbの不純物濃度が、1×1017cm−3以下の条件を満たす。より好ましくは、酸化亜鉛系基板2は、I族元素であるLi、Na、K、Rb及びFrの不純物濃度が、1×1016cm−3以下の条件を満たす。

(もっと読む)

原料ガス分解機構、薄膜製造装置、薄膜製造方法、および薄膜積層体

【課題】高品質の薄膜を基板上に堆積させることを容易にする原料ガス分解機構を提供すること。

【解決手段】減圧下のチャンバ17内で基板21上に薄膜を気相堆積させる薄膜製造装置1に設けられ、薄膜の原料となる1種類または複数種類の原料ガスの分解種を分解して該原料ガスの分解種を生成する原料ガス分解機構に、反応室に連通される開口部を有し、該開口部を介して反応室に原料ガスを導入する1つまたは複数のガス導入管13と、上記の開口部での反応室側の開口面よりも基板側に変位した状態で、かつ上記の開口部に近接した状態で接配置される原料ガス分解用の触媒体10と、触媒体に導線11a,11bを介して通電することで該触媒体を昇温させる加熱電源12とを設ける。

(もっと読む)

結晶性ホモロガス化合物層を含む積層体の製造方法及び電界効果型トランジスタ

【課題】目標とする抵抗率を有する結晶性ホモロガス化合物層を含む積層体を製造する方法を提供する。

【解決手段】本発明の結晶性ホモロガス化合物層を含む積層体の製造方法は、M1M2O3(M3O)m(M1=Sc、In、Lu、Yb、Tm、Er、Ho及びYからなる群より選択される少なくとも1種類の元素、M2=Fe、Ga、In及びAlからなる群より選択される少なくとも1種類の元素、M3=Cd、Mg、Mn、Co、CuおよびZnからなる群より選択される少なくとも1種類の元素、m=1以上の自然数)で表される結晶性ホモロガス化合物層を形成する工程と、酸素分圧が2×10−2Pa以下、及び、温度が150℃以上の少なくとも一方の条件を満たす雰囲気下で、前記結晶性ホモロガス化合物層を覆う保護層を形成することにより前記結晶性ホモロガス化合物層の抵抗率を制御する工程と、を有する。

(もっと読む)

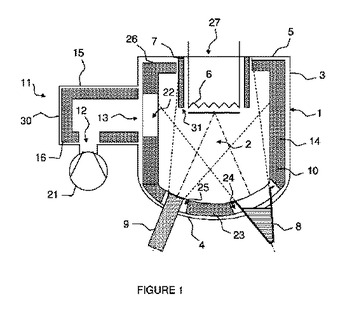

半導体ウエハ製造装置及び分子線を用いての蒸発により材料を蒸着させる装置

【課題】 より小型の、マイクロエレクトロニクス産業のマルチチャンバシステムに適合する、半導体ウエハを製造するための分子線を用いての材料蒸着装置、及び半導体ウエハに対して堆積及び処理ステップの全てをそのままの場所で行うために使用できる半導体ウエハ製造装置を提供すること。

【解決手段】 本発明は、複数の横ポート(3)を有する中央搬送モジュール(2)を備え、10−8を超える真空圧条件下で機能できる、分子線を用いての材料蒸着装置(6)及び半導体ウエハ製造装置に関する。半導体ウエハ製造装置はローディングモジュール(5)と、10−8Torrを超える真空圧条件下で機能し、それぞれが前記中央搬送モジュール(2)の前記ポート(3)の一つに接続された一つ以上の基板処理モジュール(7)とを備える。本発明によれば、前記製造装置は10−8Torr未満の真空圧条件下で動作する、分子線を用いての蒸発による少なくとも一つの材料蒸着モジュール(6)を備え、前記分子線蒸着モジュール(6)は前記中央搬送モジュール(2)の前記ポート(3)の一つに接続され、その処理面(A)に材料の層を堆積させるために前記基板(1)を受容できる。

(もっと読む)

半導体材料のウエハを製造するための分子線エピタキシー装置

本発明は、処理領域(2)を取り囲む成長室(1)、この成長室(1)の側壁(3)の内面を覆う側部部分(10)を少なくとも有する主低温パネル、サンプルホルダー(6)、材料を蒸発させる少なくとも1つのエフュージョンセル(8)、気体状プレカーサーを前記成長室(1)に注入することのできるガスインジェクター(9)、前記成長室(1)に連結され、高い真空能力を提供することのできる排気手段(11)を備えている、半導体材料のウエハを製造する分子線エピタキシー装置に関する。本発明によれば、本分子線エピタキシー装置は、少なくとも成長室壁(3,4,5)の内面を覆う断熱材囲い(14)を備え、この断熱材囲い(14)は、気体状プレカーサーの融点より低いか、これと同一である温度Tminを有する低温部と、高温部を備え、この高温部は、該高温部上の気体状プレカーサーの離脱速度が、気体状プレカーサーの吸着速度の少なくとも1000倍以上であるような温度より高いか、これと同一である温度Tmaxを有している。  (もっと読む)

(もっと読む)

基板上に材料の薄膜を堆積させる装置及びそのような装置の再生方法

【課題】 真空チャンバの低温パネルの再生中に気体状プレカーサーの分圧が制御されることを特徴とする基板上に材料の薄膜を堆積させる装置、及び真空チャンバの低温パネル上に当初捕捉された気体状プレカーサーを、制御されかつ自動的な方式で前記真空チャンバから排気できるようにする再生方法を提供すること。

【解決手段】 本発明は基板上に材料の薄膜を堆積させる装置及び再生方法に関する。装置はチャンバ(1)と、前記チャンバ内に設けられた低温パネル(10)と、基板を支持可能なサンプルホルダ(6)と、前記チャンバ(1)に気体状プレカーサーを注入可能なガスインジェクター(9)と、前記真空チャンバ(1)に接続され、前記低温パネル(10)により放出された前記気体状プレカーサーの一部を捕捉可能であり、不変の排気容量S1を有する第1の捕捉手段(11)とを備える。

発明によれば、基板上に材料の薄膜を堆積させる装置は気体状プレカーサーの分圧の関数として調節可能な可変排気容量S2を有する第2の捕捉手段(18)を備え、前記第1と第2の捕捉手段は前記真空チャンバ(1)内の前記気体状プレカーサーの分圧を所定の圧力PLに維持するのに十分な総合排気容量S=S1+S2をもたらす。

(もっと読む)

高電子移動度トランジスタの製造方法

【課題】安定した特性を有するヘテロ界面の形成、ひいては高い選択性を持ったInPエッチストッパー層の形成を実現するエピタキシャル成長方法を提供する。

【解決手段】分子線エピタキシャル成長法によりIII−V族系化合物半導体のヘテロ接合を有する半導体薄膜を形成するエピタキシャル成長方法であって、少なくとも一種類以上のIII族元素の分子線と第1のV族元素の分子線とを照射して第1の化合物半導体層を形成する第1の工程と、III族元素の分子線と第1のV族元素の分子線の照射を停止し、第1のV族元素の供給量が第1の工程における供給量の1/10以下となるまで成長を中断する第2の工程と、少なくとも一種類以上のIII族元素の分子線と第2のV族元素の分子線とを照射して第1の化合物半導体層上に第1の化合物半導体とは異なる第2の化合物半導体層を形成する第3の工程と、を備える。

(もっと読む)

窒化物半導体薄膜の製造方法

【課題】基板上に金属と活性窒素種とを供給して反応させる窒化物半導体薄膜の製造方法において、金属と活性窒素種との供給比率を容易に制御可能とし、且つ、結晶品質や表面平坦性に優れた窒化物半導体薄膜を形成可能とする手段を提供する。

【解決手段】窒化物半導体薄膜の製造方法は、インジウムをストイキオメトリ条件Sを越えて過剰に供給する金属過剰供給工程と、該金属過剰供給工程で基板10の上に析出したインジウムドロップレット15を、活性窒素種12をストイキオメトリ条件Sに達するまで供給することによってインジウムナイトライド層16に転換するドロップレット転換工程と、を含む。

(もっと読む)

制御された量子ドット成長

本開示は、概して、制御された量子ドットを成長させる技法、および量子ドットの構造に関する。いくつかの例では、基板を用意することと、基板上に欠陥を形成することと、基板上に層を堆積することと、欠陥に沿って量子ドットを形成することとのうちの1つまたは複数を含む方法が記載されている。  (もっと読む)

(もっと読む)

量子井戸構造、半導体レーザ、化合物半導体層を製造する方法及びMBE装置の状態を管理する方法

【課題】フォトルミネッセンス強度が高い井戸層を有する量子井戸構造、半導体レーザ、フォトルミネッセンス強度が高い化合物半導体層を製造する方法及び化合物半導体層のフォトルミネッセンス強度を用いてMBE装置の状態を管理する方法を提供する。

【解決手段】量子井戸構造は、InGaAs又はGaInNAsからなる井戸層を有し、井戸層の酸素濃度が5×1016atoms/cm3以下である。

(もっと読む)

酸化亜鉛基板の表面処理方法及び酸化亜鉛結晶の製造方法

【課題】表面の清浄度及び平坦性に優れた酸化亜鉛基板を得るための酸化亜鉛基板の表面処理方法、及び該方法で処理された酸化亜鉛基板を使用する酸化亜鉛結晶の製造方法の提供。

【解決手段】真空チャンバ13内で加熱された酸化亜鉛基板3の表面に、ガリウム蒸発源11からのガリウム分子線ビームを照射して、前記酸化亜鉛基板3の表面をエッチングすることを特徴とする酸化亜鉛基板3の表面処理方法;かかる方法で酸化亜鉛基板3の表面を処理し、次いでその表面において、亜鉛源6、プラズマ励起酸素源56により、酸化亜鉛結晶を成長させることを特徴とする酸化亜鉛結晶の製造方法。

(もっと読む)

強磁性半導体素子及び強磁性半導体の制御方法

【課題】室温下での動作が可能な強磁性半導体素子及びその制御方法を提供する。

【解決手段】基板11と、基板11上に設けた二酸化チタン層15と、二酸化チタン層15上に設けた遷移元素ドープ二酸化チタン層12と、遷移元素ドープ二酸化チタン層12上に設けた電解液13と、電解液13と接触するよう設けたゲート電極14と、を含む。電解液13は、CsCl4、Sr(ClO4)2、KClO4、NaClO4、LiClO4の一以上の電解質を溶媒に溶かしてなる。ゲート電極14へのゲート電圧印加の有無に応じて、遷移元素ドープ二酸化チタン層12の強磁性の強さが変化する。遷移元素はコバルトが好ましい。

(もっと読む)

ZnO系半導体素子の製造方法及びZnO系半導体素子

【課題】例えば500℃程度以下の低温成長でも、ZnO層の表面平坦性の低下が抑制されたZnO系半導体素子の製造方法を提供する。

【解決手段】ZnO系半導体素子の製造方法は、基板を準備する工程と、無電極放電管にOとNを含むガスを導入し、放電して第1のビーム3aを発生させる工程と、基板11の上方に、少なくともZnを供給するとともに、無電極放電管から第1のビーム3aを供給して、n型ZnO系半導体層を成長させる工程とを有する。

(もっと読む)

III−V族化合物半導体素子の製造方法

【課題】 結晶性が良好なIII−V族化合物半導体であるGaAsSbを含むIII−V族化合物半導体素子の製造方法を提供する。

【解決手段】 III−V族化合物半導体のGaAsxSb1−x(0.33≦x≦0.65)を成膜するとき、V族のヒ素(As)およびアンチモン(Sb)の両方の分子の供給量の和を、III族のガリウム(Ga)の分子の供給量の15倍以上とすることを特徴とする。

(もっと読む)

シリコン基板上にSi3N4へテロエピタキシャルバッファ層を有する窒化シリコン基板の作製方法および装置

【課題】シリコン基板の全表面にわたって均一な厚みを有しかつ品質の安定したSi3N4へテロエピタキシャルバッファ層を容易にかつ安価に作製する作成方法及び装置を提供する。

【解決手段】シリコン基板を表面再構成可能に清浄化処理し、次いで、前記清浄化処理したシリコン基板上に、誘導結合プラズマ方式のRF(高周波)高輝度(HB)放電により生成した解離窒素原子フラックスおよび励起窒素分子フラックスを照射して表面界面反応によりSi3N4単結晶膜をエピタキシャル成長させること。

(もっと読む)

ZnO系半導体素子の製造方法及びZnO系半導体素子

【課題】ZnO系半導体層の表面平坦性低下は抑制しつつ、成長速度の向上が図られたZnO系半導体素子の製造方法を提供する。

【解決手段】ZnO系半導体素子の製造方法は、基板を準備する工程と、無電極放電管3aと5aにOとNを含むガスを導入し、放電して第1のビームを発生させる工程と、成長温度を600℃以上として、基板の上方に、Znソースガン2から、少なくともZnを供給するとともに、無電極放電管3aと5aから第1のビームを供給して、n型ZnO系半導体層を成長させる工程とを有する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】 従来の化合物半導体へテロ接合の製造方法では、微小な信号電流を扱う半導体装置において十分な雑音特性を得ることが困難である。

【解決手段】 基板の上に、III−V族化合物半導体である第1の半導体を、第1の基板温度で成長させる。第1の半導体の成長を停止させ、第1の半導体の表面に、V族元素の原料を供給しながら、基板の温度を、第1の基板温度とは異なる第2の基板温度に変化させる。第1の半導体の上に、第1の半導体とは異なるIII−V族化合物半導体である第2の半導体を、第2の基板温度で成長させる。基板の温度を第1の基板温度から第2の基板温度に変化させる工程が、基板の温度を測定する工程と、V族元素の供給量が、測定された前記基板の温度における供給量の目標下限値と目標上限値との間に納まるように、供給量を制御する工程とを含む。

(もっと読む)

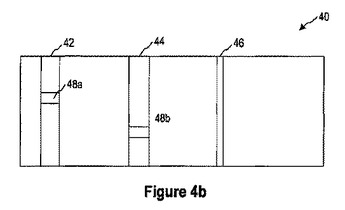

半導体ナノワイヤの製造方法及び半導体装置

【課題】 金属液滴を成長核として用いるナノワイヤ形成法において、隔絶のための薄膜の厚さ等の制限無くかつ方向の揃ったナノワイヤを安定的にかつ再現性よく製造する。

【解決手段】 半導体ナノワイヤ44の製造方法であって、半導体から成る基板42上に非結晶から成る薄膜43を形成する工程と、薄膜43上に金属液滴41を形成する工程と、金属液滴41を成長核として上記半導体から成る半導体ナノワイヤ44を結晶成長する工程とを有し、薄膜43は金属液滴41と化学反応する材料から成る。

(もっと読む)

半導体量子ドット及び同形成方法

【課題】

巨大アイランドの形成による結晶品質の低下という問題を引き起こすことなく、ナノ構造の品質・形状を高品質に保つことを可能とする半導体量子ドット及び同形成方法を提供すること。

【解決手段】

本願に係る半導体量子ドット形成方法は、自己組織化機構により半導体量子ドットを形成する方法において、量子ドットDの結晶成長レート及び/もしくは埋め込み層L4の結晶成長速度として1ML/s(モノレイヤー・パー・セカンド)以上によって層形成させる。

(もっと読む)

半導体装置及びその製造方法

【課題】

成長中断による、Alを含むIII-V族化合物半導体層への酸素の取り込みを抑制した半導体装置を提供すること。

【解決手段】

Alを構成元素として含む第1のIII-V族化合物半導体によって半導体基板上に形成された第1の半導体層と、厚さが2原子層以上8原子層以下のAlを構成元素として含まない第2のIII-V族化合物半導体で形成され、且つ前記第1の半導体層の上面又は前記第1の半導体層の内部に配置された表面保護層とを有する半導体積層構造と、第3のIII-V族化合物半導体で形成され、且つ前記半導体積層構造の上面に形成された第2の半導体層を具備すること。

(もっと読む)

61 - 80 / 240

[ Back to top ]