Fターム[5F103BB36]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 析出装置 (1,132) | 基板取扱機構 (210) | 基板移動機構 (53)

Fターム[5F103BB36]の下位に属するFターム

マニピュレータ (3)

基板回転動作機構・プラネタリ(ウム) (23)

Fターム[5F103BB36]に分類される特許

1 - 20 / 27

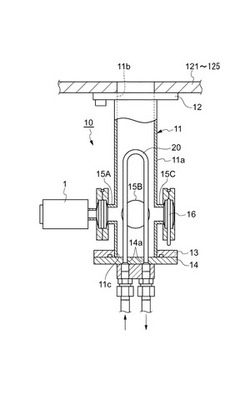

成膜装置

【課題】真空計への成膜材料の付着を抑制し、真空計の機能の低下を回避することが可能な成膜装置を提供すること。

【解決手段】基板に成膜材料を成膜する成膜装置において、基板が通過する真空環境を形成する真空容器123と、真空容器123内の真空度を測定する真空計1と、真空計1への付着を抑制する付着抑制手段10とを備える構成とする。このように、真空計1への成膜材料の付着を抑制する付着抑制手段10を備える構成とすることで、真空計1への成膜材料の付着を抑制し、真空計1の機能の低下を緩和することができる。

(もっと読む)

プラズマ源およびこれを用いた薄膜の製造方法

【課題】

本発明は高品質な化合物薄膜または有機物薄膜を高い生産性で連続的に製造可能とするために、低ダメージで反応性の高い成膜条件を実現するプラズマ源と薄膜の製造方法を提供することを目的とする。具体的には、従来のスパッタ法におけるターゲット使用効率を改善すると共に、基材へ入射する粒子の運動エネルギーを十分緩和しても良好な膜質を得るための高密度なマグネトロンプラズマを基材近傍に生成するものである。

【解決手段】

対向した少なくとも一対の平板型マグネトロンプレートを有し、前記対向する平板型マグネトロンプレートの一方のみがスパッタカソードであることを特徴とする、プラズマ源。

(もっと読む)

スパッタリング装置及びスパッタリング方法、ならびにその方法で作製された電子デバイス

【課題】主材料のみからなる薄膜と該主材料に1%以下(ppmオーダー)の副材料を添加した薄膜、およびそれらの多層や積層膜を制御性よく高品質かつ安全・安価に提供することを目的としたスパッタリング装置、スパッタリング方法および該薄膜を用いて作成された電子デバイスを提供すること。

【解決手段】形成する薄膜の主材料ターゲット1iを有する複数のマグネトロンスパッタリングカソード3mの間に、添加材料となる成分を含む副材料からなる副材料ターゲット1p,1nを有するコンベンショナルスパッタリングカソード3cを配置し、マグネトロンスパッタリングカソード3mおよびコンベンショナルスパッタリングカソード3cに投入するスパッタリング電力を独立に制御することを特徴とする。

(もっと読む)

真空蒸着装置

【課題】搬送中に基板がホルダから外れることを防止することができる真空蒸着装置を提供する。

【解決手段】ホルダ103aは、基板20を保持する一方面S1と、一方面S1と反対の他方面S2とを有する。またホルダ103aには、平面視において基板20の一部と重複する領域において開口部OPが設けられている。蒸着源120はホルダ103aの一方面S1に対向している。ヒータはホルダの他方面S2に対向している。固定具60は、ホルダの一方面S1上に固定され、一方面S1との間で基板20を挟むことによって基板20を固定している。

(もっと読む)

成膜装置

【課題】被成膜材料の有無を検出する検出機能を確保することができる成膜装置を提供する。

【解決手段】成膜装置1は、ワークWに成膜材料を成膜する成膜装置であって、ワークWを収納し成膜処理を行う成膜室2と、成膜室2の内部に設けられ、ワークWを搬送する搬送装置7と、成膜室2を画成する壁3aに設けられ、光を透過する防着ガラス27を有し、成膜室2の外部から内部への投光を可能とするビューポート13と、成膜室2の外部に設けられ、ビューポート13の防着ガラス27を透過させてセンサー光を投光し成膜室2の内部のワークWの有無を検出する走行センサ11と、防着ガラス27への成膜材料の堆積を抑制するためのヒータ31と、を備えている。

(もっと読む)

基板冷却方法、基板冷却装置並びに製膜装置

【課題】製膜処理のタクトタイムが短い場合であっても、アンロード室で基板の温度分布が少ない状態とし、基板のそり変形や破損を抑制することができる基板冷却方法、基板冷却装置および製膜装置を提供することを目的とする。

【解決手段】減圧環境下において高温条件で表面に製膜処理が施された基板7を、減圧環境下でアンロード室に受け入れて、基板7の少なくとも一方の面側から、基板7の中央部に冷媒を噴き付けて基板7の冷却を行う第1基板冷却工程と、該第1基板冷却工程を経た基板7をアンロード室から搬出した後に、基板7の一方の面の反対側から、第1基板冷却工程で冷媒を噴き付けた領域の縁から所定距離内側に冷媒を噴き付けて、あるいは、第1基板冷却工程で冷媒を噴き付けた領域の縁から所定距離外側に冷媒を噴き付けて基板の冷却を行いながら基板の面内温度分布を補正する第2基板冷却工程と、を備える基板冷却方法。

(もっと読む)

成膜装置、連続成膜装置、及び成膜方法

【課題】安定した電気的特性と高い信頼性を有する半導体装置を実現する成膜装置を提供することを課題の一とする。また、マザーガラスのような大きな基板を用いて、信頼性の高い半導体装置の大量生産を行うことの出来る成膜装置を提供することを課題の一とする。また、上記成膜装置を用いて安定した電気的特性と高い信頼性を有する半導体装置の作製方法を提供することを課題の一とする。

【解決手段】基板の搬送機構と、搬送機構が送る基板の進行方向に沿って、酸化物半導体を成膜する第1の成膜室と、第1の熱処理を行う第1の加熱室とを有し、基板は、該基板の成膜面と鉛直方向との成す角が1°以上30°以内に収まるよう保持され、大気に曝すことなく、基板に第1の膜を成膜した後に第1の熱処理を施すことのできる成膜装置を用いて、酸化物半導体層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】比較的低い温度で作製することができ、電荷の高い移動度を得ることができる半導体装置及びその製造方法を提供する。

【解決手段】酸化物半導体の微粒子を基板に吹き付けてチャネル用の半導体膜3を形成し、半導体膜3を間に挟むソース5s及びドレイン5dを形成する。

(もっと読む)

インライン型プラズマ成膜装置およびこれを用いたプラズマ成膜方法

【課題】プラズマの回り込みを効果的に抑制して被処理基板の意図しない部分に膜が成膜されることを防止することのできるインライン型プラズマ成膜装置を提供する。

【解決手段】インライン型プラズマ成膜装置1Aは、搬送路4上において被処理基板100を搬送する複数の搬送ローラ3と、被処理基板100の上面に面するようにプラズマを生成することで被処理基板100の上面に膜を成膜するプラズマ生成部と、被処理基板100の下面に膜が成膜されることを防止する成膜防止部材5とを備えている。成膜防止部材5は、プラズマが生成される領域に搬送路4を挟んで対面する領域でかつ搬送ローラ3が位置する部分を除く領域を上方から見て実質的に満たすように配置され、被処理基板100の下面に対面するように設けられた平面状の成膜防止面5aを含み、当該成膜防止面5aの幅は、被処理基板100の幅よりも大きく構成されている。

(もっと読む)

真空装置

【課題】 基板表面にある凹凸のために基板とロールの間に入れたガスは基板端部から漏れ出し、高い伝熱能力を得ることは困難である。

【解決手段】 真空中で長尺基板18を搬送する機構を有する真空装置であって、チャンバー1と、チャンバー1内を排気する真空ポンプ2と、チャンバー1内で長尺基板18を搬送する複数の搬送ロールと、チャンバー1内で搬送ロールの少なくとも一つが開口部に設置され開口部に配置された搬送ロール24に近接する仕切り部材28を有するケース23と、ケース23内にガスを導入するガス導入手段と、ケース23内で長尺基板18を搬送しながら、長尺基板18を冷却する冷却ロール25と、を有し、ケース23内での長尺基板搬送長に対する、長尺基板18と冷却ロール25との接触長との比が、ケース23外での長尺基板搬送長に対する、長尺基板18と搬送ロールとの接触長との比より大きいことを特徴とする構成とする。

(もっと読む)

半導体素子の製造方法

【課題】広い範囲で制御された組成比を有し、結晶性が優れる化合物半導体の膜を用いた半導体素子を製造する方法を提供する。

【解決手段】基板上にn型半導体およびp型半導体を含むように積層して構成された半導体素子の製造方法であって、異なるIII族元素による少なくとも2つのターゲット(第1ターゲット21および第2ターゲット22)を、V族元素を含むガスによりスパッタリングして、基板110上にIII−V族の化合物半導体の膜を形成する工程を含む。

(もっと読む)

半導体ウエハ製造装置及び分子線を用いての蒸発により材料を蒸着させる装置

【課題】 より小型の、マイクロエレクトロニクス産業のマルチチャンバシステムに適合する、半導体ウエハを製造するための分子線を用いての材料蒸着装置、及び半導体ウエハに対して堆積及び処理ステップの全てをそのままの場所で行うために使用できる半導体ウエハ製造装置を提供すること。

【解決手段】 本発明は、複数の横ポート(3)を有する中央搬送モジュール(2)を備え、10−8を超える真空圧条件下で機能できる、分子線を用いての材料蒸着装置(6)及び半導体ウエハ製造装置に関する。半導体ウエハ製造装置はローディングモジュール(5)と、10−8Torrを超える真空圧条件下で機能し、それぞれが前記中央搬送モジュール(2)の前記ポート(3)の一つに接続された一つ以上の基板処理モジュール(7)とを備える。本発明によれば、前記製造装置は10−8Torr未満の真空圧条件下で動作する、分子線を用いての蒸発による少なくとも一つの材料蒸着モジュール(6)を備え、前記分子線蒸着モジュール(6)は前記中央搬送モジュール(2)の前記ポート(3)の一つに接続され、その処理面(A)に材料の層を堆積させるために前記基板(1)を受容できる。

(もっと読む)

真空蒸着装置

【課題】蒸着材料の利用効率を向上させつつ、基板へのスプラッシュの付着を阻止することができる真空蒸着装置を提供する。

【解決手段】本発明に係る真空蒸着装置において、蒸発源40は、複数のチムニ(筒状部)42を有し、これらチムニから蒸着材料の蒸気を放出することで、対向する基板T上に蒸着膜を形成する。チムニの先端部と基板との間の距離L1を100mm以下とすることで、チムニの直上に位置する基板に対する蒸発物質の付着量を増加させる。これにより、蒸着レートが向上するとともに、蒸着材料の利用効率を高めることが可能となる。また、チムニを有することで、スプラッシュが基板へ到達することを効果的に阻止することが可能となる。

(もっと読む)

アモルファス酸化物薄膜の気相成膜方法

【課題】電子キャリア濃度が低い、アモルファス酸化物薄膜の成膜方法の提供。

【解決手段】組成が、式[Sn1−xM4xO2]a・[(In1−yM3y)2O3]b・[Zn1−zM2zO]c(ここで、0≦x≦1、0≦y≦1、0≦z≦1、かつx、y、zは同時に1ではなく、0≦a≦1、0<b≦1、0≦c≦1、かつa+b+c=1)、で示される酸化物の多結晶をターゲットとして、基板の温度は意図的に加温しない状態で、酸素ガスを含む雰囲気中の酸素分圧を制御して、基板上に薄膜を堆積させることによって、室温での電子移動度が0.1cm2/(V・秒)以上、かつ電子キャリヤ濃度が1018/cm3未満である半絶縁性である透明アモルファス酸化物薄膜を気相成膜する。

(もっと読む)

基板搬送処理装置及び方法

【課題】少ない設置面積で、ウェーハを含む基板の搬送及び処理を行う装置及び方法を提供する。

【解決手段】線形搬送チャンバ1232は、線形トラックと、線形トラックに乗っているロボットアーム1243等を含み、基板を線形的に、処理チャンバ1201等の側部に沿って搬送する。又ロードロック1235を介し、処理チャンバ1201等に到達させ、搬送チャンバ1232に沿って基板を制御された雰囲気の中に供給する。よって相応な経費で、且つ改良されたスループットで効率的に製造を行うことができる。

(もっと読む)

直線状堆積供給源

【課題】複数のノズルに供給される複数の坩堝から蒸発した材料の量を正確に制御する堆積供給源を提供する。

【解決手段】堆積供給源100であって、a)堆積材料を収容する複数の坩堝102と、b)複数のコンダクタンスチャネルを備える本体112と、c)坩堝とコンダクタンスチャネルと熱的な連通をするように配置されたヒータと、d)複数の坩堝のうちの少なくとも1つに、部分的な熱分離を提供する熱シールドと、e)複数のノズルからなり、該ノズルの各々の入力は該複数のコンダクタンスチャネルの出力に連結され、蒸発した堆積材料は、該複数の坩堝から、該コンダクタンスチャネルを通って該ノズルまで移送され、該蒸発した堆積材料は該ノズルから排出され堆積フラックスを形成する。

(もっと読む)

光起電力モジュールの大量製造装置および方法

【課題】 基体の急速加熱、CdSの成膜、CdTeの成膜、CdCl2処理お よびオーム接点形成を含むすべての工程を中程度の圧力で単独の真空境界内で実施する、CdTe光起電力モジュールを大規模インラインで製造するための装置およびプロセスを提供する。

【解決手段】 金属塩をCdTe層上へ昇華することによってp+オーム接点領域を形成する。低コスト噴霧プロセスによって背面電極を形成し、マスクを介して行なう研磨ブラスチングか機械的ブラッシングによってモジュールをスクライビングする。真空処理装置によって、基体および膜の加熱、蒸気漏出を極力抑制した、基体および膜の蒸気への暴露、基体上への薄膜の成膜、および薄膜の基体からの剥離が容易になる。基体搬送装置により、薄膜成膜時に基体を真空に出入りさせるのが容易になり、基体搬送装置自体に被覆が生じるのを防止する。

(もっと読む)

オプトエレクトロニック半導体素子およびその製造方法

本発明は、分子線エピタキシーによって半導体ヘテロ構造を製造するための方法に関するものであり、以下のステップを有する。それらは、基板を第1の真空チャンバに導入するステップと、基板を第1の温度に加熱するステップと、第1のエピタキシャル層を生成するステップであって、当該層は、III族およびV族典型元素の2元、3元または4元化合物を含む第1の材料を含み、少なくとも1つの分子線から堆積されるステップと、前記基板を第2の温度に冷却するステップであって、III族およびV族典型元素の分子線を遮るステップと、基板を第3の温度に加熱するステップと、第2のエピタキシャル層を生成するステップであって、当該層は、III族およびV族典型元素の2元、3元または4元化合物を含む第2の材料を含み、少なくとも1つの分子線から堆積されるステップとである。さらに、本発明は、ここで述べた方法によって得ることができる半導体素子に関する。  (もっと読む)

(もっと読む)

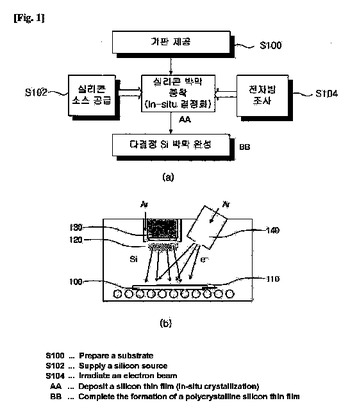

エネルギービームの照射を利用したシリコーン薄膜の製造方法

本発明のシリコーン薄膜の製造方法は、基板を提供する段階と;前記基板上にシリコーンソースを供給する段階と;前記シリコーンソースを供給してシリコーン薄膜を形成するとともに、電子ビームとイオンビームを照射したり、シリコーンソースを供給してシリコーン薄膜を形成した後後処理として前記基板上に電子ビームとイオンビームを照射する段階とを含む。本発明によって、前記供給されたシリコーンソースによって前記基板上にシリコーン薄膜が蒸着されながら前記照射された電子ビームが前記蒸着中のシリコーン薄膜にエネルギーを供給してこのシリコーン薄膜を蒸着工程中に(in−situ)結晶化させたり、非晶質シリコーン薄膜が形成された後後処理として電子ビームとイオンビームを照射することによって結晶化させることができる。また、電子ビームを照射するとともに、イオンビームをともに照射することによって、基板表面に蓄積される電子ビームの電荷がイオンビームの電荷によって中和されるようにして、電子ビームの電荷が基板表面に蓄積されて不必要な表面電流を形成することを防止し、效率的に非晶質シリコーン薄膜を結晶化させることができる。  (もっと読む)

(もっと読む)

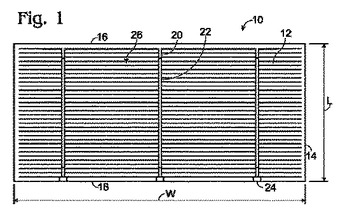

薄膜太陽電池セルを製造するための装置および方法

基板ウェブ上に半導体材料吸収層の薄膜層を形成するための改善された方法および装置を提供する。本発明の教示に従って、半導体層をマルチゾーンプロセスで形成することができ、これにより、さまざまな層が移動する基板ウェブ上に順次蒸着される。  (もっと読む)

(もっと読む)

1 - 20 / 27

[ Back to top ]