Fターム[5F103LL09]の内容

半導体装置を構成する物質の物理的析出 (6,900) | 適用デバイス・適用構造 (785) | 電界効果トランジスタ(FET) (97) | 2次元電子ガストランジスタ・HEMT (18)

Fターム[5F103LL09]に分類される特許

1 - 18 / 18

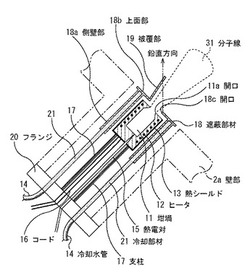

分子線結晶成長装置及び半導体装置の製造方法

【課題】良好な結晶を安定して成長させることができる分子線結晶成長装置及び半導体装置の製造方法を提供する。

【解決手段】原料を放出する開口11aを有する坩堝11と、坩堝11の外周及び開口11aの縁を覆う遮蔽部材18と、遮蔽部材18を冷却する冷却部材21と、坩堝11に対向するように基板を保持する基板保持部材と、が設けられている。遮蔽部材18には、鉛直上方から坩堝11を覆う被覆部19が設けられている。

(もっと読む)

窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法

【課題】任意の基板上に形成でき良好な結晶性を有する窒化物半導体素子、窒化物半導体ウェーハ及び窒化物半導体層の製造方法を提供する。

【解決手段】実施形態によれば、第1層と、機能層と、を備えた窒化物半導体素子が提供される。前記第1層は、非晶質層の上に形成され、窒化アルミニウムを含み、圧縮歪または引張歪を有する。前記機能層は、前記第1層の上に形成され、窒化物半導体を含む。

(もっと読む)

GaNHEMT装置用再成長ショットキー構造

【課題】高温で動作可能な高電子移動度トランジスタを提供する。

【解決手段】バッファ層16と、バッファ層16上のIII−V族層18と、III−V族層18上のソース接点20およびドレイン接点22と、III−V族層18上で、ソース接点20およびドレイン接点22間の再成長ショットキー層10と、成長ショットキー層10上のゲート接点24、を備える装置、および装置を用いたシステムを含む。さらに、装置とシステムの製造方法も含む。

(もっと読む)

分子線結晶成長装置およびシャッタ機構

【課題】加熱されたセル上へのフレークの落下付着を防止する分子線結晶成長(MBE)装置のシャッタ機構を提供する。

【解決手段】動作時に、セル2の中心軸上で該セル2と対向する位置において蒸発原料を通過させる開口部11を備え、非動作時には、該開口部11以外の部分でセル2上面を覆うシャッタ板1と、シャッタ板1の側面に一体的に取り付けられ、セル2の側面の一部または全体を覆うスカート部4と、シャッタ板1を回転または移動させる駆動軸3と、を有し、シャッタ開の状態でも、セル2の分子線照射開口以外を覆うことを特徴とする分子線結晶成長装置のシャッタ機構。

(もっと読む)

半導体装置の製造方法

【課題】サファイア基板上に高品質なIII族窒化物を結晶成長させ、高品質な半導体装置を得ることが可能な半導体装置の製造方法を提供する。

【解決手段】直接窒化されたサファイア基板2上のAlN層にラジカル源5から窒素ラジカル又は窒素イオンを含む気体を所定時間照射する。その後、成長させるIII族窒化物の構成元素からなるターゲット3aに窒素雰囲気中でパルスレーザ光を照射するPLD(パルスレーザ堆積)法によってIII族窒化物を結晶成長させることにより、極めて高品質なN極性結晶を得ることができる。

(もっと読む)

III族窒化物半導体積層構造体

【課題】高度の結晶性を有し、特に直径100mm以上の大型基板を用いる場合でも全面均一に平坦なAlN結晶膜シード層を用いることにより、結晶性の良いGaN系薄膜を得、信頼性の高い高輝度のLED素子等を得る。

【解決手段】サファイア基板上にシード層としてスパッター法で堆積されたAlN結晶膜を有し、該シード層上にIII族窒化物半導体からなる、n型半導体層、発光層およびp型半導体層を積層してなるIII族窒化物半導体積層構造体において、該シード層のAlN結晶膜中の酸素含有量が0.1原子%以上5原子%以下であり、AlN結晶膜は結晶粒界の間隔が200nm以上であり、かつ最終p型半導体層であるp−コンタクト層のロッキングカーブ半値幅が(0002)面と(10−10)面でそれぞれ60arcsec以下および250arcsec以下であることを特徴とするIII族窒化物半導体積層構造体。

(もっと読む)

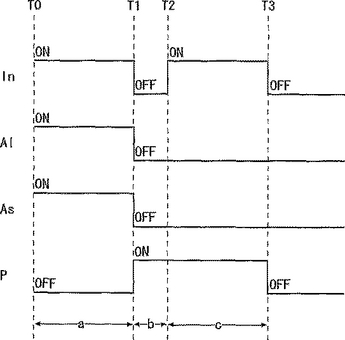

高電子移動度トランジスタの製造方法

【課題】安定した特性を有するヘテロ界面の形成、ひいては高い選択性を持ったInPエッチストッパー層の形成を実現するエピタキシャル成長方法を提供する。

【解決手段】分子線エピタキシャル成長法によりIII−V族系化合物半導体のヘテロ接合を有する半導体薄膜を形成するエピタキシャル成長方法であって、少なくとも一種類以上のIII族元素の分子線と第1のV族元素の分子線とを照射して第1の化合物半導体層を形成する第1の工程と、III族元素の分子線と第1のV族元素の分子線の照射を停止し、第1のV族元素の供給量が第1の工程における供給量の1/10以下となるまで成長を中断する第2の工程と、少なくとも一種類以上のIII族元素の分子線と第2のV族元素の分子線とを照射して第1の化合物半導体層上に第1の化合物半導体とは異なる第2の化合物半導体層を形成する第3の工程と、を備える。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】 従来の化合物半導体へテロ接合の製造方法では、微小な信号電流を扱う半導体装置において十分な雑音特性を得ることが困難である。

【解決手段】 基板の上に、III−V族化合物半導体である第1の半導体を、第1の基板温度で成長させる。第1の半導体の成長を停止させ、第1の半導体の表面に、V族元素の原料を供給しながら、基板の温度を、第1の基板温度とは異なる第2の基板温度に変化させる。第1の半導体の上に、第1の半導体とは異なるIII−V族化合物半導体である第2の半導体を、第2の基板温度で成長させる。基板の温度を第1の基板温度から第2の基板温度に変化させる工程が、基板の温度を測定する工程と、V族元素の供給量が、測定された前記基板の温度における供給量の目標下限値と目標上限値との間に納まるように、供給量を制御する工程とを含む。

(もっと読む)

窒化物系III−V族化合物半導体装置の製造方法

【課題】バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供する。

【解決手段】SiC基板71上にAlNのバッファ層72を形成した後、AlNのバッファ層72上にGaN層を成長させる。続いて、AlNのバッファ層72と上記GaN層の界面近傍に、Gaイオンを打ち込んで、AlNのバッファ層72と上記GaN層の界面付近にアモルファスの層74を形成する。その後、基板温度を800℃まで上げてアモルファスの層74の上の上記GaN層を再結晶化して、転位が少ないGaN層75層を形成する。

(もっと読む)

化合物半導体基板

【課題】電気的な絶縁性及び良好な熱伝導性を有する中間層を備えた化合物半導体基板の提供。

【解決手段】表面の結晶面方位が{111}面であるSi単結晶基板100と、前記Si単結晶基板100の表面に形成され、AlNで構成された第1層110aと、MgOで構成された第2層110bとが、この順で互いに交互に複数積層された中間層110と、前記中間層110上に形成され、GaN(0001)、AlN(0001)又はInN(0001)のいずれか1種で構成された窒化物半導体単結晶層120と、を備える。

(もっと読む)

ZnO系半導体素子

【課題】ZnO系半導体からなるアクセプタドープ層を含む積層体を形成する場合に、アクセプタ元素の濃度を低下させずに、アクセプタドープ層又はアクセプタドープ層以降の層の平坦性が悪くなるのを抑制することができるZnO系半導体素子を提供する。

【解決手段】ZnO基板1上にn型MgZZnO層2、アンドープMgZnO層3、MQW活性層4、アンドープMgXZnO層5、アクセプタドープMgYZnO層6が順に積層されている。アクセプタドープMgYZnO(0≦Y<1)層6は、アクセプタ元素を少なくとも1種類含んでおり、この層に接してアンドープMgXZn1−XO(0<X<1)層5が形成されている。このため、アクセプタドープ層にアクセプタ元素を十分取り込むことができるとともに、アクセプタドープ層の表面平坦性は良くなる。

(もっと読む)

高電子移動度ZnOデバイス

【課題】 本発明は、HEMT構造に適した“大きなバンドギャップの半導体/小さなバンドギャップの半導体/基板”構造で、2次元電子ガス層をチャンネル層として利用する構造の高電子移動度ZnOデバイスを提供することを課題とする。

【解決手段】 Zn極性(0001)面を有するアンドープZnO層及びZn極性(0001)面を有するアンドープZn1−xMgxO(0.15≦x≦0.45)層のヘテロ接合を有し、Zn極性(0001)面を有するアンドープZnO層の2次元電子ガス層をチャンネル層とすることを特徴とする高電子移動度ZnOデバイスである。

(もっと読む)

半導体積層膜、及び半導体積層膜作製用装置

【課題】Si単結晶基板上において、表面欠陥密度の少ないSi1−XGeX膜を有する半導体多層膜を提供する。

【解決手段】Si単結晶基板と、このSi単結晶基板上に形成されたSi1−XGeX(0<X≦1)膜とを具えた半導体積層膜において、前記Si1−XGeX膜は好ましくはマグネトロンスパッタリング法で形成し、前記Si1−XGeX膜の表面欠陥密度が104/cm2以下となるようにする。

(もっと読む)

ZnO系半導体素子

【課題】積層側の主面がc軸方向を向いているMgZnO基板上に平坦なZnO系半導体層を成長させることができるZnO系半導体素子を提供する。

【解決手段】+C面(0001)が少なくともm軸方向に傾斜した面を主面とするMgxZn1−xO(0≦x<1)基板1上に、ZnO系半導体層2〜6がエピタキシャル成長されている。そして、ZnO系半導体層6上にはp電極10が、MgxZn1−xO基板1の下側にはn電極9が形成されている。このようにして、MgxZn1−xO基板1の表面に、m軸方向に並ぶ規則的なステップを形成することで、ステップバンチングと呼ばれる現象を防ぎ、基板1上に積層される半導体層の膜の平坦性を向上させることができる。

(もっと読む)

III族窒化物半導体素子の製造

電源電極を受け入れる部分の上に保護本体を設ける間に、ゲート構造を形成する工程を有する、III族窒化物電力半導体素子を製造する方法。 (もっと読む)

内包体、内包体の製造方法および製造装置

【課題】外壁に付着した制御物質の除去が可能であり、安定した電気的特性を維持できる内包体等を提供する。

【解決手段】単層カーボンナノチューブと、該単層カーボンナノチューブのチューブ内に含まれた制御物質(フラーレンを除く)およびフラーレンを有し、前記制御物質は、前記単層カーボンナノチューブの電気特性を制御可能な物質であり、前記フラーレンは、前記制御物質よりも、前記単層カーボンナノチューブの開口部により近い側にそれぞれ設けられている、内包体。

(もっと読む)

エピタキシャル成長方法

分子線エピタキシャル成長法によりIII−V族系化合物半導体のヘテロ接合を有する半導体薄膜を形成するエピタキシャル成長方法であって、少なくとも一種類以上のIII族元素の分子線と第1のV族元素の分子線とを照射して第1の化合物半導体層を形成する第1の工程と、前記III族元素の分子線と前記第1のV族元素の分子線の照射を停止し、前記第1のV族元素の供給量が前記第1の工程における供給量の1/10以下となるまで成長を中断する第2の工程と、少なくとも一種類以上のIII族元素の分子線と第2のV族元素の分子線とを照射して前記第1の化合物半導体層上に前記第1の化合物半導体とは異なる第2の化合物半導体層を形成する第3の工程と、を備えるようにした。  (もっと読む)

(もっと読む)

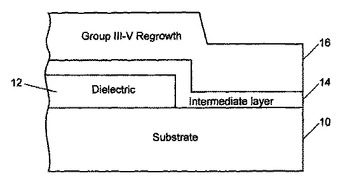

誘電体上にIII−V族半導体材料を成長させるための方法

III−V族半導体材料の再成長層の形成は、中間層を予め形成することによって、容易にされる。この中間層は、主として、その滑らかな形態特性により選択される。この中間層は、下にある基板を覆うように、かつこの基板の一部を覆って形成された誘電体層を覆うように、形成される。この中間層は、その下にある基板層の、誘電体層によって覆われた領域以外の領域の単結晶特性を維持し、そしてこの中間層を覆って形成された再成長層の電気的特性および形態特性を改善する。  (もっと読む)

(もっと読む)

1 - 18 / 18

[ Back to top ]