Fターム[5F110AA02]の内容

Fターム[5F110AA02]に分類される特許

1 - 20 / 412

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

液晶表示装置、表示モジュール及び電子機器

【課題】アクティブマトリクス型基板において、薄膜トランジスタと、その端子接続部を同時に作り込み、少ないマスク数で歩留まりの良い表示装置を提供する。

【解決手段】画素部および外部入力端子を有する表示装置であって、画素部は、ゲート電極と、半導体膜と、ゲート電極上に形成された絶縁膜、および絶縁膜上に半導体膜と電気的に接続された電極を有するTFTを有し、外部入力端子は、ゲート電極と同じ層に形成された第1の配線と、電極と同じ層に形成され、絶縁膜に形成されたコンタクトホールを介し第1の配線と接続された第2の配線と、第2の配線に接続され、第2の配線上に形成された透明導電膜と、第2の配線と透明導電膜が接続している位置で透明導電膜と電気的に接続するフレキシブルプリント配線板を有する表示装置。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

酸化物半導体膜の処理方法および半導体装置の作製方法

【課題】トランジスタに用いることが可能な、低抵抗領域を有する酸化物半導体膜を提供する。また、高速動作が可能な、酸化物半導体膜を用いたトランジスタを生産性高く提供する。また、高速動作が可能な、酸化物半導体膜を用いたトランジスタを有する高性能の半導体装置を生産性高く提供する。

【解決手段】酸化物半導体膜上に還元性を有する膜を成膜し、次に酸化物半導体膜から還元性を有する膜へ酸素の一部を移動させ、次に還元性を有する膜を介して酸化物半導体膜に不純物を注入した後、還元性を有する膜を除去することで、酸化物半導体膜に低抵抗領域を形成する。

(もっと読む)

表示装置

【課題】動作速度を向上させる。

【解決手段】第1のソース及び第1のドレインの一方に画像信号線を介して画像信号が入力され、第1のゲートに第1の走査信号線を介して第1の走査信号が入力される第1のトランジスタ101と、2つの電極のうちの一方の電極が第1のトランジスタの第1のソース及び第1のドレインの他方に電気的に接続される容量素子102と、第2のソース及び第2のドレインの一方が第1のトランジスタ101の第1のソース及び第1のドレインの他方に電気的に接続され、第2のゲートに第2の走査信号線を介して第2の走査信号が入力される第2のトランジスタ103と、第1の電極が第2のトランジスタの第2のソース及び第2のドレインの他方に電気的に接続される液晶素子104と、を備え、画像信号線としての機能を有する導電層及び第2の走査信号が入力される走査信号線としての機能を有する導電層は、互いに離間し、且つ並置されている。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置

を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極およびド

レイン電極と、酸化物半導体層、ソース電極およびドレイン電極を覆うゲート絶縁層と、

ゲート絶縁層上のゲート電極と、を有し、酸化物半導体層の厚さは1nm以上10nm以

下であり、ゲート絶縁層は、ゲート絶縁層に用いられる材料の比誘電率をεr、ゲート絶

縁層の厚さをdとして、εr/dが、0.08(nm−1)以上7.9(nm−1)以下

の関係を満たし、ソース電極とドレイン電極との間隔は10nm以上1μm以下である半

導体装置である。

(もっと読む)

半導体装置及びその製造方法

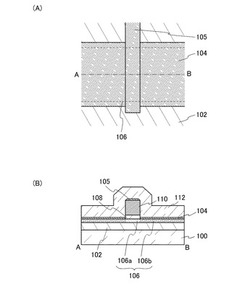

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを

課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を

用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導

体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時

に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置

【課題】半導体集積回路における消費電力を低減する。また、半導体集積回路における動作の遅延を低減する。

【解決手段】記憶回路が有する複数の順序回路のそれぞれにおいて、酸化物半導体によってチャネル形成領域が構成されるトランジスタと、該トランジスタがオフ状態となることによって一方の電極が電気的に接続されたノードが浮遊状態となる容量素子とを設ける。なお、酸化物半導体によってトランジスタのチャネル形成領域が構成されることで、オフ電流(リーク電流)が極めて低いトランジスタを実現することができる。そのため、記憶回路に対して電源電圧が供給されない期間において当該トランジスタをオフ状態とすることで、当該期間における容量素子の一方の電極が電気的に接続されたノードの電位を一定又はほぼ一定に保持することが可能である。その結果、上述した課題を解決することが可能である。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

半導体装置

【課題】ブラックマトリックス層の幅を設計値以上に拡張しなくても、位置合わせずれによる光漏れが生じることを抑制する。

【解決手段】ボトムゲート電極12aと第1のブラックマトリックス層17aで第1の半導体層14を挟むシングルゲート型の薄膜トランジスタを有する半導体装置であって、前記第1の半導体層と前記第1のブラックマトリックス層は重畳している半導体装置である。

(もっと読む)

半導体装置

【課題】高速動作、低消費電力である半導体装置の提供。

【解決手段】結晶性のシリコンをチャネル形成領域に有する第1のトランジスタを用いた記憶素子と、当該記憶素子のデータを記憶する容量素子と、当該容量素子における電荷の供給、保持、放出を制御するためのスイッチング素子である第2のトランジスタとを有する。第2のトランジスタは第1のトランジスタを覆う絶縁膜上に位置する。第1及び第2のトランジスタは、ソース電極又はドレイン電極を共有している。上記絶縁膜は、加熱により一部の酸素が脱離する第1の酸化絶縁膜と、酸素の拡散を防ぎ、なおかつ当該第1の酸化絶縁膜の周囲に設けられた第2の酸化絶縁膜とを有し、第2のトランジスタが有する酸化物半導体膜は、上記第1の酸化絶縁膜に接し、かつチャネル形成領域である第1の領域と、第1の領域を挟み、第1及び第2の酸化絶縁膜に接する一対の第2の領域とを有する半導体装置。

(もっと読む)

半導体装置

【課題】高性能な半導体装置を提供する。

【解決手段】絶縁表面上に設けられるゲート電極層421と、ゲート電極層上に設けられるゲート絶縁層402と、ゲート絶縁層上に設けられる第1の酸化物半導体層442と、第1の酸化物半導体層上に接して設けられる第2の酸化物半導体層443と、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域と重なり、且つ第2の酸化物半導体層に接して設けられる酸化物絶縁層と、酸化物絶縁層上、第1の酸化物半導体層の第2の領域上、及び第2の酸化物半導体層の第2の領域と重なり、且つ第2の酸化物半導体層に接して設けられるソース電極層及びドレイン電極層と、を有し、第1の酸化物半導体層の第1の領域及び第2の酸化物半導体層の第1の領域は、ゲート電極層と重なる領域、並びに第1の酸化物半導体層及び第2の酸化物半導体層の周縁及び側面、に設けられる領域である。

(もっと読む)

半導体装置およびその作製方法

【課題】ソース電極およびドレイン電極間におけるオフリーク電流の低減を課題とする。

【解決手段】本発明の一態様は、ゲート電極101と、前記ゲート電極を覆うように形成されたゲート絶縁膜102,103と、前記ゲート絶縁膜上に形成され、前記ゲート電極の上方に位置する活性層104と、前記活性層の側面及び前記ゲート絶縁膜の上に形成されたシリコン層105,106と、前記シリコン層上に形成されたソース電極107aおよびドレイン電極107bと、を具備し、前記活性層は、前記ソース電極および前記ドレイン電極それぞれと接しないことを特徴とする半導体装置である。

(もっと読む)

表示装置

【課題】酸化物半導体を用いたトランジスタを有する表示装置において、寄生容量を軽減する。表示装置において、解像度の向上や、高精細化といった高性能化及び高品質化を達成する。

【解決手段】ボトムゲート型のトランジスタにおいて、酸化物半導体膜と重畳して設けられるゲート電極が第1のゲート電極と第2のゲート電極とに間隔を有して分割して設けられる。第1のゲート電極はソース電極又はドレイン電極の一方と重畳して設けられ、第2のゲート電極はソース電極又はドレイン電極の他方と重畳して設けられる。

(もっと読む)

1 - 20 / 412

[ Back to top ]