Fターム[5F110AA03]の内容

Fターム[5F110AA03]に分類される特許

141 - 160 / 732

半導体装置および半導体装置の作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置の提供を目的の一とする。さらに、これらの微細化を達成した半導体装置の良好な特性を維持しつつ、3次元高集積化を図ることを目的の一つとする。

【解決手段】絶縁層中に埋め込まれた配線と、絶縁層上の酸化物半導体層と、酸化物半導体層と電気的に接続するソース電極及びドレイン電極と、酸化物半導体層と重畳して設けられたゲート電極と、酸化物半導体層と、ゲート電極との間に設けられたゲート絶縁層と、を有し、絶縁層は、配線の上面の一部を露出するように形成され、配線は、その上面の一部が絶縁層の表面の一部より高い位置に存在し、且つ、絶縁層から露出した領域において、ソース電極またはドレイン電極と電気的に接続し、絶縁層表面の一部であって、酸化物半導体層と接する領域は、その二乗平均平方根粗さが1nm以下である半導体装置である。

(もっと読む)

電界効果トランジスタ、およびその製造方法

【課題】高い移動度、低いオン抵抗を備えたノーマリオフ型の電界効果トランジスタを提供する。

【解決手段】III族窒化物系化合物半導体からなるチャネル層104と、前記チャネル層上に形成されたAlInGaNからなる界面層106と、前記界面層上に形成され、前記界面層に達するリセス部を備えたIII族窒化物系化合物半導体からなる電子供給層108と、前記リセス部を挟んで、前記電子供給層108上に形成されたソース電極110およびドレイン電極112と、前記リセス部の内表面に形成された絶縁膜120と、前記絶縁膜上に形成されたゲート電極114とを備える。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

半導体装置

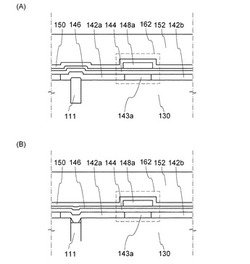

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、ソース電極またはドレイン電極は、第1の導電層と、前記ゲート電極と一部が重畳するように第1の導電層の端部よりチャネル長方向に伸長した領域を有する第2の導電層と、を含み、第2の導電層の伸長した領域の上にサイドウォール絶縁層を有し、サイドウォール絶縁層は異なる複数の材料層が積層される半導体装置である。

(もっと読む)

導電性有機ポリマーと複数のナノ粒子とを含有するバッファー層を含むデバイス

【課題】 本発明は、エレクトロルミネセンスデバイスでの使用のための高抵抗バッファー層や、マイクロエレクトロニクス用途向けの改善された特性を有する有機電子デバイスを提供することを課題とする。

【解決手段】 本発明は、導電性ポリマーと、そこに分散した複数のナノ粒子とを含む高抵抗バッファー層を含むことを特徴とする有機電子デバイスであって、

前記ナノ粒子が、有機ポリアクリル酸、カーボンナノチューブ、およびコロイド形成スルホン酸ナノ粒子ならびに、これらの混合物からなる群から選択されることを特徴とする有機電子デバイスである。

(もっと読む)

表示装置及びその製造方法

【課題】ソース・ドレイン電極に、剥離やストレスマイグレーションによるボイドが発生するのを抑制する。

【解決手段】複数の薄膜トランジスタが配列された基板を有する表示装置であって、薄膜トランジスタは、半導体層6と、半導体層6上に形成されるコンタクト層7と、コンタクト層7上に形成されるソース電極10及びドレイン電極9とを有し、ソース電極10およびドレイン電極9は、コンタクト層7の上側に形成される第1の導電層9a,10aと、第1の導電層9a,10aの上側に形成される第2の導電層9b,10bとを有し、第2導電層9b,10bは、第1添加元素と、銅とを含有する銅合金層であり、前記第1添加元素は、ジルコニウム、チタン、銀、インジウム、金、錫、クロム、ケイ素から選ばれた少なくとも1種類の元素である、ことを特徴とする表示装置。

(もっと読む)

埋立ビットラインを有する半導体装置及び半導体装置の製造方法

【課題】埋立ビットラインを有する半導体装置及び半導体装置の製造方法を提供すること。

【解決手段】埋立ビットラインを備えて低抵抗を有する垂直ピラートランジスタを含む半導体装置及びその製造方法が開示される。垂直ピラートランジスタは、基板上に形成され、下部と上部を有する本体、本体の上部に配置されるソース/ドレインノード、そして、本体の下部に配置されるドレイン/ソースノードを含む。半導体装置は、少なくとも本体の下部の上部表面に形成され、金属シリサイドを含む前記埋立ビットライン及び前記本体の上部を部分的に包むワードラインを備える。

(もっと読む)

表示装置およびその製造方法

【課題】 ボトムゲート構造のTFTを有する表示装置の生産性の低下を抑えるとともに、表示特性の劣化を抑える。

【解決手段】 複数の薄膜トランジスタが形成された基板を有する表示パネルを備え、前記薄膜トランジスタは、前記基板の上にゲート電極、ゲート絶縁膜、半導体膜の順に積層され、かつ、前記半導体膜の上にはソース電極の一部または全部およびドレイン電極の一部または全部がコンタクト膜を介して積層されており、前記コンタクト膜は、前記半導体膜と前記ソース電極との間に介在する部分および前記半導体膜と前記ドレイン電極との間に介在する部分を除いた部分が酸化されている表示装置であって、それぞれの前記コンタクト膜は、前記半導体膜と接している面の反対側が凹凸を有する曲面であり、かつ、最小膜厚が3nm以下、最大膜厚が4nm以上である表示装置。

(もっと読む)

表示装置および表示装置の製造方法

【課題】Cu合金をソース・ドレイン電極に用いたTFTにおいて、コンタクト膜に対して酸化処理を施す場合であっても、良好なオン特性を維持する表示装置を提供することを目的とする。

【解決手段】半導体層4と、銅と1種類の添加元素とを含む銅合金層を有するソース電極10およびドレイン電極9と、ソース電極10及びドレイン電極9のそれぞれの電極と半導体層4との間に形成されるコンタクト膜5と、それぞれの電極とコンタクト膜5との間に形成される酸化物膜8と、を含む薄膜トランジスタ基板を有する表示装置であって、コンタクト膜5は、不純物とシリコンとを含み、酸化物膜8は、シリコン、不純物および酸素を含むとともに、酸化物膜8における不純物濃度がコンタクト膜5における不純物濃度よりも低い、ことを特徴とする表示装置。

(もっと読む)

電界効果型トランジスタの製造方法

【課題】活性層―電極間の寄生抵抗に起因する素子特性のばらつきの少ないIGZO系電界効果型トランジスタを製造する。

【解決手段】基板B上に、IGZO系アモルファス酸化物からなる半導体層11、ソース電極22、ドレイン電極23、ゲート電極21およびゲート絶縁膜31とを備えてなる電界効果型トランジスタ1の製造方法において、半導体層11上にIGZO系アモルファス酸化物層20をスパッタ成膜により成膜し、その後アニール処理を行って、ソース電極22およびドレイン電極23の少なくとも半導体層11に接触する面側を構成する導電層を形成する。スパッタ成膜における背圧は1×10−5Pa未満とし、アニール処理におけるアニール温度を100℃以上、300℃以下とする。

(もっと読む)

薄膜トランジスタ及びその製造方法、並びに表示装置

【課題】 ソース・ドレイン電極と半導体膜との接触抵抗を低減し、移動度特性を向上した薄膜トランジスタを提供する。さらに、それを用いた高性能の表示装置を提供する。

【解決手段】 板上に形成されたゲート電極と、前記ゲート電極を覆うようにして前記基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成された半導体膜と、少なくとも各々の一部が前記半導体膜上に形成され、ソース電極及びドレイン電極として機能する一対の電極と、を具備する薄膜トランジスタであって、前記半導体膜は、GeあるいはSi及びGeを含有し、前記一対の電極の各々は、ボロンあるいはV族元素を含有する金属膜で形成され、前記一対の電極の各々と前記半導体膜との間に、ジャーマノシリサイドあるいは金属−Ge間化合物が形成されている。

(もっと読む)

半導体トランジスタの製造方法

【課題】プロセスの自由度を高めつつ、活性層とオーミックコンタクトをとるオーミック電極を形成できる半導体トランジスタの製造方法を提供する。

【解決手段】GaN系の半導体からなる活性層上に、オーミック電極を形成する半導体トランジスタの製造方法であって、活性層3上に、タンタル窒化物からなる第1の層11と、第1の層11上に積層されたAlからなる第2の層12とを形成する工程と、第1及び第2の層11,12を、520℃以上、600℃以下の温度で熱処理することにより、活性層3とオーミックコンタクトをとるオーミック電極9s,9dを形成する工程とを備える。

(もっと読む)

薄膜トランジスタ基板および表示デバイス

【課題】Cu系合金配線膜を半導体層と直接接続しても接触抵抗率が低く、かつ密着性に優れた薄膜トランジスタ基板を提供する。

【解決手段】薄膜トランジスタの半導体層33と、Cu合金層28b、29bとを有する薄膜トランジスタ基板において、前記半導体層33と前記Cu合金層28b、29bとの間に、酸素含有層28a、29aを含んでおり、前記酸素含有層28a、29aを構成する酸素の一部若しくは全部は、前記薄膜トランジスタの前記半導体層33のSiと結合しており、前記Cu合金層28b、29bは、合金元素としてX(Xは、Mn、Ni、Zn、およびMgよりなる群から選ばれる少なくとも1種)を合計で2原子%以上20原子%以下含有し、前記Cu合金層28b、29bは、前記酸素含有層28a、29aを介して前記薄膜トランジスタの前記半導体層33と接続していることを特徴とする薄膜トランジスタ基板である。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

有機電子装置のための電極処理方法

【課題】有機電子装置のための電極処理方法を提供する。

【解決手段】本発明は、有機電子(OE:organic electronic)装置、特に、有機電界効果トランジスタ(OFET:organic field effect transistor)にける電極の処理方法と、そのような方法によって調製される装置と、そのような方法において使用される材料および配合物とに関する。

(もっと読む)

電圧調整回路

【課題】トランジスタにおけるオフ電流を低減し、電圧調整回路における出力電圧の変換効率を向上させる。

【解決手段】ゲート、ソース、及びドレインを有し、ゲートがソース又はドレインに電気的に接続され、ソース及びドレインの一方に第1の信号が入力され、チャネル形成層としてキャリア濃度が5×1014/cm3以下である酸化物半導体層を有するトランジスタと、第1の電極及び第2の電極を有し、第1の電極がトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極にクロック信号である第2の信号が入力される容量素子と、を有し、第1の信号の電圧を昇圧又は降圧し、昇圧又は降圧した電圧である第3の信号を出力信号としてトランジスタのソース及びドレインの他方を介して出力する構成である。

(もっと読む)

有機半導体デバイスのコンタクト構造、有機半導体デバイス及びその作製方法

【課題】有機半導体デバイスのコンタクト抵抗を、デバイス作製プロセスをあまり複雑化することなく低下させる。

【解決手段】たとえば図示した有機半導体FETにおいて、ソースあるいはドレイン電極4から相手側の電極へ流れる電流は電極4のうちの相手側電極に近い端に集中する。この箇所に金属酸化物層5を設ける。有機半導体層3と金属酸化物層5との間の電荷移動により、電極4の電流が集中する端近傍まではキャリアが豊富でトラップの少ない領域が形成されるので、コンタクト抵抗が大幅に低下する。

(もっと読む)

表示装置

【課題】TFTと接続するソース電極あるいはドレイン電極のスルーホールにおけるコンタクト抵抗を減少させ、表示装置の動作効率を向上させる。

【解決手段】スルーホールにおいて、TFTのソース部とソース電極8が接続している。ソース電極8は、バリヤメタル、Al合金82、キャップメタル83の3層から形成されている。バリヤメタルは半導体層と接触する下層81aとAl合金と接触する上層81bとに分かれている。バリヤメタルの下層81aをスパッタリングして形成した後、熱処理し、その後、ベースメタルの上層81b、Al合金82、キャップメタル83を連続してスパッタリングによって形成する。Al合金82と接触するバリヤメタルの上層81bは酸化されていないので、スルーホールにおけるコンタクト抵抗の上昇を防止することが出来る。

(もっと読む)

光電変換装置、エックス線撮像装置及び光電変換装置の製造方法

【課題】外部接続端子の接続信頼性を向上させることができると共に、簡単な工程で製造

できるようにした光電変換装置を提供すること。

【解決手段】本発明の光電変換装置は、フォトダイオード25及びTFT24がマトリク

ス状に配置され、周辺部に複数の外部接続端子が形成され、フォトダイオードは、第1電

極251がTFT24に接続され、第2電極252がバイアス線23に接続され、バイア

ス線23がバイアス線用の外部接続端子に電気的に接続されており、バイアス線23は、

透明導電性金属酸化物で形成され、光電変換装置の光の入射面の全面に亘って形成されて

いると共に、バイアス線用の外部接続端子まで延在されて前記バイアス線用の外部接続端

子の最上部側に配置されている。

(もっと読む)

グラフェン膜と金属電極とが電気的接合した回路装置

【課題】グラフェン膜と金属電極との間の接触抵抗を低減してグラフェン膜と金属電極とが良好に電気的接合された回路装置を提供する。

【解決手段】本発明に係るグラフェン膜と金属電極とが電気的接合した回路装置は、単層または複数層からなるグラフェン膜を利用した回路装置であって、前記グラフェン膜と直接接触する下地層としての酸化アルミニウム膜が前記グラフェン膜の下部のみに形成されており、前記酸化アルミニウム膜の組成がAl2-xO3+x(x ≧ 0)であり、前記グラフェン膜と金属電極とが直接接合し、該接合箇所には凹凸構造が形成され、前記凹凸構造は、前記酸化アルミニウム膜に形成された少なくとも1つのコーン状凹部と、前記コーン状凹部を含む前記酸化アルミニウム膜の表面に沿って該表面と平行に成長した前記グラフェン膜と、前記グラフェン膜を覆いかつ前記コーン状凹部を埋めるように形成された前記金属層とから構成されていることを特徴とする。

(もっと読む)

141 - 160 / 732

[ Back to top ]