Fターム[5F110BB11]の内容

Fターム[5F110BB11]に分類される特許

1 - 20 / 325

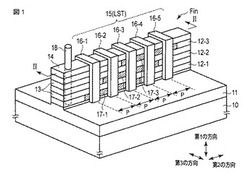

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜近傍の酸化物半導体膜に含まれる不純物元素濃度を低減する。また、ゲート絶縁膜近傍の酸化物半導体膜の結晶性を向上させる。また、当該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたソース電極、及びドレイン電極と、酸化物半導体膜、ソース電極、及びドレイン電極上に形成されたシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記酸化物半導体膜と重畳する領域に設けられたゲート電極と、を有し、酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度である領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置、及びその作製方法

【課題】良好な特性を維持しつつ微細化を達成した半導体装置を提供する。また、微細化された半導体装置を歩留まりよく提供する。

【解決手段】絶縁表面を有する基板上に設けられた酸化物半導体膜と、酸化物半導体膜の側面に接して設けられ、かつ酸化物半導体膜よりも膜厚が大きいソース電極層及びドレイン電極層と、酸化物半導体膜、ソース電極層、及びドレイン電極層上に設けられたゲート絶縁膜と、酸化物半導体膜の上面と、ソース電極層及びドレイン電極層の上面との間に生じた段差により生じた凹部に設けられたゲート電極層と、を有する構造である。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気的特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】チャネル形成領域、及びチャネル形成領域を挟む低抵抗領域を含む酸化物半導体膜、ゲート絶縁膜、及び上面及び側面を覆う酸化アルミニウム膜を含む絶縁膜が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び酸化アルミニウム膜を含む絶縁膜の上面及び側面の一部に接して設けられる。

(もっと読む)

エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法

【課題】エアギャップを備えるグラフェントランジスタ、それを備えるハイブリッドトランジスタ及びその製造方法を提供する。

【解決手段】基板上のゲート電極と、ゲート電極上のゲート絶縁層と、ゲート絶縁層上のグラフェンチャネルと、グラフェンチャネル上で互いに離隔しているソース電極及びドレイン電極と、ソース電極及びドレイン電極の上面を覆い、グラフェンチャネル上でソース電極とドレイン電極との間にエアギャップを形成するカバーと、を備えるグラフェントランジスタ。前記ソース電極と前記ドレイン電極との間の前記グラフェンチャネルの長さが、10nm〜100nmである。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】酸素欠損の発生を抑制する。

【解決手段】ガリウム(Ga)若しくはスズ(Sn)の一部又は全部の代わりにゲルマニウム(Ge)を用いて酸化物半導体膜を構成する。ゲルマニウム(Ge)原子は、酸素(Ge)原子との結合の少なくとも一つの結合エネルギーがガリウム(Ga)又はスズ(Sn)の場合よりも高い。このため、ゲルマニウム(Ge)を用いて構成される酸化物半導体結晶において、酸素欠損が発生しにくい。このことから、ゲルマニウム(Ge)を用いて酸化物半導体膜を構成することにより、酸素欠損の発生の抑制を図る。

(もっと読む)

積層型半導体装置及びその製造方法

【課題】本発明は、接続電極のピッチを大きくせずにゲートの寄生容量を小さくすることができ、回路の高速化と層間接続の高密度化の両立が図れる積層型半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1のゲート60と、該第1のゲートよりも下層に形成された第1及び第2の不純物拡散領域31、33とを有する第1の半導体素子70と、

前記第1のゲートと対向して接合された第2のゲート65と、該第2のゲートよりも上層に形成された第3及び第4の不純物拡散領域36、38とを有する第2の半導体素子75と、を有することを特徴とする。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層の溝に埋め込まれた電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設ける。チャネル形成領域は、サイドウォールを側壁に有するゲート電極層と重なる位置に形成される。溝は、深い領域と浅い領域を有し、サイドウォールは、浅い領域と重なり、配線との接続は、深い領域と重なる。

(もっと読む)

半導体装置

【課題】良好な電気特性を維持しつつ、微細化を達成した半導体装置を提供する。また、信頼性の高い半導体装置を提供する。

【解決手段】ゲート電極層をマスクとした不純物の導入処理によって自己整合的にチャネル形成領域と一対の低抵抗領域とが形成される酸化物半導体層を有し、ゲート電極層を挟んで設けられる一対の配線層が低抵抗領域と電気的に接続し、配線層が形成される領域の下部に低抵抗領域と接する電極層が設けられている半導体装置である。

(もっと読む)

半導体装置

【課題】微細化しても高いオン電流を得ることができるトランジスタを用いた、半導体装置。

【解決手段】トランジスタが、絶縁表面上の一対の第1導電膜と、一対の第1導電膜上の半導体膜と、一対の第1導電膜にそれぞれ接続されている一対の第2導電膜と、半導体膜上の絶縁膜と、絶縁膜上において、半導体膜と重なる位置に設けられた第3導電膜とを有する。また、半導体膜上における第3導電膜の端部と、一対の第2導電膜が設けられた領域とは、離隔している。

(もっと読む)

光検出装置及び光検出装置の駆動方法

【課題】ノイズによる影響を抑制する。

【解決手段】光検出回路と、差分データ生成回路と、データ入力選択回路と、を具備する。光検出回路は、光データ信号を生成する機能を有する。また、差分データ生成回路は、第1のデータ信号及び第2のデータ信号が入力され、第1のデータ信号のデータと第2の信号のデータとの差分データを生成する機能を有する。また、データ入力選択回路は、光データ信号のデータを、第1のデータ信号のデータみなすか第2のデータ信号のデータとみなすかを決定する機能を有する。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】オン電流が少ないトランジスタを含むメモリセルと積層方向に延びるビット線により、低い製造コストで高速動作を実現可能な半導体装置を提供する。

【解決手段】本発明の半導体装置は、例えば、記憶素子とその読み出し電流経路に挿入される第1のトランジスタとを含むメモリセルMCと、このメモリセルMCの一端に直接接続され、記憶素子の情報を伝送する第1のビット線LBLと、第2のトランジスタを含み第1のビット線LBLを介して伝送される記憶素子の情報を増幅する第1のアンプLSAとを備えている。第1のアンプLSAは基板L0に形成され、メモリセルMCは基板L0の上部の第1の層L1〜L8に形成され、第1のビット線LBLは積層方向に延びる配線構造を含んで形成される。第1のトランジスタのチャネル中のキャリアの移動度は、第2のトランジスタのチャネル中のキャリアの移動度よりも低い。

(もっと読む)

SOI基板の作製方法

【課題】表面のP−V値が小さく、かつ、高い結晶性を有する半導体薄膜層を備えたSOI基板の作製方法を提供する。

【解決手段】半導体薄膜層の結晶性を高く保つため、水素イオン添加処理中の半導体基板の温度を200℃以下に抑制した。加えて、水素イオン添加処理後の半導体基板を100℃以上400℃以下に保持した状態で半導体基板に対してプラズマ処理を行うことにより、水素イオン添加処理により生じる、半導体薄膜層の分離に対して寄与度の高いSi−H結合を残存させたまま、半導体薄膜層の分離に対して寄与度の低いSi−H結合を低減した。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

1 - 20 / 325

[ Back to top ]