Fターム[5F110BB20]の内容

Fターム[5F110BB20]に分類される特許

1 - 20 / 665

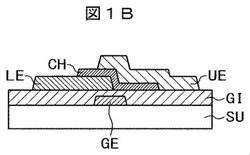

酸化物半導体装置およびその製造方法

【課題】

短いチャネル長の酸化物半導体装置およびそれを低コストで実現することのできる製造方法を提供する。

【解決手段】

酸化物半導体装置において、チャネルとなる酸化物半導体層CHと、第1方向に、酸化物半導体層CHを介して延伸する第1の電極層(ソース又はドレイン)LEおよび第2の電極層(ドレイン又はソース)UEと、第1方向と交差する第2方向に延伸し、酸化物半導体層CHと基板SUに垂直な方向においてゲート絶縁層GIを介して重なるゲート電極層GEとを有し、酸化物半導体層CHの膜厚がそのチャネル長となる。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体素子の製造方法及び半導体素子

【課題】II族酸化物半導体を用いた半導体素子における新規な絶縁層形成技術を提供する。

【解決手段】半導体素子の製造方法は、(a)基板上方に、II族酸化物半導体層を成長させる工程と、(b)II族酸化物半導体層上に、窒素をドープしつつOリッチ条件での成長を行い抵抗率が105Ωcm以上のII族酸化物絶縁層を成長させる工程とを有する。

(もっと読む)

半導体装置、モジュール、及び電子機器

【課題】大量生産上、大型の基板に適している液滴吐出法を用いた製造プロセスを提供す

る。

【解決手段】液滴吐出法で感光性の導電膜材料液を選択的に吐出し、レーザ光で選択的に

露光した後、現像またはエッチングすることによって、レーザ光で露光した領域のみを残

し、吐出後のパターンよりも微細なソース配線およびドレイン配線を実現する。TFTの

ソース配線およびドレイン配線は、島状の半導体層を横断して重ねることを特徴としてい

る。

(もっと読む)

半導体装置及び電子機器

【課題】可撓性を有する基板上に有機化合物を含む層を有する素子が設けられた半導体装置を歩留まり高く作製することを課題とする。

【解決手段】基板上に剥離層を形成し、剥離層上に、無機化合物層、第1の導電層、及び有機化合物を含む層を形成し、有機化合物を含む層及び無機化合物層に接する第2の導電層を形成して素子形成層を形成し、第2の導電層上に第1の可撓性を有する基板を貼りあわせた後、剥離層と素子形成層とを剥す半導体装置の作製方法である。

(もっと読む)

表面ポテンシャルのシミュレーション装置及び表面ポテンシャルのシミュレーションプログラム

【課題】半導体膜中にキャリアを捕獲する欠陥を含む蓄積型の電界効果型薄膜トランジスタについて、表面ポテンシャルを高速かつ高精度に計算する。

【解決手段】シミュレーション装置1は、電気的中性条件に基づいて、フラットバンド条件でのフェルミ準位を算出するフェルミ準位演算手段11と、このフェルミ準位を用いてフラットバンド条件での帯電した欠陥の密度を含む電荷担体密度を算出する電荷担体密度演算手段12と、ポアソン方程式から解析的に導出されるポテンシャルとゲート電圧との間の関係式に、半導体膜中の電荷分布が一定として表面及び裏面ポテンシャルを関連付けた近似式を代入して得た方程式に、電荷担体密度算出手段12で算出した電荷担体密度を代入して裏面ポテンシャルを算出する裏面ポテンシャル演算手段14と、裏面ポテンシャルを前記近似式に代入して表面ポテンシャルを算出する表面ポテンシャル演算手段15とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置

【課題】メモリの大容量化と図りつつ、消費電力を軽減でき、且つ、消費電力を一定にす

る。

【解決手段】メモリを、複数のメモリブロックを対称に配置して構成する。また、メモリ

に供給されるアドレス信号のうち、特定の信号の組み合わせにより、データ読み出しまた

は書き込みの対象となるメモリセルを含むメモリブロックを一意に特定する。さらに、当

該メモリブロック以外のメモリブロックに供給される信号を一定値に保つ。このようにす

ることで、メモリアレイにおけるビット線の配線長を短縮し、負荷容量を軽減すると同時

に、メモリ内のあらゆるアドレスのメモリセルに対するデータ読み出しもしくは書き込み

において、消費電流を一定にできる。

(もっと読む)

有機薄膜トランジスタ

【課題】電界効果移動度が高く、オフ電流が小さい有機薄膜トランジスタを提供することである。

【解決手段】有機半導体層の内部のうち、ソース電極の真上又は真下に位置する部分を第1の部分とし、ドレイン電極の真上又は真下に位置する部分を第2の部分とし、第1の部分と第2の部分とは異なる部分を第3の部分とした場合に、ドーピング領域が、第3の部分、第1の部分と第3の部分、又は第2の部分と第3の部分に存在する有機薄膜トランジスタである。

(もっと読む)

半導体装置

【課題】信頼性の高い半導体装置を歩留まり良く製造する技術を提供する。

【解決手段】基板上に設けられ、一対の不純物領域の間に設けられたチャネル形成領域を

含む島状の半導体層と、半導体層の側面に接して設けられた第1絶縁層と、チャネル形成

領域上に設けられ、半導体層を横断するように設けられたゲート電極と、チャネル形成領

域及びゲート電極の間に設けられた第2絶縁層と、半導体層及び前記ゲート電極上に形成

された第3絶縁層と、第3絶縁層を介して、不純物領域と電気的に接続される導電層と、

を有する。不純物領域はチャネル形成領域と比較して膜厚が大きい領域を有し、且つ該膜

厚が大きい領域で導電層が接続されている。第2絶縁層は、少なくともゲート電極が重畳

する領域の半導体層の側面に設けられた第1絶縁層を覆う。

(もっと読む)

半導体装置

【課題】小面積、低電力動作、高速動作を並立する論理ゲートを含む半導体装置の構成を提供する。

【解決手段】本発明に係る半導体装置は、基板上にゲート絶縁膜を介してゲート電極と半導体層が配置され、半導体層に接続してソース電極とドレイン電極とが配置される薄膜トランジスタを2つ以上含む論理ゲートで構成される。少なくとも第一の薄膜トランジスタは、そのゲート電極が電気的に浮遊状態にあり、かつ、その半導体層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。また、少なくとも第二の薄膜トランジスタは、そのゲート電極が入力端子に接続され、かつ、そのチャネル層は基板面に対して垂直方向について、ゲート電極とソース電極により挟まれる第1の重なり領域とゲート電極とドレイン電極により挟まれる第2の重なり領域を有する。

(もっと読む)

表示装置及び表示装置の製造方法

【課題】TFTの信頼性向上を図りつつ、良好なコントラスト特性を得ることのできる表示装置及びその製造方法を提供する。

【解決手段】本発明の表示装置は、透光性基板と、前記透光性基板の一部に形成された不純物ドープ層と、前記不純物ドープ層及び前記透光性基板上に形成された絶縁膜と、前記絶縁膜上に形成された複数のTFTを含むTFT回路と、前記TFT回路により駆動される複数のシャッターを有するシャッターアレイと、を備えることを特徴とする。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】基板と、基板上に形成されたHEMT積層物と、を備え、HEMT積層物は、2DEGを含む化合物半導体層と、化合物半導体層より分極率の大きい上部化合物半導体層と、上部化合物半導体層上に備えられたソース電極、ドレイン電極及びゲートと、を備え、基板は、シリコン基板より誘電率及び熱伝導度の高い窒化物基板であるHEMT。該基板は、シリコン基板より誘電率及び熱伝導度の高い絶縁層、この絶縁層に蒸着された金属層及びこの金属層に付着されたプレートを備える。

(もっと読む)

半導体装置

【課題】昇圧効率を向上させた昇圧回路を提供することを課題の一とする。または、昇圧効率を向上させた昇圧回路を用いたRFIDタグを提供することを課題の一とする。

【解決手段】単位昇圧回路の出力端子に当たるノード、または当該ノードに接続されたトランジスタのゲート電極をブートストラップ動作により昇圧することで、当該トランジスタにおけるしきい値電位と同等の電位の低下を防ぎ、当該単位昇圧回路の出力電位の低下を防ぐことができる。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

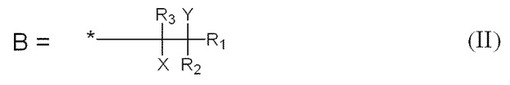

薄膜トランジスタ及びそれを用いた電子デバイス

【課題】優れた電気特性、大気安定性を有した薄膜トランジスタ及びそれを用いた電子デバイスをウェットプロセスにて作製するための、π電子共役系化合物前駆体、及びトランジスタ構造を提供する。

【解決手段】少なくとも下記一般式(I)で示される工程により得られる有機膜を用いたトップゲート型薄膜トランジスタ。

(もっと読む)

(もっと読む)

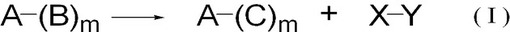

薄膜トランジスタ及びそれを用いた電子デバイス

【課題】特定構造のπ電子共役化合物前駆体を含む薄膜中の該前駆体のπ電子共役化合物への変換が、基板の耐熱温度に制限されることなく、且つ大気下で進行する、有機膜の製造方法。

【解決手段】π電子共役化合物前駆体A−(B)mを含む薄膜中の該前駆体A−(B)mが、活性エネルギー線の照射により、π電子共役系化合物A−(C)mと脱離性化合物X−Yに変換される。A−(B)m→A−(C)m+X−Y

(Aはπ電子共役系置換基、Bは溶媒可溶性置換基、mは自然数である。)

(もっと読む)

半導体記憶装置

【課題】コストを増大させずとも、書き込みに高電圧を必要とせず、不良が発生しにくく

、書き込み時間が短く、データの書換えができない半導体記憶装置を提供する。

【解決手段】ダイオード接続した第1のトランジスタと、ダイオード接続した第1のトラ

ンジスタのソース電極及びドレイン電極の一方の端子にゲートが接続する第2のトランジ

スタと、ダイオード接続した第1のトランジスタのソース電極及びドレイン電極の一方の

端子及び第2のトランジスタのゲートに接続する容量素子を有するメモリ素子を含む半導

体記憶装置である。

(もっと読む)

半導体装置の作製方法

【課題】 大面積のガラス基板上に薄膜からなる集積回路を形成し、他の基体に転写して分断を行い、接触、好ましくは非接触でデータの受信または送信が可能な微細なデバイスを大量に効率よく作製する方法を提供することを課題とする。特に薄膜からなる集積回路は、非常に薄いため移動時に飛んでしまう恐れがあり、取り扱いが難しかった。

【解決手段】 本発明は、剥離層に達する多数の穴または多数の溝を設け、穴(または溝)およびデバイス部に重ならない領域にパターン形状を有する材料体を設けた後、ハロゲン化フッ素を含む気体又は液体を導入して、前記剥離層を選択的に除去する。

(もっと読む)

1 - 20 / 665

[ Back to top ]