Fターム[5F110DD21]の内容

Fターム[5F110DD21]に分類される特許

1 - 20 / 538

半導体装置およびその製造方法

半導体素子及びその製造方法

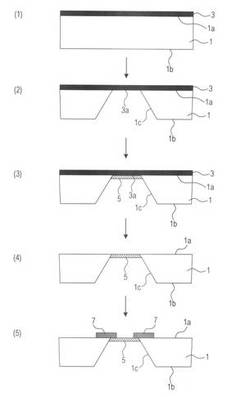

【課題】スティッキングが生じにくい半導体素子及びその製造方法を提供することを目的とする。

【解決手段】一方の面1aに触媒層3が形成された基板1において、前記一方とは反対側から前記触媒層3の裏面3aに至る開口部1cを形成する工程と、前記開口部1cにおいて、前記触媒層3の裏面3aにグラフェン5を形成する工程と、前記触媒層3の少なくとも一部を除去する工程と、を有することを特徴とする半導体素子の製造方法。開口部1cの形成後、グラフェン5の形成前に、熱処理を行うことができる。グラフェン5を形成する前に、触媒層3の表面に保護層を形成することができる。

(もっと読む)

酸化物半導体膜の作製方法、半導体装置の作製方法及び半導体装置

【課題】絶縁表面に形成される酸化物半導体膜は、下地界面近傍に非晶質領域が残存してしまい、これがトランジスタなどの特性に影響を与える要因の一つと考えられている。

【解決手段】酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜を形成する材料の融点を、酸化物半導体を構成する材料の融点よりも高くする。これにより、酸化物半導体膜に接する下地面又は酸化物半導体膜に接する膜との界面近傍まで結晶領域が存在することを可能とする。当該材料として絶縁性の金属酸化物を用いる。金属酸化物として、酸化物半導体膜を構成する材料と同族の材料である酸化アルミニウム、酸化ガリウムなどを用いる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】互いに異なる特性を備える複数の電界効果トランジスタを同一基板上に有する半導体装置の製造歩留まりを向上させる。

【解決手段】異方性のドライエッチングと等方性のウェットエッチングまたは等方性のドライエッチングとを組み合わせることにより、互いにサイドウォール長の異なる3種類のサイドウォールSWL,SWM,SWHを形成する。異方性のドライエッチングの回数を減らすことにより、配置密度の高い第3nMIS領域および第3pMIS領域において、隣り合うゲート電極GLnとゲート電極GLnとの間、隣り合うゲート電極GLnとゲート電極GLpとの間、および隣り合うゲート電極GLpとゲート電極GLpとの間の半導体基板1の削れを防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置およびその作製方法

【課題】ノーマリーオフの電気特性を有し、オン電流の高い、酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを用いた高速動作が可能な半導体装置を提供する。

【解決手段】下地絶縁膜と、下地絶縁膜上に設けられた酸化物半導体膜と、酸化物半導体膜上に設けられたゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳して設けられたゲート電極と、少なくともゲート電極を覆って設けられた、開口部を有する層間絶縁膜と、層間絶縁膜上に設けられ、開口部を介して酸化物半導体膜と接する配線と、を有し、少なくとも酸化物半導体膜と配線とが接する領域の、下地絶縁膜および酸化物半導体膜の間に、絶縁膜および絶縁膜上に設けられたバッファ層を有する半導体装置である。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 光リーク電流を抑制した高い耐光性を有するTFTを、製造工程を簡素化することにより低コストで実現する。

【解決手段】 TFT100は、絶縁基板107としてのガラス基板上に形成された遮光膜113と、遮光膜113上に形成された絶縁膜112と、絶縁膜112上に形成された半導体膜111と、半導体膜111上に形成されたゲート絶縁膜104とを基本的に有する。遮光膜113、絶縁膜112及び半導体膜111の三層から成る積層体100aは、各層が同時にパターニングされている。そして、積層体100aの各層がシリコン又はシリコンを含む材料から成る。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】ハイブリッド基板構造を有する半導体集積回路装置においては、SOI−MISFETとバルク−MISFETの混在する結果、ゲートファースト方式で両方のMISFETを作製した場合、それぞれでゲート材料に合った構造設計が必要である。バルク−MISFETはこれまでに多くの知見があり、ゲート材料変更に伴う構造変更は開発コストの増大を招くことになるため、可能な限りバルク−MISFETの構造を維持したい。また従来のゲートラスト方式でゲート電極材料の変更を行う場合は、プロセスの複雑化や製造コスト増大などの問題を招く恐れがある。

【解決手段】本願発明は、半導体基板のデバイス面上にSOI構造とバルク構造が混在するハイブリッド基板構造を有する半導体集積回路装置において、前記デバイス面を基準とするSOI型MISFETのゲート電極の高さを、バルク型MISFETのゲート電極の高さよりも高くしたものである。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を含み、高速動作が可能なトランジスタを提供する。または、該トランジスタを含む信頼性の高い半導体装置を提供する。

【解決手段】下地絶縁層中に埋め込まれ、上面の少なくとも一部が下地絶縁層から露出した電極層上に、一対の低抵抗領域及びチャネル形成領域を含む酸化物半導体層を設け、電極層において、または、酸化物半導体層の低抵抗領域であって電極層と重畳する領域において、酸化物半導体層の上層に設けられる配線層との電気的な接続を行うトランジスタを提供する。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】ソース電極層405a及びドレイン電極層405bの端部と、ゲート電極層401の端部とを重畳させ、更に酸化物半導体層403のチャネル形成領域となる領域に対して、ゲート電極層401を確実に重畳させることで、トランジスタのオン特性を向上させる。また、絶縁層491中に埋め込み導電層を形成し、埋め込み導電層481a,481bと、ソース電極層405a及びドレイン電極層405bとの接触面積を大きくとることで、トランジスタのコンタクト抵抗を低減する。ゲート絶縁層402のカバレッジ不良を抑制することで、酸化物半導体層403を薄膜化し、トランジスタの微細化を実現する。

(もっと読む)

高電子移動度トランジスタ及びその製造方法

【課題】高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】高電子移動度トランジスタ(HEMT)及びその製造方法に係り、該高電子移動度トランジスタは、基板と、基板から離隔された位置に備わった高電子移動度トランジスタ積層物と、基板と高電子移動度トランジスタ積層物との間に位置した疑似絶縁層と、を含み、該疑似絶縁層は、異なる相の少なくとも2つの物質を含む。前記異なる相の少なくとも2つの物質は、固体物質と非固体物質とを含む。前記固体物質は、半導体物質であり、前記非固体物質は、空気である。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減する。オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。高速動作が可能な半導体装置を提供する。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、酸化物半導体膜に窒素プラズマ処理を行うことで酸化物半導体膜を構成する酸素の一部が窒素に置換された酸窒化領域を形成し、該酸窒化領域に接して金属膜を形成する。該酸窒化領域は酸化物半導体膜の他の領域と比べ低抵抗となり、また、接触する金属膜との界面に高抵抗の金属酸化物を形成しにくい。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ドレイン−ソース間のリーク電流が少なく、かつ、ノーマリーオフの半導体装置を提供する。

【解決手段】基板11の上に形成された不純物元素を含む第1の半導体層13と、第1の半導体層13の上に形成された第2の半導体層16と、第2の半導体層16の上に形成された第3の半導体層17と、第3の半導体層17の上に形成されたゲート電極21、ソース電極22及びドレイン電極23と、を有し、第2の半導体層16において、ゲート電極21の直下には、第1の半導体層13と接し、第1の半導体層13に含まれる不純物元素が拡散している不純物拡散領域15が形成されており、不純物元素は、不純物拡散領域がp型となる元素であることを特徴とする半導体装置。

(もっと読む)

半導体装置及びその製造方法

【課題】動作速度を向上し消費電力を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に第1の領域を画定する第1の素子分離絶縁膜と、半導体基板の第1の領域に形成された第1導電型の第1の導電層と、半導体基板上に形成され、第1の領域の一部である第2の領域に第1の導電層に接続して形成された第1導電型の第2の導電層と、第1の領域の他の一部である第3の領域に第1の導電層に接続して形成された第1導電型の第3の導電層とを有する半導体層と、半導体層内に設けられ、第2の導電層と第3の導電層とを分離する第2の素子分離絶縁膜と、第2の導電層上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成され、第3の導電層を介して第1の導電層に電気的に接続されたゲート電極とを有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】GaとSiとの反応を抑制することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、Si基板1と、Si基板1の表面に形成されたSi酸化層3と、Si酸化層3上に形成され、Si酸化層3の一部を露出する核形成層2と、Si酸化層3及び核形成層2上に形成された化合物半導体積層構造9と、が設けられている。

(もっと読む)

薄膜トランジスタおよび電子機器

【課題】性能向上を容易に実現することが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、ゲート電極と、そのゲート電極から分離絶縁層を介して離間された半導体層と、その半導体層に接続されると共に互いに離間されたソース電極およびドレイン電極とを備える。ソース電極とドレイン電極との間においてゲート電極とソース電極およびドレイン電極とが重ならない第1領域における分離絶縁層の厚さは、ゲート電極とソース電極およびドレイン電極のうちの少なくとも一方とが重なる第2領域における分離絶縁層の厚さよりも小さい。

(もっと読む)

論理回路および半導体装置

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅1

μmあたりのオフ電流が1×10−13A以下であるトランジスタを有し、入力信号とし

て、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力され

た第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を

出力信号として出力する構成とする。

(もっと読む)

1 - 20 / 538

[ Back to top ]