Fターム[5F110DD30]の内容

Fターム[5F110DD30]に分類される特許

1 - 20 / 53

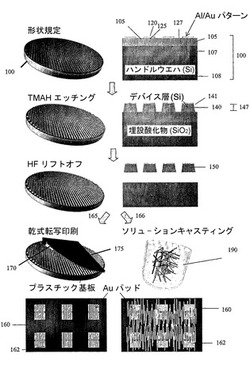

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

【課題】印刷可能半導体素子を製造するとともに、印刷可能半導体素子を基板表面上に組み立てるための方法及びデバイスを提供する。

【解決手段】デバイス、デバイス部品は、幅広いフレキシブル電子デバイス及び光電子デバイス並びにデバイスの配列を高分子材料を備える基板上に形成する。伸張形態で良好な性能が得られる伸縮可能な半導体構造及び伸縮可能な電子デバイスを形成する。

(もっと読む)

回路及び回路の駆動方法

【課題】消費電力を低減する。

【解決手段】入力信号を元に論理演算処理を行い、論理演算処理の結果に応じて設定される電位を記憶データとして保持し、記憶データに応じた値の信号を出力信号として出力する機能を有する演算回路を具備し、演算回路は、論理演算処理を行う演算部と、記憶データの電位を、論理演算処理の結果に応じた電位に設定するか否かを制御する第1の電界効果トランジスタと、記憶データの電位を、基準電位に設定するか否かを制御する第2の電界効果トランジスタと、記憶データに応じた値の信号を出力信号として出力するか否かを制御する第3の電界効果トランジスタと、を備える。

(もっと読む)

薄膜トランジスタの製造装置およびその製造方法

【課題】フレキシブルな基板を用いても、高い精度で薄膜トランジスタを形成することができる薄膜トランジスタの製造装置およびその製造方法を提供する。

【解決手段】本発明は、基板上に薄膜トランジスタを製造する製造装置であり、基板に関する基板情報を取得する取得部と、取得部で得られた基板に関する基板情報に基づいて、基板の伸縮強度が高い方向を特定し、伸縮強度が高い方向と薄膜トランジスタのチャネル領域を挟んでソース電極およびドレイン電極が配置される配置方向とが直交するように薄膜トランジスタを形成する向きを設定する設定部とを有する。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

半導体装置及びその製造方法、並びにSOI基板及びその製造方法

【課題】コンタクトホールの形成領域が素子分離領域と重複しても、素子特性の劣化を抑制できるSOI基板とこのSOI基板を用いた半導体装置とを提供する。

【解決手段】半導体装置1は、半導体基材11と埋め込み絶縁膜12と半導体層16とを有するSOI基板と、このSOI基板上に形成された半導体素子構造とを備える。埋め込み絶縁膜12は、半導体基材11から半導体層16を電気的に絶縁分離する機能を有し、窒化膜14を有する。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】

製造プロセスのステップ数を少なくでき、素子の構造が簡単でコストを抑制することが可能な薄膜トランジスタを提供する。

【解決手段】本発明の薄膜トランジスタ100は、主面を有する基材110と、前記基材110の前記主面に対する積層方向に配設される遮光層111と、前記積層方向からみて、前記遮光層111に含まれるように設けられる有機半導体層150と、前記有機半導体層150と接触するように設けられ、互いに対向しチャネル領域を形成するソース電極120及びドレイン電極130と、前記積層方向からみて、前記有機半導体層150の外周において前記ソース電極120と前記ドレイン電極130と重畳しない溝部165が設けられたゲート絶縁層160と、前記積層方向からみて前記有機半導体層150を含むように、前記ゲート絶縁層160上及び前記溝部165に設けられるゲート電極140と、からなることを特徴とする。

(もっと読む)

薄膜トランジスタ形成用基板、半導体装置、電気装置

【課題】多層基板内にTFT素子の構成要素のうちの少なくとも1つを内蔵させることによって薄膜トランジスタの高精細化を実現できる薄膜トランジスタ形成用基板、半導体装置、電気装置を提供する。

【解決手段】本発明の第1基板30(素子基板300)は、表面に制御トランジスタの構成要素の少なくとも一部を備え、内部には制御トランジスタの構成要素に接続される走査線66、データ線68、保持容量線、保持容量が埋め込まれていることを特徴とする。

(もっと読む)

半導体装置、および半導体装置の製造方法

【課題】同一の極性を有する複数の薄膜FETの閾値電圧に差をつけて、半導体装置の性能の最適化を図ることができる。

【解決手段】半導体基板1と、半導体基板1上に設けられた埋め込み絶縁膜2と、埋め込み絶縁膜2上に形成された薄膜n型FET100と、埋め込み絶縁膜2上に形成された薄膜p型FET101と、埋め込み絶縁膜2上に形成された薄膜n型FET100bと、薄膜n型FET100のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4と、薄膜p型FET101のチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域5と、薄膜n型FET100bのチャネル領域8と平面視で重なるように半導体基板1に設けられたp型ウェル領域4bと、を備え、p型ウェル領域4、4b、5は、n型ウェル領域40によって囲まれており、かつ互いに接触していない。

(もっと読む)

ダイヤモンド電子素子及びその製造方法

【課題】欠陥密度が低減したドリフト層を有する高出力ダイヤモンド電子素子を提供する。

【解決手段】半絶縁性単結晶ダイヤモンド基板の一方の面に、p−ダイヤモンド層からなるドリフト層を成膜し、該ドリフト層の上にp+ダイヤモンド層からなるコンタクト層を成膜する工程と、前記基板の他方の面に開口部をエッチングにより形成して、前記基板を構造保持材として前記ドリフト層の一部が露出した露出部を形成する工程と、前記露出部にカソード電極を設け、前記コンタクト層にアノード電極を設ける工程とにより、ダイヤモンド電子素子の積層構造を形成する。ドリフト層を基板上に直接成膜するので、欠陥密度の減少した素子を得ることができる。

(もっと読む)

半導体素子、半導体装置及び半導体素子の作製方法

【課題】半導体領域に酸化物半導体を用いた、高耐圧で、大電流の制御が可能であり、かつ量産性に優れた半導体素子を提供することを課題の一とする。また、該半導体素子を用いた半導体装置を提供することを課題の一とする。また、該半導体素子の作製方法を提供することを課題の一とする。

【解決手段】半導体領域に酸化物半導体を用いたトランジスタと、トランジスタのゲート電極層、ソース電極層及びドレイン電極層の各々と電気的に接続した貫通電極を備えた半導体チップを積層し、トランジスタを電気的に並列接続することによって、実質的にW長の長い半導体素子を提供する。

(もっと読む)

半導体装置

【課題】デカップリング容量及びガードリング等のノイズを低減する構造物を設けるための専用配置領域を必要としない半導体集積回路装置を提供する。

【解決手段】P−型シリコンからなる支持基板2を設け、この支持基板2上にP+型シリコン層3を設け、その上にN+型シリコン層4及びP+型シリコン層12を相互に同層に設ける。P+型シリコン層3及びN+型シリコン層4の不純物濃度は支持基板2の不純物濃度よりも高くする。また、N+型シリコン層4及びP+型シリコン層12上の全面に、埋込酸化膜5及びSOI層6を設ける。そして、P+型シリコン層3を接地電位配線GNDに接続し、N+型シリコン層4を電源電位配線VDDに接続する。これにより、P+型シリコン層3とN+型シリコン層4との間に、電源に並列に接続されたデカップリング容量C1が形成される。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体を用いたトランジスタにおいて、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】チャネルを形成する脱水化または脱水素化された酸化物半導体層に接する絶縁層に、シリコン過酸化ラジカルを含む絶縁層を用いる。絶縁層から酸素が放出されることにより、酸化物半導体層中の酸素欠損及び絶縁層と酸化物半導体層の界面準位を低減することができ、電気的特性の変動が小さく、信頼性の高い半導体装置を作製することができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】信頼性および再現性が優れるとともに、歩留まりが高く生産性が優れた薄膜トランジスタおよびその製造方法を提供する。

【解決手段】薄膜トランジスタの製造方法は、基板上にゲート電極を形成する工程と、ゲート電極を覆って基板上に第1の絶縁膜を形成し、第1の絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第2の絶縁膜を形成して、第1の絶縁膜、酸化物半導体膜および第2の絶縁膜からなる積層体を得る工程と、積層体の第1の絶縁膜、酸化物半導体膜および第2の絶縁膜をパターニングして、それぞれゲート絶縁層、活性層およびチャネル保護層を形成する工程と、ソース電極およびドレイン電極を形成する工程とを有する。第1の絶縁膜、酸化物半導体膜および第2の絶縁膜は、大気に曝されることなく連続して形成される。

(もっと読む)

薄膜トランジスタ、その製造方法、及び表示装置並びに電子機器

【課題】製造コストが少なく、光リーク電流が抑制された薄膜トランジスタを提供する。

【解決手段】透明基板上に作製される薄膜トランジスタであって、透明基板上に、少なくともチャネル領域と重畳しないように配置された遮光膜、下地層、結晶性シリコン膜、ゲート絶縁膜、ゲート電極膜を順次形成してなるトップゲート型結晶性シリコン薄膜トランジスタの構造を具え;結晶性シリコン膜には、チャネル長Lのチャネル領域、それを挟むLDD長dのLDD領域、ソース領域、ドレイン領域が形成されており;遮光膜はチャネル領域を挟んで分割されており;分割された遮光膜の間隔xは、チャネル長L以上、チャネル長LとLDD長dの2倍の和(L+2d)以下に選択されていることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】貼り合わせSOI基板を使用せずに、容易なプロセスにより、高速なMIS電界効果トランジスタを提供する。

【解決手段】p型のSi基板1上に、一部に空孔4を有するシリコン酸化膜2が設けられ、空孔4を挟んでシリコン酸化膜2上に延在したp型のSOIC基板(Si)5が設けられ、シリコン窒化膜3により素子分離されている。空孔4に自己整合して、SOIC基板5上にゲート酸化膜10を介してゲート電極11が設けられ、ゲート電極11の側壁にサイドウォール12が設けられ、SOIC基板5には、ゲート電極11に自己整合してn型ソースドレイン領域(7、8)及びサイドウォール12に自己整合してn型ソースドレイン領域(6、9)が設けられ、n型ソースドレイン領域には、バリアメタル15を有する導電プラグ16を介してバリアメタル18を有するCu配線19が接続されている構造からなるNチャネルのMIS電界効果トランジスタ。

(もっと読む)

薄膜トランジスタ組成物およびこれに関する方法

【課題】薄膜トランジスタ組成物およびこれに関する方法を提供する。

【解決手段】少なくとも1つのトランジスタを基板上に形成する方法が記載されている。基板は、ポリイミドおよびナノスケールの充填材を含む。ポリイミドは、実質的にまたは完全に剛直性モノマーから誘導され、ナノスケール充填材は、少なくとも3:1のアスペクト比を有する。本開示の基板は、少なくとも部分的に、引湿性膨張に対する高い耐性、ならびに、比較的高いレベルの熱安定性および寸法安定性により、薄膜トランジスタ用途に特に良好に適している。

(もっと読む)

スイッチングシステム及びスイッチング方法

本発明は無線周波数システム及び方法に関する。無線周波数(RF)システムは、バルク基板領域及び埋設酸化物領域を備えるシリコンオンインシュレータ(SOI)上に実装された、少なくとも1つ又は複数のRF信号をスイッチングするための複数のトランジスタスイッチング素子を備えるRFスイッチを具備する。少なくとも1つのフィルタが、基板及び/又はRFシステムに存在する他の高周波信号若しくは制御信号からRF信号を絶縁するように構成される。トランジスタスイッチ素子の線形性を改善するために、フィルタと協働するように構成された結合キャパシタも提供される。 (もっと読む)

フレキシブル半導体装置およびその製造方法

【課題】生産性に優れたフレキシブル半導体装置を提供する。

【解決手段】表面12aに第1の銅層23が形成されたフレキシブル基板10を用意する工程(a)と、第1の銅層23をパターニングすることによって、フレキシブル基板10の表面12aにゲート電極20gを形成する工程(b)と、フレキシブル基板10の表面12aの上に、少なくとも表面に接着性がある絶縁層30を転写によって形成する工程(c)と、フレキシブル基板10における表面12aの絶縁層30の上に、第2の銅層25を積層する工程(d)と、フレキシブル基板10の表面12aの上の第2の銅層25をパターニングすることによってソース電極20s及びドレイン電極20dを形成する工程(e)と、を含む、フレキシブル半導体装置100の製造方法である。

(もっと読む)

1 - 20 / 53

[ Back to top ]