Fターム[5F110EE38]の内容

Fターム[5F110EE38]に分類される特許

1 - 20 / 538

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

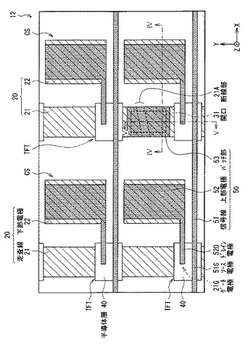

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置の製造方法

【課題】絶縁膜上に良質のグラフェンを形成しうる半導体装置の製造方法を提供する。

【解決手段】第1の基板上に触媒金属膜を形成する工程と、触媒金属膜を触媒としてグラフェンを形成する工程と、グラフェン上に第1の絶縁膜を形成する工程と、第1の絶縁膜上に第1の金属膜を形成する工程と、第2の基板上に、第2の金属膜を形成する工程と、第1の金属膜の表面と第2の金属膜の表面とを対向させ、第1の金属膜と第2の金属膜とを接合する工程と、第1の基板を除去する工程とを有する。

(もっと読む)

半導体素子基板の製造方法および半導体素子基板並びに表示装置

【課題】結晶異方性を有する領域と結晶異方性を有さない領域とを含む結晶化半導体膜を用いて薄膜トランジスタの集積化を容易に行なうことができる半導体素子基板の製造方法および半導体素子基板を提供する。

【解決手段】絶縁基板上に成膜した非晶質半導体膜56の下方に加熱促進層30を形成した領域と、加熱促進層30を形成しない領域とを設け、非晶質半導体膜56にレーザビーム18を照射する。このとき、加熱促進層30によってレーザビーム18が反射または吸収されることにより、非晶質半導体膜56は裏面側からも結晶化が促進される。これにより、加熱促進層30が形成された領域には結晶の配向が揃った第1の結晶性半導体膜54が形成され、形成されない領域には結晶の配向がランダムな第2の結晶性半導体膜55が形成される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

半導体装置の作製方法及び半導体装置

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体層と電気的に接続するソース電極層及びドレイン電極層を、酸化物半導体層上のゲート絶縁層及び絶縁層の開口を埋め込むように設ける。ソース電極層を設けるための開口とドレイン電極層を設けるための開口は、それぞれ別のマスクを用いた別のエッチング処理によって形成される。これにより、ソース電極層(またはドレイン電極層)と酸化物半導体層が接する領域と、ゲート電極層との距離を十分に縮小することができる。また、ソース電極層またはドレイン電極層は、開口を埋め込むように絶縁層上に導電膜を形成し、絶縁層上の導電膜を化学的機械研磨処理によって除去することで形成される。

(もっと読む)

半導体装置

【課題】画素部に形成される画素電極や走査線(ゲート線)及びデータ線の配置を適したものとして、かつ、マスク数及び工程数を増加させることなく高い開口率を実現した画素構造を有するアクティブマトリクス型表示装置を提供する。

【解決手段】半導体膜107と基板との間に第1の絶縁膜を介して設けられた第1の配線102を、半導体膜107と重ねて設け、遮光膜として用いる。さらに半導体膜上にゲート絶縁膜として用いる第2の絶縁膜を形成し、第2の絶縁膜上にゲート電極と第2の配線134を形成する。第1及び第2の配線は、第1及び第2の絶縁膜を介して交差する。第2の配線134の上層には、層間絶縁膜として第3の絶縁膜を形成し、その上に画素電極147を形成する。画素電極147は、第1の配線及び第2の配線とオーバーラップさせて形成することが可能であり、反射型の表示装置において画素電極147の面積を大型化できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造のトランジスタを歩留まりよく提供する。また、該トランジスタのオン特性を向上させ、高速応答、高速駆動が可能な半導体装置を提供する。

【解決手段】酸化物半導体層、ゲート絶縁層、ゲート電極層、絶縁層、導電膜、層間絶縁層が順に積層され、該導電膜を切削することにより、該ゲート電極層及び該絶縁層上の導電膜を除去して、自己整合的に形成されるソース電極層及びドレイン電極層を有し、ソース電極層及びドレイン電極層と接する領域と重畳して酸化物半導体層と接する電極層を設ける。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であっても高い電気特性を有するトランジスタを歩留まりよく提供する。該トランジスタを含む半導体装置においても、高性能化、高信頼性化、及び高生産化を達成する。

【解決手段】酸化物半導体膜、ゲート絶縁膜、及び側面に側壁絶縁層が設けられたゲート電極層が順に積層されたトランジスタを有する半導体装置において、ソース電極層及びドレイン電極層は、酸化物半導体膜及び側壁絶縁層に接して設けられる。該半導体装置の作製工程において、酸化物半導体膜、側壁絶縁層、及びゲート電極層上を覆うように導電膜及び層間絶縁膜を積層し、化学的機械研磨法によりゲート電極層上の層間絶縁膜及び導電膜を除去してソース電極層及びドレイン電極層を形成する。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

半導体装置

【課題】インバータ回路を構成する直列接続された素子を備えた半導体装置において、その直列接続の高電位配線の影響による耐圧低下が生じるのを防止する半導体装置の提供。

【解決手段】第1および第2の素子は、各々、電流のスイッチングを行うトランジスタと、還流を行うダイオードとを含み、かつ、トランジスタの第1主電極とダイオードの第1主電極が電気的に接続され、トランジスタの第2主電極とダイオードの第2主電極が電気的に接続され、第1の素子および第2の素子は、第1の素子におけるトランジスタの第1主電極と、第2の素子におけるトランジスタの第2主電極が電気的に接続され、かつ、半導体基板を平面視したときに、第1の素子におけるトランジスタの第1主電極とドリフト領域の間の導電性半導体領域と、第2の素子におけるトランジスタの第2主電極とドリフト領域の間の導電性半導体領域とが対向するように、配置されていることを特徴とする。

(もっと読む)

駆動用回路基板およびその製造方法並びに表示装置および電子機器

【課題】工程数が少なく、且つ、材料の利用効率が向上した駆動用回路基板およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本開示の表示装置は、一対のソース・ドレイン電極と、チャネル領域を形成すると共に、ソース・ドレイン電極に接して設けられた有機半導体層と、ソース・ドレイン電極まで貫通する貫通孔を有すると共に、有機半導体層およびソース・ドレイン電極上に設けられた少なくとも1層からなる絶縁層と、チャネル領域に対応する位置に設けられたゲート電極と、貫通孔を介して前記ソース・ドレイン電極に電気的に接続されると共に、ゲート電極と同一材料、且つ、同一膜厚で絶縁層上に設けられた画素用電極とを備える。

(もっと読む)

積層型半導体装置及びその製造方法

【課題】本発明は、接続電極のピッチを大きくせずにゲートの寄生容量を小さくすることができ、回路の高速化と層間接続の高密度化の両立が図れる積層型半導体装置及びその製造方法を提供することを目的とする。

【解決手段】第1のゲート60と、該第1のゲートよりも下層に形成された第1及び第2の不純物拡散領域31、33とを有する第1の半導体素子70と、

前記第1のゲートと対向して接合された第2のゲート65と、該第2のゲートよりも上層に形成された第3及び第4の不純物拡散領域36、38とを有する第2の半導体素子75と、を有することを特徴とする。

(もっと読む)

酸化物半導体膜及び半導体装置

【課題】バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を提供する。また、バンドギャップが大きく、且つ結合エネルギーを安定な状態にする酸化物半導体膜を具備する半導体装置を提供する。

【解決手段】インジウム、ランタン、亜鉛及び酸素を有する結晶構造の酸化物半導体膜とする。また、当該結晶構造において、ランタンは酸素が6配位した構造とし、インジウムは酸素が5配位した構造とする。酸化物半導体膜の結晶構造中にランタンを用いることで、インジウム、ガリウム、亜鉛及び酸素を有する結晶構造の酸化物半導体膜よりもバンドギャップが大きく、結合エネルギーを大きくした酸化物半導体膜とすることができる。また、該酸化物半導体膜を用いた半導体装置の特性を向上させることができる。

(もっと読む)

発光装置

【課題】開口部をシンプルにしてシュリンクの問題を解決する。

【解決手段】駆動トランジスタと、スイッチングトランジスタと、消去用トランジスタと、を画素内に有する3トランジスタ型の発光装置の場合において、スイッチング用TFT5505と消去用TFT5506の2つのTFTを、第1のゲート信号線5502と第2のゲート信号線5503の間に配置する。このように配置することで開口率を上げ、開口部もシンプルな形状にすることが出来る。

(もっと読む)

半導体装置

【課題】トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供する。

【解決手段】酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたコプレナー型のトランジスタにおいて、該ゲート電極層は、該第1の導電層と該ゲート絶縁層を介して重畳し、該第2の導電層と前記ゲート絶縁層を介して非重畳とする。

(もっと読む)

半導体装置

【課題】チップ面積を増大させずにスナップバック現象を抑制することのできる、IGBTと他の半導体素子とが一体化して配置された半導体装置を提供する。

【解決手段】IGBTとドリフト層を有する他の半導体素子とを備えた半導体装置であって、IGBTのドリフト層と他の半導体素子のドリフト層とが互いに接しており、IGBTのエミッタ層と他の半導体素子のドリフト電界を発生させる電圧が印加される一方の極性層とが互いに導電的に接続されており、IGBTのコレクタ層と他の半導体素子の他方の極性層とが互いに導電的に接続されており、IGBTのドリフト層の他の半導体素子のドリフト層との境界から離れた領域に絶縁層を介して対向する領域をドリフト方向に沿って延伸し、Nチャネル型IGBTではコレクタ側からエミッタ側に向けて電流が流され、Pチャネル型IGBTではエミッタ側からコレクタ側に向けて電流が流される配線部が設けられている。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離構造の上面の周縁部にディボットが形成されても、このディボットに起因するゲート絶縁膜の破壊を防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、トレンチ分離構造20Bと、トレンチ分離構造20Bで区画される活性領域上に形成されたゲート絶縁膜30と、ゲート絶縁膜30の上面からトレンチ分離構造20Bの上面まで延在するゲート電極層31と、ゲート電極層31の両側に形成された第1及び第2の不純物拡散領域13D,13Sとを備える。ゲート電極層31は、ゲート絶縁膜30と第1の不純物拡散領域13Dとの間の領域に貫通孔31hを有し、貫通孔31hは、トレンチ分離構造20Bの上面の周縁部の直上に形成されている。

(もっと読む)

1 - 20 / 538

[ Back to top ]