Fターム[5F110EE41]の内容

Fターム[5F110EE41]の下位に属するFターム

Fターム[5F110EE41]に分類される特許

1 - 20 / 180

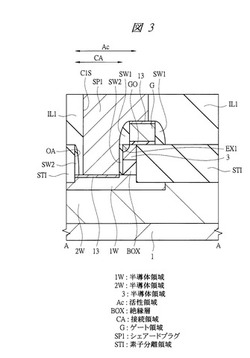

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

集積装置

【課題】

形状に限定されることなく、柔軟性ないし可撓性を有し、任意の形状の各種装置を作成することが可能な素子を用いた集積装置を提供すること。

【解決手段】

回路素子が長手方向に連続的又は間欠的に形成されている素子、回路を形成する複数の領域を有する断面が長手方向に連続的又は間欠的に形成されている素子を複数複数束ね、撚り合せ、織り込み又は編み込み、接合し、組み合わせて成形加工し又は不織状に成形したことを特徴とする。

(もっと読む)

薄膜素子組立体

【課題】巻き取りを行っても傷や損傷が発生し難い構成、構造を有する薄膜素子組立体を提供する。

【解決手段】薄膜素子組立体にあっては、可撓性を有する基材20の第1面21上に複数の薄膜素子10が備えられており、基材20において、複数の薄膜素子10が備えられた第1領域の外側に、薄膜素子を備えていない第2領域が設けられており、基材20の第1面21の第2領域、又は、第2面22の第2領域、又は、第1面21及び第2面22の第2領域に凸部31が形成されている。

(もっと読む)

液晶表示装置及び液晶表示装置の作製方法

【課題】新規な電極構造を有する、横電界方式の液晶表示装置とその作製方法の提案。

【解決手段】絶縁表面を有する第1基板と、絶縁表面上の第1導電膜及び第2導電膜と、第1導電膜上の第1絶縁膜と、第2導電膜上の第2絶縁膜と、第1基板と対峙する第2基板と、第1基板と第2基板の間に位置する液晶層と、を有し、第1導電膜の一部は第1絶縁膜の側部にも位置し、なおかつ、第2導電膜の一部は第2絶縁膜の側部にも位置し、液晶層は、ブルー相を示す液晶を含んでいる液晶表示装置。

(もっと読む)

半導体装置

【課題】SOI−MISFETにおいて、多結晶シリコンの残存による電気的な短絡、ゲート電極の寄生容量の増大を防止する。逆狭チャネル効果の抑制。

【解決手段】シリコン膜13を有するSOI基板上にゲート絶縁膜14、第1の多結晶シリコン膜15、ストッパー窒化膜(16)を順次堆積する。シリコン膜13、第1の多結晶シリコン膜15の側面に逆テーパー面(テーパー角θが鈍角)が形成されるようにエッチングして素子分離溝を形成する。STI埋め込み絶縁膜17を堆積し、CMPにより平坦化した後、等速性のRIEによりストッパー窒化膜(16)と絶縁膜17をエッチングして平坦な表面を得、その上に第2の多結晶シリコン膜18を堆積し(e)、積層多結晶シリコン膜をエッチングして積層ゲート電極(15、18)を形成する(f)。以下、ソース・ドレイン領域21、シリサイド膜22、層間絶縁膜23及びメタル配線24等を形成する(g)。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留まりの低下を抑制する半導体装置及びその製造方法を提供する。

【解決手段】実施の形態の半導体装置1は、配線20を有する配線層11bと、配線層11b上に形成された層間絶縁膜26と、層間絶縁膜26上に形成され、上部がシリサイド化されたアモルファスシリコン層27を有するTFT14と、TFT14上に、層間絶縁膜47を介して形成された配線50を有する配線層12aと、層間絶縁膜47、アモルファスシリコン層27及び層間絶縁膜26を貫通し、第1及び第2の配線を電気的に接続するコンタクトプラグ32と、を備える。

(もっと読む)

電子回路付き基板及びその製造方法、並びに混合型電子回路形成キット

【課題】DNA又はDNA−脂質複合体を用いた簡易な方法により、基板上に導電性パターンを、画像流れを抑制しながら安定して形成できる電子回路付き基板の製造方法を提供する。

【解決手段】基板上に、DNA又はDNA−脂質複合体を含む溶液を描画することによって電子回路パターンを形成する工程と、前記電子回路パターンが形成された基板を多価金属イオン溶液に浸漬することによって、前記電子回路パターンにおいて、前記DNA又は前記DNA−脂質複合体と前記多価金属イオンとの錯体を形成する工程と、形成された錯体中の金属イオンを還元することによって、前記電子回路パターンを導電性パターンとする工程と、を有する電子回路付き基板の製造方法である。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて製造することが可能な電界効果トランジスタを提供する。

【解決手段】ソース領域144及びドレイン領域146並びにチャネル領域142を含む酸化物導電体層140と、チャネル領域142の導通状態を制御するゲート電極120と、ゲート電極120とチャネル領域142との間に形成され強誘電体材料からなるゲート絶縁層130とを備え、チャネル領域142の層厚は、ソース領域144の層厚及びドレイン領域146の層厚よりも薄い電界効果トランジスタ。酸化物導電体層140は、型押し成形技術を用いて形成されている。

(もっと読む)

薄膜電界効果型トランジスタの製造方法

【課題】TFT特性が良好であり、しかも面内均一性等も良好な薄膜電界効果型トランジスタを低コストで提供すること。

【解決手段】基板上に、少なくともゲート電極、絶縁膜、活性層、ソース電極およびドレイン電極が形成され、活性層上にソース電極およびドレイン電極が設けられた薄膜電界効果型トランジスタの製造方法である。本発明の製造方法は、エッチング液として、りん酸、酢酸および硝酸を含む混酸水溶液を用いて、ソース電極およびドレイン電極を形成する工程を有する。この活性層は、In、GaおよびZnを含むアモルファス酸化物半導体で構成されるものであり、かつZn濃度が20%未満であり、In濃度が40%以上であり、Ga濃度が37%以上である。

(もっと読む)

SeOIの連想メモリでデータを比較するデバイス

【課題】連想メモリの比較デバイス、比較デバイスを制御する方法、および連想メモリを提供する。

【解決手段】データビットを格納する第1のトランジスタT1およびデータビットの補数を格納する第2のトランジスタT2によって形成されたメモリセルであって、各トランジスタは、セミコンダクタ・オン・インシュレータ基板上に作られ、各々は、フロント制御ゲート、およびトランジスタを遮断するように制御するバック制御ゲートBG1、BG2を有する、メモリセルと、各々のフロント制御ゲートに公称読出し電圧を加えることによって読出しモードで動作させ、一方、バック制御ゲートBG1、BG2を、一方をビット(DATA)、他方をビットの補数(DATAb)で制御し、ビット(DATA)と格納されたビットが一致する場合には各々のうちの通過トランジスタを遮断し、各々のソースに連結されたソース線SLの電流の有無を検出する比較回路を備える。

(もっと読む)

半導体装置の製造方法

【課題】ポリシリコンゲート電極の意図しないフルシリサイド化を防止する。

【解決手段】基板17上に、ゲート絶縁膜12およびシリコン層10をこの順に積層した積層体(10、12)を形成する工程と、積層体(10、12)の側壁沿いにSiN膜を有するオフセットスペーサ13を形成する工程と、その後、シリコン層10の上面を、薬液を用いて洗浄する工程と、その後、少なくともシリコン層10の上面を覆う金属膜19を形成する工程と、その後、加熱する工程と、を有し、オフセットスペーサ13が有するSiN膜は、ALD法を用いて450℃以上で成膜されたSiN膜、または、1Gpa以上の引張/圧縮応力を有するSiN膜であり、前記薬液は、重量比率で、HF/H2O=1/100以上であるDHF、または、バッファードフッ酸である半導体装置の製造方法を提供する。

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】 微結晶Si薄膜トランジスタの光リーク電流を抑制し、液晶ディスプレイ等の光照射下で使用する場合に、クロストークやコントラストの低下等の表示特性の劣化を低減する。

【解決手段】 基板上に設けられたゲート電極と、ゲート電極を被覆するように設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられ、微結晶Si層と非晶質Si層とを含むチャネル層と、チャネル層上の一方に設けられたソース電極と、チャネル層上の他方に設けられたドレイン電極とを備えた薄膜トランジスタに関する。そして、この実施形態において、ソース電極およびドレイン電極の夫々は、第1の層と、前記第1の層よりも下側に設けられた第2の層とを含み、前記第2の層は第1の層よりも反射率が低い導電膜の層で構成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ゲート電極にシリサイドを形成しつつ、拡散領域に接続するコンタクトとゲート電極の間隔を確保する。

【解決手段】被覆絶縁膜120は、ゲート電極140のチャネル幅方向における少なくとも一部上に形成されている。拡散領域170は素子形成領域104に位置する基板100に形成され、トランジスタ110のソース及びドレインとなる。絶縁層200は、素子形成領域104上、ゲート電極140上、及び被覆絶縁膜120上に形成されている。コンタクト210は絶縁層200に形成され、拡散領域170に接続している。シリサイド層142は、ゲート電極140上に形成されている。サイドウォール160は、被覆絶縁膜120が形成されている領域においてはゲート電極140より高く形成されている。そしてコンタクト210は、ゲート電極140のうち被覆絶縁膜120が形成されている領域に面している。

(もっと読む)

不揮発性メモリ

【課題】酸化物半導体層を含むトランジスタを有する不揮発性メモリにおいて、保持された情報を容易に消去できる不揮発性メモリを提供する。

【解決手段】不揮発性メモリは、第1のトランジスタ20及び第2のトランジスタ21を有するメモリセルを有し、第1のトランジスタ20は第1のチャネル、第1のゲート電極、第1のソース電極及び第1のドレイン電極を有し、第2のトランジスタ21は酸化物半導体からなる第2のチャネル、第2のゲート電極、第2のソース電極及び第2のドレイン電極を有し、第2のソース電極及び第2のドレイン電極の一方は第1のゲート電極と電気的に接続され、メモリセルへの情報の書き込み及び消去は、第2のソース電極及び第2のドレイン電極の一方と、第1のゲート電極との間のノードの電位を高くすることにより情報が書き込まれ、第2のチャネルに紫外線を照射して、ノードの電位を低くすることにより情報が消去される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】素子の特性や信頼性を向上させることが可能な半導体装置およびその製造方法を提供する。

【解決手段】Hfを含む高誘電率ゲート絶縁膜3上にゲート電極13、14を有する相補型電界効果型トランジスタにおいて、ゲート電極13、14の少なくともゲート絶縁膜3に接する部分は、Ni組成が40%を超えない結晶化したNiシリサイドを主成分とし、pチャネル上のゲート電極14に含まれるNiシリサイドとゲート絶縁膜3との界面にB、Al、Ga、In、Tlの中の少なくともひとつの元素を含み、且つ、nチャネル上のゲート電極13に含まれるNiシリサイドとゲート絶縁膜3との界面にN、P、As、Sb、Biの中の少なくともひとつの元素を含む半導体装置を提供する。

(もっと読む)

寄生容量が低減されたSOIボディ・コンタクト型FETのための方法

【課題】

ボディ・コンタクトを半導体オン・インシュレータ・デバイスに設け、それにより、デバイスに寄生容量の低減をもたらすこと。

【解決手段】

1つの実施形態において、本発明は、絶縁層の上を覆うように配置された半導体層を含む基板であって、半導体層は、半導体ボディと、半導体ボディの外周の周りに存在する分離領域とを含む基板と、基板の半導体層の上を覆うゲート構造体であって、半導体ボディの上面の第1の部分上に存在するゲート構造体と、非シリサイド半導体領域によって半導体ボディの第1の部分から分離される半導体ボディの第2の部分と直接物理的に接触しているシリサイド・ボディ・コンタクトとを含む、半導体デバイスの製造方法を提供する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

配線材料、TFT回路基板、及びターゲット材

【課題】ガラス基板への密着性が高いと共に、Siを含んだ層へのCuの拡散を抑制し、配線とSiを含んだ層とのコンタクト抵抗を低くすることができる配線を提供することができ、また、当該配線材料を用いた回路基板と、当該配線材料用のターゲット材とを提供する。

【解決手段】本発明に係る回路基板用の配線材料は、Cuよりも優先的にSiとの間でシリサイドを形成するシリサイド形成材と、Siの酸化物生成自由エネルギーよりも酸化物生成自由エネルギーが低い少なくとも1種類の添加物とが添加され、残部がCu及び不可避的不純物からなる。

(もっと読む)

1 - 20 / 180

[ Back to top ]