Fターム[5F110EE44]の内容

Fターム[5F110EE44]に分類される特許

1 - 20 / 4,424

半導体装置

層選択レーザーアブレーションパターニング

半導体装置

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた表示装置、スパッタリングターゲット材

液晶表示装置の製造方法

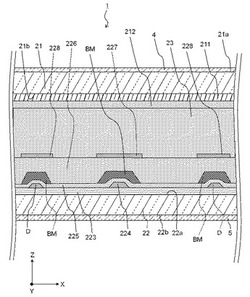

【課題】本発明の液晶表示装置の製造方法によれば、高い表示品位を有する液晶表示装置を製造できる。

【解決手段】液晶表示装置の製造方法は、第2基板22の主面21a上に遮光膜BMを形成する工程と、遮光膜BMを覆うように第1絶縁膜226を形成する工程と、第1絶縁膜226上に透光性の導体層100を形成する工程と、導体層100上にレジストREを形成する工程と、第2基板22の反対主面22b側から、遮光膜BMと重ならない部分のレジストREを露光する工程と、レジストRE上にマスクPMを配置して、レジストREのうち遮光膜BMの形成領域上に位置するレジストREの一部をマスクPM側から露光する工程と、導体層100の一部を露出させる工程

と、導体層100の露出した一部をエッチングし、レジストを除去して、遮光膜BMの形成領

域上に信号電極228および共通電極227を形成する工程とを含むことを特徴とする。

(もっと読む)

電界効果型トランジスタ。

【課題】CNTを含有する半導体層を有する電界効果型トランジスタにおいて、高移動度・高オンオフ比を達成し、且つターンオン電圧・ヒステリシスを低減すること。

【解決手段】表面の少なくとも一部に共役系重合体が付着したカーボンナノチューブを含有する半導体層、ポリマーおよび無機酸化物微粒子を含有するゲート絶縁層、ゲート電極、ソース電極およびドレイン電極を有する電界効果型トランジスタ。

(もっと読む)

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

金属酸化物薄膜形成用塗布液、金属酸化物薄膜、電界効果型トランジスタ、及び電界効果型トランジスタの製造方法

【課題】所望の体積抵抗率を有する金属酸化物薄膜を、簡便かつ大面積に作製でき、更に所望の形状の金属酸化物を形成する精度が高い金属酸化物薄膜形成用塗布液などの提供。

【解決手段】無機インジウム化合物と、無機カルシウム化合物及び無機ストロンチウム化合物の少なくともいずれかと、有機溶媒とを含有する金属酸化物薄膜形成用塗布液である。

(もっと読む)

酸化物半導体装置およびその製造方法

【課題】

短いチャネル長の酸化物半導体装置およびそれを低コストで実現することのできる製造方法を提供する。

【解決手段】

酸化物半導体装置において、チャネルとなる酸化物半導体層CHと、第1方向に、酸化物半導体層CHを介して延伸する第1の電極層(ソース又はドレイン)LEおよび第2の電極層(ドレイン又はソース)UEと、第1方向と交差する第2方向に延伸し、酸化物半導体層CHと基板SUに垂直な方向においてゲート絶縁層GIを介して重なるゲート電極層GEとを有し、酸化物半導体層CHの膜厚がそのチャネル長となる。

(もっと読む)

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

薄膜トランジスタ及び薄膜トランジスタの製造方法

【課題】酸化物をチャネル及びゲート絶縁層に適用した薄膜トランジスタの高性能化、又はそのような薄膜トランジスタの製造プロセスの簡素化と省エネルギー化を実現する。

【解決手段】本発明の1つの薄膜トランジスタ100は、ゲート電極220とチャネル40との間に、ゲート電極20に接する、ビスマス(Bi)とニオブ(Nb)とからなる第1酸化物(不可避不純物を含み得る)の層32と、チャネル40に接する、ランタン(La)とタンタル(Ta)とからなる酸化物、ランタン(La)とジルコニウム(Zr)とからなる酸化物、及びストロンチウム(Sr)とタンタル(Ta)とからなる酸化物の群から選択される1種の第2酸化物(不可避不純物を含み得る)の層34との積層酸化物30を備え、チャネル40が、インジウム(In)と亜鉛(Zn)とからなるチャネル用酸化物(不可避不純物を含み得る)である。

(もっと読む)

半導体装置の作製方法

【課題】電気特性が良好で信頼性の高いトランジスタ及び当該トランジスタを用いた表示

装置を提供する。

【解決手段】チャネル領域に酸化物半導体を用いたボトムゲート型のトランジスタであっ

て、加熱処理により脱水化または脱水素化された酸化物半導体層を活性層に用い、該活性

層は、微結晶化した表層部の第1の領域と、その他の部分の第2の領域で形成されている

。この様な構成をした酸化物半導体層を用いることにより、表層部からの水分の再侵入や

酸素の脱離によるn型化や寄生チャネル発生の抑制、及びソース電極及びドレイン電極と

の接触抵抗を下げることができる。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。

【解決手段】酸化物半導体膜上にチャネル保護膜として機能する絶縁層が設けられたボトムゲート構造のトランジスタを有する半導体装置において、酸化物半導体膜上に接して設けられる絶縁層、及び/または、ソース電極層及びドレイン電極層の形成後に不純物除去処理を行うことで、エッチングガスに含まれる元素が、酸化物半導体膜表面に不純物として残存することを防止する。酸化物半導体膜の表面における不純物濃度は、5×1018atoms/cm3以下、好ましくは1×1018atoms/cm3以下とする。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、シリコンを含む絶縁膜と、絶縁膜上の酸化物半導体膜と、酸化物半導体膜上のシリコンを含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有する構造とし、少なくともゲート電極と重畳する酸化物半導体膜は、絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%より低い領域を有し、当該領域以外の酸化物半導体膜のシリコン濃度は、当該領域より小さくなる構造とする。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置およびその作製方法

【課題】トランジスタ、ダイオード等の半導体用途に好適な材料を提供する。

【解決手段】Inと、M1と、M2と、Znと、を含む酸化物材料であり、M1=13族元素、代表的にはGaであり、M2の元素は、M1の元素よりも含有量が少ない材料を提供する。M2としてはTi、Zr、Hf、Ge、Snなどが挙げられる。M2を含ませることで、酸化物半導体材料における酸素欠損の発生を抑制することができる。酸素欠損がほとんど存在しないトランジスタを実現できれば、半導体装置の信頼性を向上させることができる。

(もっと読む)

1 - 20 / 4,424

[ Back to top ]