Fターム[5F110EE45]の内容

Fターム[5F110EE45]に分類される特許

2,001 - 2,010 / 2,010

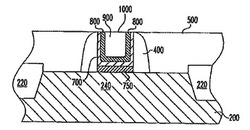

集積回路のトランジスタにおける金属ゲート構造および形成方法(高性能デバイスの金属置換ゲートのための構造および方法)

【課題】 高性能デバイスの金属置換ゲートのための構造および形成方法を提供する。

【解決手段】 まず、半導体基板(240)上に設けたエッチ・ストップ層(250)上に、犠牲ゲート構造(260)を形成する。犠牲ゲート構造(300)の側壁上に、1対のスペーサ(400)を設ける。次いで、犠牲ゲート構造(300)を除去して、開口(600)を形成する。続けて、スペーサ(400)間の開口(600)内に、タングステン等の金属の第1の層(700)、窒化チタン等の拡散バリア層(800)、およびタングステン等の金属の第2の層(900)を含む金属ゲート(1000)を形成する。

(もっと読む)

フィン型電界効果トランジスタを有する半導体装置

n型電界効果トランジスタおよびp型電界効果トランジスタとを含む半導体装置であって、n型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{100}面であり、p型電界効果トランジスタを構成する突起状半導体領域の結晶方位は、その基板と平行な面が実質上{100}面であり、その側面が実質上前記{100}面と直交する{110}面である、という条件を満足する半導体装置とする。 (もっと読む)

窒化シリコン酸化物ゲート誘電体を製造する方法

【課題】 ウェハ内における相対的に均一な厚さ及び窒素濃度を有するSiOxNy層を製造する方法を提供すること。

【解決手段】 基板を準備するステップと、該基板の上面に二酸化シリコン層を形成するステップと、還元雰囲気内でプラズマ窒化を実行し、該二酸化シリコン層を酸窒化シリコン層に変換するステップとを含む、ゲート誘電体層を製造する方法である。このように形成された誘電体層を、MOSFETの製造において用いることができる。

(もっと読む)

半導体デバイスおよびその製造方法

集積回路での使用に適した歪み半導体デバイスおよび歪み半導体デバイスの製造方法。半導体−オン−インシュレータ基板からメサ分離構造が形成される。このメサ分離構造にゲート構造が形成される。このゲート構造は、ゲート絶縁材料に配置されたゲートと、対向する2組の側壁を有する。ゲート構造の対向する第1の組の側壁に隣接するメサ分離構造の一部に、半導体材料が選択的に成長され、ドープが行われる。ドープされた半導体材料がシリサイド化されて、絶縁材料によって保護される。ゲートがシリサイド化され、このシリサイドが、対向する第2の組の側壁を覆っており、チャネル領域に応力を付与する。  (もっと読む)

(もっと読む)

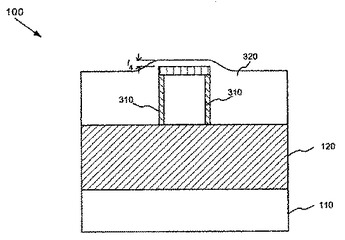

FINFET中のゲート領域のマルチステップ化学機械研磨

チャネル上にたい積されるゲート材料層(320)をプレーナ化するステップを含む、MOSFET型の半導体デバイスを製造する方法である。このプレーナ化は、第1の”荒い”プレーナ化と、その後の”緻密な”プレーナ化を含んだ複数のステッププロセスで実行される。より緻密なプレーナ化で使用されるスラリーは、ゲート材料の低い領域に付着し易い付加材料を含んでいてもよい。  (もっと読む)

(もっと読む)

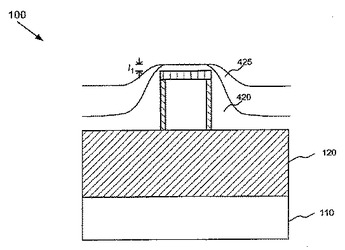

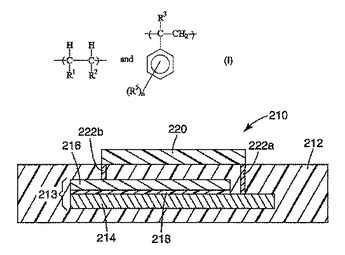

化学機械研磨プレーナ化のためのデュアルシリコンゲート層を有するFINFET

FinFETタイプの半導体デバイスは、フィン構造(210)を含んでいる。この上には、比較的薄いアモルファスシリコン層(420)を形成し、それから非ドープポリシリコン層(425)を形成する。この半導体デバイスは、アモルファスシリコン層(420)がフィン構造の損傷を防ぐ停止層として働く化学機械研磨(CMP)を使用してプレーナ化することができる。  (もっと読む)

(もっと読む)

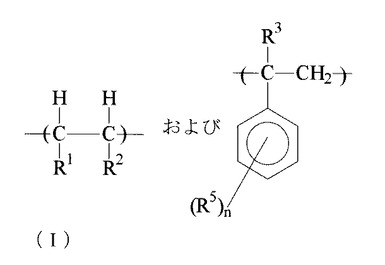

有機ポリマー、ラミネート、およびコンデンサー

コンデンサーなどのラミネートに使用するための有機ポリマー。このポリマーは、式:

【化1】

で示される反復単位を含む。上記式中、各R1は、独立して、H、アリール基、Cl、Br、I、または架橋性基を含む有機基であり;各R2は、独立して、H、アリール基、またはR4であり;各R3は、独立して、Hまたはメチルであり;各R5は、独立して、アルキル基、ハロゲン、またはR4であり;各R4は、独立して、少なくとも1つのCN基を含みかつCN基1つあたり約30〜約200の分子量を有する有機基であり;そしてnは0〜3に等しく;ただし、ポリマー中の少なくとも1つの反復単位は、R4を含む。

(もっと読む)

(もっと読む)

発光装置およびその作製方法

【課題】アクティブマトリクス型の発光装置における光の取り出し効率を向上させる手段を提供する。

【解決手段】アクティブマトリクス型の発光装置において、第1の凹部101a〜第3の凹部101cを有する第1の基板100に金属膜102a〜第3の金属膜102cを形成することや、画素電極145、有機層148、凸部149aの表面を有する陰極149からなる発光素子150を形成することにより、光の損失や隣の画素への光漏れを防ぐことができる。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】 電気特性の優れた多結晶TFTを提供する。

【解決手段】多結晶膜3を堆積させる工程、堆積した多結晶膜のうち所望の位置4のみを残すようにエッチングする工程、残された部分的な多結晶膜の中で所望の結晶方位の結晶粒5だけを、しかも所望の結晶面(ファセット)6を出した状態になるように異方性エッチングする工程、さらに、こうして得られた結晶核の上に膜を堆積し結晶化させる工程を用いる。

(もっと読む)

半導体装置の製造方法

【課題】 優れた特性を有する多結晶シリコン膜を備えた半導体装置を高い歩留まりで製造することが可能な半導体装置の製造方法を提供する。

【解決手段】 石英ガラスや無アルカリガラスなどの基板1上に、非晶質シリコン膜2aを形成する。その非晶質シリコン膜2a上にWシリサイド膜(導電膜)4bを形成する。そして、Wシリサイド膜(導電膜)4bに対し、高周波やYAGレーザービームなどの電磁波を照射することにより、Wシリサイド膜(導電膜)4bを発熱させ、この熱を利用して、非晶質シリコン膜2aを多結晶シリコン膜2に変える。

(もっと読む)

2,001 - 2,010 / 2,010

[ Back to top ]