Fターム[5F110GG02]の内容

Fターム[5F110GG02]に分類される特許

1 - 20 / 7,158

半導体積層体及びその製造方法

印刷可能半導体素子を製造して組み立てるための方法及びデバイス

半導体装置およびその製造方法

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた表示装置、スパッタリングターゲット材

半導体装置およびその製造方法

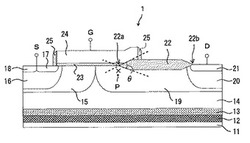

【課題】LOCOS酸化膜端部の直下の電界集中が容易に緩和され、LOCOS酸化膜直下の半導体導電層の良好な耐圧および抵抗を実現することのできる半導体装置を提供する。

【解決手段】半導体装置(1)は、LOCOS酸化膜(22)の半導体基板の表面に対してラテラル方向に終端しているエッジ(22a、22b)の少なくとも一部(22a、22b)が、上面と下面とに15度以上30度以下の角度(θ)で挟まれて終端するプロファイルを有している。

(もっと読む)

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

液晶表示装置の製造方法

【課題】本発明の液晶表示装置の製造方法によれば、高い表示品位を有する液晶表示装置を製造できる。

【解決手段】液晶表示装置の製造方法は、第2基板22の主面21a上に遮光膜BMを形成する工程と、遮光膜BMを覆うように第1絶縁膜226を形成する工程と、第1絶縁膜226上に透光性の導体層100を形成する工程と、導体層100上にレジストREを形成する工程と、第2基板22の反対主面22b側から、遮光膜BMと重ならない部分のレジストREを露光する工程と、レジストRE上にマスクPMを配置して、レジストREのうち遮光膜BMの形成領域上に位置するレジストREの一部をマスクPM側から露光する工程と、導体層100の一部を露出させる工程

と、導体層100の露出した一部をエッチングし、レジストを除去して、遮光膜BMの形成領

域上に信号電極228および共通電極227を形成する工程とを含むことを特徴とする。

(もっと読む)

FinFETを形成する方法およびFinFET構造

【課題】 ゲートの平面性が改善されたFinFETおよび形成方法を提供する。

【解決手段】 不要なフィンを除去する前にフィンのパターン上にゲートが配置される。リソグラフィ技法またはエッチング技法あるいはその両方の組み合わせを使用して、不要なフィンを除去することができる。残りのフィンの全部または一部を併合することができる。

(もっと読む)

配線の形成方法、電子素子、および表示装置

【課題】物理的な版を必要とせず、微細な導電パターンを形成でき、パターン変更に対して柔軟に対応できる配線の形成方法を提供する。

【解決手段】本発明では、基板上に、エネルギー付与によって臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程と、前記濡れ性変化層に選択的にレーザ光を照射して、前記濡れ性変化層の臨界表面張力が高くなるように変化させた高表面エネルギー領域部を前記濡れ性変化層に形成する工程と、前記高表面エネルギー領域部に導電性インクを塗布し、前記高表面エネルギー領域部上に配線を形成する工程と、を有し、前記濡れ性変化層と前記高表面エネルギー領域部とには段差がなく、前記配線は前記高表面エネルギー領域部上に形成されていることを特徴とする配線の形成方法が提供される。

(もっと読む)

半導体装置およびその製造方法

【課題】トンネルFETのオン電流の劣化を抑制しつつ、オフ電流を低減することが可能な半導体装置を提供する。

【解決手段】実施形態によれば、半導体装置は、溝が形成された基板と、前記基板上の前記溝に隣接する位置にゲート絶縁膜を介して形成され、前記溝の反対側に位置する第1側面と、前記溝側に位置する第2側面とを有するゲート電極とを備える。さらに、前記装置は、前記ゲート電極の前記第1側面に形成された第1の側壁絶縁膜と、前記ゲート電極の前記第2側面と前記溝の側面に形成された第2の側壁絶縁膜とを備える。さらに、前記装置は、前記基板内において、前記ゲート電極の前記第1側面に対し前記第1の側壁絶縁膜側に形成された、第1導電型のソース領域と、前記基板内において、前記ゲート電極の前記第2側面と前記溝の側面に対し前記第2の側壁絶縁膜側に形成された、第2導電型のドレイン領域とを備える。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

薄膜トランジスタアレイおよびその製造方法、並びに表示装置

【課題】配線密度を高くしすぎることなく断線を修復することが可能であり、フレキシブル性を持たせる場合に短絡や断線などを抑えることが可能な薄膜トランジスタアレイおよびその製造方法、並びに表示装置を提供する。

【解決手段】第1導電層と、前記第1導電層の少なくとも一部に対向して、前記第1導電層に合わせた平面形状の開口を有する絶縁膜と、前記開口を塞ぐと共に前記開口内で前記第1導電層に接するパッチ部を含む第2導電層とを備えた薄膜トランジスタアレイ。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

半導体装置

【課題】作製工程が簡略化され、容量素子の面積が縮小化された昇圧回路を有する半導体

装置を提供することを課題とする。

【解決手段】直列に接続され、第1の入力端子部から出力端子部へ整流作用を示す複数の

整流素子と、第2の入力端子部に接続され、互いに反転する信号が入力される第1の配線

及び第2の配線と、それぞれ第1の電極、絶縁膜及び第2の電極を有し、昇圧された電位

を保持する複数の容量素子とから構成される昇圧回路を有し、複数の容量素子は、第1の

電極及び第2の電極が導電膜で設けられた容量素子と、少なくとも第2の電極が半導体膜

で設けられた容量素子とを有し、複数の容量素子において少なくとも1段目の容量素子を

第1の電極及び第2の電極が導電膜で設けられた容量素子とする。

(もっと読む)

薄膜トランジスタ回路基板、及びその製造方法

【課題】厚いゲート絶縁層を有する薄膜トランジスタと、薄いゲート絶縁層を有する薄膜トランジスタとを備えた回路基板を提供する。

【解決手段】ポリシリコン半導体層の上下に、ボトムゲート型薄膜トランジスタのゲート絶縁層とトップゲート型薄膜トランジスタのゲート絶縁膜とを各々設け、トップゲート型薄膜トランジスタのゲート絶縁膜の厚さをボトムゲート型薄膜トランジスタのゲート絶縁層の厚さと異ならせる。

(もっと読む)

コンタクトホールの形成方法および電気光学装置の製造方法

【課題】シュリンク技術を利用して、コンタクトホールとして利用できる複数の凹部を1回のレジストマスク工程で異なる深さ寸法に形成することのできるコンタクトホールの形成方法、および電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置の素子基板10上にコンタクトホールを形成するにあたって、まず、第1開口部17aおよび第2開口部17bを備えたレジストマスク17を層間絶縁膜42の表面に形成した後、第1開口部17aおよび第2開口部17bから層間絶縁膜42および絶縁膜49をエッチングする。その後、シュリンク工程において、レジストマスク17を変形させて第2開口部17bを塞ぐ一方、第1開口部17aの開口面積を狭める。次に、第1開口部17aから層間絶縁膜41およびゲート絶縁層2をエッチングする。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。

【解決手段】SOI基板SB上に形成されたマットMT内に複数のMOSFETを有する半導体装置において、BOX膜を貫き支持基板に達するコンタクトプラグCT2を形成することで、マットMTの周囲を、SOI基板SBの主面に沿う第1方向または第1方向に直交する第2方向に延在する複数のコンタクトプラグCT2により囲む。これにより、コンタクトプラグCT2をガードリングとして用い、マットMTの外部に流れる高周波信号に起因してマットMT内にノイズが発生することを防ぐ。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

CMOS集積回路及び増幅回路

【課題】入力トランジスタの構造を櫛形構造にしてゲート抵抗を抑えつつ、NFの増大を防ぐことが可能なCMOS集積回路を提供する。

【解決手段】トランジスタは、ゲート配線から櫛歯状に延びて形成され、信号入力端子からの入力信号が供給されるゲート電極と、ゲート配線に対向した位置に形成されるソース配線から、ゲート電極の櫛歯の間に1つ起きに櫛歯状に延びて形成される、接地端子に接続されたソース電極と、ゲート配線に対向した位置に形成されるドレイン配線から、ゲート電極の櫛歯の間のソース電極が存在しない箇所に櫛歯状に延びて形成される、電源端子に接続されたドレイン電極と、を備え、ゲート電極と、ソース電極またはドレイン電極とは、重なり合う領域が存在しないことを特徴とする、CMOS集積回路が提供される。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

1 - 20 / 7,158

[ Back to top ]