Fターム[5F110GG21]の内容

Fターム[5F110GG21]の下位に属するFターム

断面形状 (1,535)

平面形状 (486)

チャネル半導体層の膜厚が規定 (6,098)

他の構成要素との相対的な大きさが規定 (178)

Fターム[5F110GG21]に分類される特許

1 - 6 / 6

電界効果型トランジスタの製造方法

【課題】電界効果型トランジスタに関する新規な製造方法を提供する。

【解決手段】基板上に、非晶質酸化物層を形成する前に、基板表面にオゾン雰囲気中で紫外線を照射したり、基板表面にプラズマを照射したり、あるいは基板表面を過酸化水素を含有する薬液により洗浄する。または、非晶質酸化物を含み構成される活性層を形成する工程をオゾンガス、窒素酸化物ガス等の少なくともいずれかを含む雰囲気中で行う。または、基板上に、非晶質酸化物層を形成する後に、非晶質酸化物層の成膜温度よりも高い温度で熱処理する工程を含む。

(もっと読む)

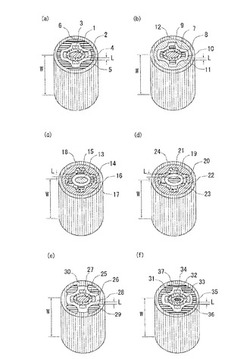

線状素子

【課題】 柔軟性、可撓性があり任意の形状に集積回路を作成できるという特徴を持つ線状MISFETでは、ソース領域とドレイン領域を並列配置する構造が使用されていた。しかし、MISFETの電気特性を決めるチャネル長が円筒形のゲート絶縁領域に沿ったソース領域とドレイン領域の距離できまるため、チャネル長の微細化や再現性向上が困難だった。

【解決手段】 MISFETの構造を、ソース領域とドレイン領域でチャネル領域となる半導体領域を挟む構造とした。半導体領域にゲート絶縁領域を介して制御電圧を加え、ソース領域とドレイン領域間で流れる電流を制御する。チャネル長が、半導体領域の膜厚で決まるため、チャネル長の微細化や再現性向上が可能になった。

(もっと読む)

集積電子回路におけるワイヤー部の形成方法

集積回路にワイヤー部(101、102)を形成する方法は、シード材質の層部分(11、12)の側面上にワイヤー部をエピタキシャル成長する段階を備える。ワイヤー部の断面寸法はシード材質の層部分の厚さ及び成長段階の継続時間に対応する。その後、シード材質の層部分が選択的に除去され、ワイヤー部が回路上に固定的に保持される。その後、回路を加熱することで、ワイヤー部の断面を丸くすることができる。得られたワイヤー部の直径は、約10nmとすることができる。この方法は、ショットチャネル効果がないMOSトランジスタのチャネルを形成するのに用いられ得る。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法、及び、液晶表示装置

【課題】1.5μmのDRによるTFT製造において、電源電圧・しきい値電圧の要求仕様と一般的なTFTに要求されるGI耐圧を同時に達成し、また、3.0μmのDRによるTFT製造においても、GI耐圧を低下させることなく電源電圧等を引き下げる半導体装置及びその製造方法、及び、低消費電力性の良好な液晶表示装置を提供する。

【解決手段】半導体装置は、絶縁性基板と、絶縁性基板上に設けられたベースコート膜と、ベースコート膜上に設けられ、且つ、平坦面を有する半導体層と、半導体層の平坦面上に設けられた酸化シリコン膜と、酸化シリコン膜上に設けられた窒化シリコン膜と、により2層構造に形成されたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、を備える。

(もっと読む)

二重の閾値電圧制御手段を有する低閾値電圧の半導体デバイス

【課題】 Si又はGeの高い含有量を有する高k誘電体を絶縁中間層と組み合わせることによって、及び/又は、チャネル工学処理によって、閾値電圧及びフラットバンド電圧のシフトを低減させること。

【解決手段】 SiO2より大きい誘電率、及び、50%を超えるGe又はSi含有量を有する誘電体材料と、材料スタック工学処理によって閾値電圧/フラットバンド電圧を調整するための少なくとも1つの他の手段とを含む、半導体構造体、特にpFETが提供される。本発明において考慮される他の手段は、例えば、電荷を固定するために誘電体の上に絶縁中間層を用いること、及び/又は、工学処理されたチャンネル領域を形成することを含む。本発明はまた、このようなCMOS構造体を製造する方法にも関する。

(もっと読む)

微小半導体構造およびその製造方法

【課題】優れた半導体特性を備えた微小半導体構造を簡便に製造する方法を提供する。

【解決手段】単結晶半導体からなる微小半導体構造の製造方法であって、半導体成長の触媒作用を有する元素を含む金属体102および絶縁膜103を含む積層構造を支持体101上に形成する工程(a)と、絶縁膜103と反応する元素を含むガス雰囲気に絶縁膜103表面を曝すことにより、元素と絶縁膜とを反応させて絶縁膜の一部を除去し、金属体の表面を露出する開口部105を絶縁膜103に形成する工程(b)と、単結晶半導体を構成する元素を含むガス雰囲気に露出した金属表面を曝すことにより、開口部105内に単結晶半導体からなる微小構造体110を形成する工程(c)とを包含する微小半導体構造の製造方法。

(もっと読む)

1 - 6 / 6

[ Back to top ]