Fターム[5F110GG24]の内容

Fターム[5F110GG24]の下位に属するFターム

1000Å(0.1μm)以下 (4,599)

Fターム[5F110GG24]に分類される特許

1 - 20 / 1,499

半導体積層体及びその製造方法

酸化物半導体装置およびその製造方法

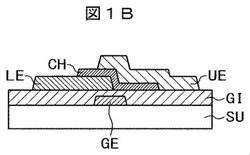

【課題】

短いチャネル長の酸化物半導体装置およびそれを低コストで実現することのできる製造方法を提供する。

【解決手段】

酸化物半導体装置において、チャネルとなる酸化物半導体層CHと、第1方向に、酸化物半導体層CHを介して延伸する第1の電極層(ソース又はドレイン)LEおよび第2の電極層(ドレイン又はソース)UEと、第1方向と交差する第2方向に延伸し、酸化物半導体層CHと基板SUに垂直な方向においてゲート絶縁層GIを介して重なるゲート電極層GEとを有し、酸化物半導体層CHの膜厚がそのチャネル長となる。

(もっと読む)

金属酸化物薄膜形成用塗布液、金属酸化物薄膜、電界効果型トランジスタ、及び電界効果型トランジスタの製造方法

【課題】所望の体積抵抗率を有する金属酸化物薄膜を、簡便かつ大面積に作製でき、更に所望の形状の金属酸化物を形成する精度が高い金属酸化物薄膜形成用塗布液などの提供。

【解決手段】無機インジウム化合物と、無機カルシウム化合物及び無機ストロンチウム化合物の少なくともいずれかと、有機溶媒とを含有する金属酸化物薄膜形成用塗布液である。

(もっと読む)

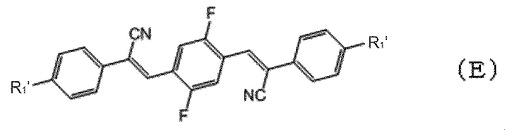

新規化合物および該化合物を含む有機半導体材料

【課題】キャリア移動度と安定性が高く、有機半導体材料として好適な新規化合物を提供する。

【解決手段】

下記一般式(E)で表される化合物。

【化1】

(但し、R1'は、炭素数1〜3のフッ素置換アルキル基である。)

当該化合物はキャリア移動度と安定性が高く、容易な製造プロセスで成膜が可能であるため、有機半導体材料として好適である。特に有機薄膜トランジスタ用の有機半導体層として好適に使用することができる。

(もっと読む)

半導体積層体、半導体デバイス、及びそれらの製造方法

【課題】本発明では、高価かつエネルギー多消費型の大掛かりな装置を必要とせずに、連続性が高い半導体シリコン膜を有する半導体積層体を製造する方法を提供する。また、本発明では、連続性が高い半導体シリコン膜を有する半導体積層体を提供する。

【解決手段】半導体積層体を製造する本発明の方法は、基材の表面上にシリコン粒子分散体膜を形成する工程、シリコン粒子分散体膜を乾燥して、未焼結シリコン膜120を形成する工程、及び未焼結シリコン膜に光200を照射して、半導体シリコン膜130aを形成する工程を含み、かつ基材の表面100aに対する溶融シリコンの接触角が70度以下である。本発明の半導体積層体は、この半導体シリコン膜が、互いに焼結されている複数のシリコン粒子から作られており、かつ基材の表面に対する溶融シリコンの接触角が70度以下である。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

化合物半導体

【課題】高電圧駆動素子の為にSiCやGaNの基板の簡素化が重要な課題となっている。Si基板上のシリコン酸化膜の上に単結晶のSiC膜を形成し、トレンチによる絶縁物分離構造とし、その中に結晶欠陥が多くてもその影響を避ける新構造の素子の発明である。

【解決手段】SiC膜に形成したMOSFETなどの半導体素子を構成しているPN接合面において基板面と並行となる面にあるPN接合に印加される電界が、SiC膜が形成されているシリコン酸化膜や基板となるSi層により緩和されて、さらには基板電位をドレイン電圧とは逆方向の電位とすることにより大きく電界緩和されて、SiC膜に発生している基板と垂直方向の結晶欠陥の結晶欠陥降伏電圧以下とすることを特徴とする素子構造を持った半導体装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

液晶表示装置

【課題】画質の低下を防ぎつつ、消費電力の低減を実現することができる、液晶表示装置

の駆動方法を提案する。

【解決手段】液晶素子と、当該液晶素子への画像信号の供給を制御するトランジスタとを

画素に有する。上記トランジスタは、チャネル形成領域に、シリコン半導体よりもバンド

ギャップが広く、真性キャリア密度がシリコンよりも低い半導体を含み、オフ電流の極め

て小さい。そして、画素を反転駆動させる際に、画素電極を間に挟んで配置されている一

対の信号線に、互いに逆の極性を有する画像信号を入力する。上記構成により、液晶素子

に容量素子を接続しなくても、表示される画質が低下するのを防ぐ。

(もっと読む)

半導体装置の作製方法

【課題】本発明の一態様は、スパッタ法でトランジスタ、ダイオード等の半導体用途に好

適な材料を提供することを課題の一とする。

【解決手段】下地部材上に、第1の酸化物部材を形成し、第1の加熱処理を行って表面か

ら内部に向かって結晶成長し、下地部材に少なくとも一部接する第1の酸化物結晶部材を

形成し、第1の酸化物結晶部材上に第2の酸化物部材を形成し、第2の加熱処理を行って

第1の酸化物結晶部材を種として結晶成長させて第2の酸化物結晶部材を設ける積層酸化

物材料の作製方法である。

(もっと読む)

生体情報評価システム

【課題】顕微鏡で観察するのと同時に生体関連物質の信号情報を透明バイオセンサで取得する場合に、その信号情報を正確に取得することができる生体情報評価システムを提供する。

【解決手段】透明基材とその透明基材上に設けられた薄膜トランジスタ素子部及び透明な生体関連物質感応部とを有し、その薄膜トランジスタ素子部が酸化物半導体膜を有する透明バイオセンサ10と、透明バイオセンサ10が有する生体関連物質感応部に載置される生体関連物質から信号情報を取得する電気信号測定装置101と、透明バイオセンサ10をステージ53上にセットし、透明バイオセンサ10に光源光62,74を照射して生体関連物質感応部に載置される生体関連物質を観察する顕微鏡90とを少なくとも備え、透明バイオセンサ10と光源光62,74との間に紫外線カットフィルタ51を設けた生体情報評価システム50により上記課題を解決した。

(もっと読む)

半導体装置

【課題】安定した電気特性を有する薄膜トランジスタを有する電位保持機能の高い固体撮

像素子を提供する。

【解決手段】酸化物半導体層を用いて薄膜トランジスタのオフ電流を1×10−13A以

下とし、該薄膜トランジスタを固体撮像素子のリセットトランジスタ及び転送トランジス

タの両方に用いることで信号電荷蓄積部の電位が一定に保たれ、ダイナミックレンジを向

上させることができる。また、周辺回路に相補型金属酸化物半導体素子が作製可能なシリ

コン半導体を用いることで高速かつ低消費電力の半導体装置を作製することができる。

(もっと読む)

しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法

【課題】しきい電圧の変動を減らした高電子移動度トランジスタ及びその製造方法を提供する。

【解決手段】化合物半導体を含む基板上に形成され、二次元電子ガスチャネルとデプリーション領域とを備えるチャネル層と、二次元電子ガスチャネルに対応するように、チャネル層上に形成された第1チャネル供給層と、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に形成されたデプリーション層と、第1チャネル供給層上に形成され、デプリーション領域を挟んで対向するソース及びドレイン電極と、デプリーション層上に形成されたゲート電極と、を備え、第1チャネル供給層より分極率が小さい第2チャネル供給層を、チャネル層のデプリーション領域及び第1チャネル供給層の一部の領域上に備え、デプリーション層が第2チャネル供給層上に備えられる、高電子移動度トランジスタである。

(もっと読む)

横型素子を有する半導体装置

【課題】耐圧バラツキを抑制し、歩留りを向上させることが可能となる横型素子を有する半導体装置を提供する。

【解決手段】横型FWDなどの横型素子に備えられるSRFP21について、の不純物濃度を1×1018cm-3以上となるようにする。このように、横型FWD7などに備えられるSRFP21について、の不純物濃度を1×1018cm-3以上とすることにより、耐圧バラツキを抑制することが可能となり、的確に目標とする耐圧を得ることができる製品とすることが可能になる。したがって、製品の歩留りを向上させることが可能となる。

(もっと読む)

表示装置およびその製造方法、並びに電子機器

【課題】互いに電気的に接続された薄膜トランジスタの第2電極と配線層との間の電食の発生を防止して、安定した電気特性を得ることできる表示装置およびその製造方法、並びに電子機器を提供する。

【解決手段】薄膜トランジスタおよび配線層を備え、前記薄膜トランジスタは、制御電極

と、前記制御電極と対向する半導体層と、前記半導体層に電気的に接続され、光透過性材

料からなる第1電極と、前記光透過性材料よりも低抵抗の金属膜を含むと共に、前記半導

体層および前記配線層にそれぞれ電気的に接続された第2電極とを備え、前記金属膜の構

成材料と前記配線層の少なくとも一部を構成する導電材料とのイオン化傾向の差は、前記

光透過性材料と前記導電材料とのイオン化傾向の差よりも小さい表示装置。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

半導体装置の製造方法

【課題】結晶性の優れた炭化シリコン膜を形成することができる炭化シリコンからなる半導体装置の製造方法を提供する。

【解決手段】基板1上に、絶縁膜2を介してシリコン膜3が形成された半導体基板を用意し、炭化シリコン膜6形成予定領域を選択的に被覆するマスク膜5を形成する。このマスク膜5で被覆されない領域のシリコン膜3を酸化し、酸化シリコン膜4を形成する。マスク膜5を除去し、シリコン膜3を露出させ、露出したシリコン膜3を炭化し、炭化シリコン膜6を形成する。その後、炭化シリコン膜6上に炭化シリコンのエピタキシャル成長膜8を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】長期にわたって安定した動作が可能な化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された電子走行層3及び電子供給層5と、電子供給層5上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11daと、電子供給層5とゲート電極11gとの間に形成された第1のp型半導体層7aと、ソース電極11sと電子供給層5との間に形成されたp型半導体層7と、が設けられている。第2のp型半導体層7上のソース電極11sには、第1の金属膜11saと、第1の金属膜11saにゲート電極11g側で接し、第1の金属膜11saよりも抵抗が大きい第2の金属膜11sbと、が設けられている。

(もっと読む)

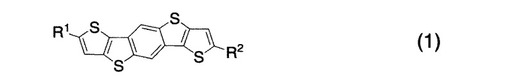

ジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタ

【課題】溶媒への溶解性に優れ、高キャリア移動度が期待できる新規なジチエノベンゾジチオフェン誘導体組成物及びこれを用いた有機薄膜トランジスタを提供する。

【解決手段】下記一般式(1)で示されるジチエノベンゾジチオフェン誘導体99〜80重量%及び特定式で示されるジチエノベンゾジチオフェン誘導体1〜20重量%からなることを特徴とするジチエノベンゾジチオフェン誘導体組成物。

(ここで、置換基R1及びR2は、同一又は異なって、n−ペンチル基、n−ヘキシル基、n−ヘプチル基及びn−オクチル基からなる群より選択される置換基を示す。)

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

1 - 20 / 1,499

[ Back to top ]