Fターム[5F110GG30]の内容

Fターム[5F110GG30]に分類される特許

1 - 20 / 331

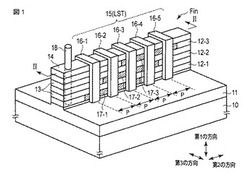

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

FinFETを形成する方法およびFinFET構造

【課題】 ゲートの平面性が改善されたFinFETおよび形成方法を提供する。

【解決手段】 不要なフィンを除去する前にフィンのパターン上にゲートが配置される。リソグラフィ技法またはエッチング技法あるいはその両方の組み合わせを使用して、不要なフィンを除去することができる。残りのフィンの全部または一部を併合することができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細化を実現し、トランジスタとして十分に機能できる電気的特性を付与された半導体装置を提供する。

【解決手段】半導体層、ゲート絶縁膜、及びゲート電極層が順に積層されたトランジスタを有する半導体装置において、該半導体層としてインジウム、ガリウム、亜鉛、及び酸素の4元素を少なくとも含み、該4元素の組成を原子百分率で表したとき、インジウムの割合が、ガリウムの割合及び亜鉛の割合の2倍以上である酸化物半導体膜を用いる。該半導体装置において、酸化物半導体膜は作製工程において酸素が導入され、酸素を多く(過剰に)含む膜であり、トランジスタを覆う酸化アルミニウム膜を含む絶縁層が設けられる。

(もっと読む)

パワー絶縁ゲート型電界効果トランジスタ

【課題】酸化物半導体を用いたパワー絶縁ゲート型電界効果トランジスタ(パワーMISFET)を提供する。

【解決手段】半導体層103を挟んでゲート電極105とドレイン電極102を形成し、ゲート電極105の側面に半導体層109を形成し、ゲート電極105の頂上部と重なる部分で、半導体層109とソース電極112が接する構造を有する。このようなパワーMISFETのドレイン電極とソース電極の間に500V以上の電源と負荷を直列に接続し、ゲート電極105に制御用の信号を入力して使用する。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体装置の製造方法及びプラズマドーピング装置

【課題】フィン型半導体領域の側面に不純物を導入して低抵抗の不純物領域を形成できるようにし、それによって、所望の特性を持つフィン型半導体装置を実現する。

【解決手段】基板11上にフィン型半導体領域13を形成した後、不純物含有ガスと酸素含有ガスとを用いて、フィン型半導体領域13に対してプラズマドーピングを行うことによって、フィン型半導体領域13の少なくとも側部に不純物導入領域27Bを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SOI基板を用いることなく、絶縁層上にフィン型半導体を形成する。

【解決手段】半導体基板1上に支柱型半導体4を形成し、支柱型半導体4の下部を埋め込む絶縁層5を半導体基板1上に形成し、支柱型半導体4の上部の側面に接合されたフィン型半導体6を絶縁層5上に形成し、フィン型半導体6を絶縁層5上に残したまま支柱型半導体4を除去する。

(もっと読む)

半導体装置

【課題】チャネル形成領域の空乏化領域を増やし、電流駆動能力の高い半導体装置を提供する。

【解決手段】島状の半導体領域308と、前記島状の半導体領域308の側面及び上面を覆って設けられたゲート絶縁膜310と、前記ゲート絶縁膜310を介して前記島状の半導体領域308の前記側面及び前記上面を覆って設けられたゲート電極とを有し、前記島状の半導体領域308の前記側面及び前記上面はチャネル形成領域として機能する半導体装置である。

(もっと読む)

半導体装置

【課題】短チャネル効果を抑制させつつ微細化を行い、低消費電力化した半導体装置を提供する。

【解決手段】溝部および該溝部を挟んで形成された一対の低抵抗領域を有する半導体基板と、半導体基板上の第1のゲート絶縁膜と、第1のゲート絶縁膜を介し、溝部と重畳するゲート電極と、ゲート電極を覆って設けられた第2のゲート絶縁膜と、第2のゲート絶縁膜上の、溝部を挟んで設けられた一対の電極と、一対の電極と接する半導体膜と、を有し、一対の低抵抗領域の一方と、一対の電極の一方が電気的に接続されている積層されたトランジスタを形成し、一方はn型半導体からなるトランジスタであり、他方はp型半導体からなるトランジスタにより形成させることによって、相補型MOS回路を形成する。

(もっと読む)

半導体装置、および、その製造方法

【課題】製造効率の向上、コストダウン、信頼性の向上を実現する。

【解決手段】第1導電型の第1電界効果トランジスタを第1基板に設ける。そして、第1導電型と異なる第2導電型の第2電界効果トランジスタを第2基板に設ける。そして、第1基板と第2基板とのそれぞれを対面させて貼り合わせる。そして、第1電界効果トランジスタと第2電界効果トランジスタとの間を電気的に接続させる。

(もっと読む)

電子デバイス及びその製造方法

【課題】転写プロセスを用いずに、所期のグラフェンを制御性良く容易且つ確実に安定形成し、信頼性の高い高性能の微細な電子デバイスを実現する。

【解決手段】基板1上に絶縁層2を形成し、絶縁層2に空隙2Aを形成し、空隙2Aに触媒材料4を充填し、絶縁層2における触媒材料4の露出面4aにグラフェン5を形成し、絶縁層2上でグラフェン5の両端部に接続するように一対の電極5,6を形成し、グラフェン5を一部除去してグラフェンリボン8を形成し、グラフェンリボン8の除去された部位である間隙2A1,2A2を通じて触媒材料4を除去する。

(もっと読む)

ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法

【課題】ワイヤチャンネルを有する電界効果トランジスタ及びその製造方法を提供する。

【解決手段】半導体基板100と、半導体基板100上に形成されたソース/ドレイン

領域142と、ソース/ドレイン領域142と電気的に連結され、2列及び少なくとも2

行で配列された複数個のワイヤチャンネル112e、114eと、複数個のワイヤチャン

ネル112e、114eをそれぞれ取り囲むゲート絶縁膜142aと、それぞれの複数個

のワイヤチャンネル112e、114e及びゲート絶縁膜142aを取り囲むゲート電極

と、を備える。

(もっと読む)

半導体装置

【課題】長期に亘って信頼性の高い横型MISFETを有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置1は、半導体基板11上に形成された半導体層13と、半導体層13に溝状に形成され、その内壁が絶縁膜31で被覆され、絶縁膜31の内部にゲート電極32が埋設されたトレンチ溝30と、半導体層13上に、トレンチ溝30と少なくとも一部が対向配置する位置に形成されたゲート配線51と、ゲート配線51を挟むように半導体層13上に形成されたソース電極52、及びドレイン電極53とを具備する。半導体層13におけるオン動作時の電流経路は、ソース電極52とドレイン電極53の間の半導体層13の表面領域を実質的に経由せず、上記トレンチ溝30の側面近傍を経由する。

(もっと読む)

薄膜トランジスタアレイ、表示装置、およびそれらの製造方法

【課題】本発明は、開口率を大きくする必要がなく、印刷に適し、複数画素を用いずに面積階調できる薄膜トランジスタアレイ、表示装置、および薄膜トランジスタアレイの製造方法を提供する。

【解決手段】画素の有効領域の幅をA、画素の有効領域のネガパターンの幅をBとしたとき、幅Bが幅Aよりも大きな薄膜トランジスタとする。あるいは、対向電極と画素電極の距離をCとしたとき、距離Cが幅Bの4分の1以上B以下である表示装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】高性能でかつばらつきの少ないナノワイヤトランジスタを備えた半導体装置およびその製造方法を提供する。

【解決手段】半導体基板上に第1絶縁膜を形成する工程と、第1絶縁膜上に設けられ、第1領域と第1領域よりも幅の広い第2および第3領域とを有しこれらの第2および第3領域の少なくとも一方が第1領域に接続するように構成された第1半導体層と、第1半導体層の上面に設けられるマスクと、を形成する工程と、マスクを用いて、前記第1半導体層の第1領域の側面にイオン注入を行う第1イオン注入を行う工程と、イオン注入を行った後に、第1熱処理を行う工程と、マスクを除去した後、第1半導体層の前記第1領域の少なくとも側面にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、ゲート電極の、第2および第3領域側の側面に絶縁体のゲート側壁を形成する工程と、少なくとも第1半導体層の第2および第3領域に第2イオン注入を行う工程と、とを備えている。

(もっと読む)

電界効果トランジスタとその製造方法

【課題】電界効果トランジスタとその製造方法において、電界効果トランジスタの耐圧を高めつつそのオン抵抗を低減すること。

【解決手段】基板1と、基板1の上に形成され、複数の第1の半導体層3と複数の層間絶縁層4とが交互に積層された積層体10と、積層体10の側面10aに形成されると共に、該側面10aにおいて複数の第1の半導体層3の各々に接続された第2の半導体層12と、第2の半導体層12の上に形成されたゲート絶縁層17と、ゲート絶縁層17の上に形成され、ゲート絶縁層17を介して側面10aに対向するゲート電極19と、第2の半導体層12に電気的に接続されたソース電極14と、複数の第1の半導体層3の各々に電気的に接続されたドレイン電極15とを有する電界効果トランジスタによる。

(もっと読む)

一時記憶回路、記憶装置、信号処理回路

【課題】トランジスタの数を少なくした構成の記憶素子を用いた一時記憶回路を提供する。

【解決手段】一時記憶回路は複数の記憶素子を有し、複数の記憶素子それぞれは、第1のトランジスタと、第2のトランジスタとを有し、第1のトランジスタはチャネルが酸化物半導体層に形成され、ゲートに入力される制御信号によってオン状態を選択された第1のトランジスタを介して、データに対応する信号電位を第2のトランジスタのゲートに入力し、ゲートに入力される制御信号によって第1のトランジスタをオフ状態とすることによって、第2のトランジスタのゲートに当該信号電位を保持し、第2のトランジスタのソース及びドレインの一方を第1の電位としたとき、第2のトランジスタのソースとドレイン間の状態を検出することによってデータを読み出す。

(もっと読む)

半導体装置及びその製造方法

【課題】電子及び正孔の移動度を向上させたSOI構造のCMOSの提供

【解決手段】Si基板1上にシリコン窒化膜2及びシリコン酸化膜3を介して、歪みSi層6を挟み、左右にSiGe層5を有する構造からなる第1のエピタキシャル半導体層及び歪みGe層8を挟み、左右にSiGe層7を有する構造からなる第2のエピタキシャル半導体層が島状に絶縁分離されて設けられ、歪みSi層6には概略チャネル領域が形成され、SiGe層5には概略高濃度及び低濃度のソースドレイン領域(10、11、12,13)が形成された包囲型ゲート電極構造のNチャネルのMISFETと、歪みGe層8には概略チャネル領域が形成され、SiGe層7には概略高濃度のソースドレイン領域(14、15)が形成された包囲型ゲート電極構造のPチャネルのMISFETとから構成したCMOS。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

1 - 20 / 331

[ Back to top ]