Fターム[5F110GG31]の内容

Fターム[5F110GG31]の下位に属するFターム

Fターム[5F110GG31]に分類される特許

1 - 15 / 15

半導体装置

【課題】カラーフィルタに含まれる不純物による汚染の問題を解決する。

【解決手段】薄膜トランジスタと、薄膜トランジスタに電気的に接続されるソース電極及

びドレイン電極と、薄膜トランジスタ、ソース電極及びドレイン電極上の第1の絶縁膜と

、第1の絶縁膜上のカラーフィルタと、カラーフィルタ上の第2の絶縁膜と、第2の絶縁

膜上の画素電極とを有し、第1の絶縁膜は窒化シリコンを有し、カラーフィルタは第1の

開口部を有し、第2の絶縁膜は第2の開口部を有し、第2の開口部は第1の開口部の内側

に設けられ、画素電極は、第1の開口部及び第2の開口部を介してソース電極及びドレイ

ン電極の一方に電気的に接続され、カラーフィルタは、画素電極、ソース電極及びドレイ

ン電極に接触しない。

(もっと読む)

誘電体分離型半導体装置

【課題】高耐圧かつ、電流駆動能力が高く、かつ電流集中による素子破壊の起こりにくい誘電体分離型半導体装置を提供する。

【解決手段】半導体支持基板の上に、絶縁された第一導電型の半導体領域とを有する誘電分離基板に形成した誘電体分離型半導体装置において、第一導電型の半導体領域と絶縁分離領域の間と、前記第1導電型の半導体領域の基板表面側と、に形成されたドレイン領域と、第一導電型のソースと第二導電型の半導体領域のチャネルからなる複数個の単位ソース領域と、第一導電型の半導体領域の基板表面側に形成されたドレイン領域と前記複数個の単位ソース領域の間を制御する複数個のゲート電極とを、備え、隣接する前記単位ソース領域間に絶縁分離領域が、基板底面側から基板表面側に向けて突き出した形状とされ、この絶縁分離領域上の素子表面領域が前記第一導電型の半導体領域より抵抗値が高い。

(もっと読む)

有機半導体膜の形成方法

【課題】塗布性の低いゲート絶縁膜表面に低分子有機半導体材料をハジキを発生することなく塗布することが可能となり、形成された有機半導体膜はバラツキの少ない、優れた移動度を得ること。

【解決手段】基板上に低分子有機半導体材料を含む溶液を供給し、乾燥させることにより薄膜を形成させる有機半導体膜の形成方法において、基板上に形成された有機半導体ウエット膜に不溶性の微小構造物を含むことを特徴とする有機半導体膜の形成方法。

(もっと読む)

半導体装置

【課題】ドリフト領域に設けられたトレンチ内に抵抗性フィールドプレートを有し、トレンチ底部近傍の電界強度がトレンチ開口部近傍の電界強度に近く、高耐圧で駆動が可能であり、オン電圧の増加を抑制することができる安価な半導体装置を提供すること。

【解決手段】nドリフト領域3の表面層のpボディ領域4およびnバッファ領域7に挟まれた部分に設けられたトレンチ11に、酸化膜12を介して、抵抗性薄膜13が設けられている。この抵抗性薄膜13に、コレクタ(ドレイン)電極17と、ゲート電極16もしくはエミッタ(ソース)電極15と、を接続させることで抵抗性フィールドプレートとする。これによって、トレンチ11の開口部近傍の電界強度と、トレンチ11の底部近傍の電界強度と、がほぼ同等となるため、nドリフト領域3の電流経路が短くなり、デバイスを高耐圧で駆動する場合にも、オン電圧の増加を抑制することができる。

(もっと読む)

イメージセンサ及びその作製方法

【課題】受光部での隣接画素への漏れ込みを防止して、高開口率、高密度の受光画素を備えたイメージセンサおよびその作製方法を提供することを目的とする。

【解決手段】光電変換層に溝部を形成し、この溝部に絶縁性の光吸収物を埋め込む。光吸収物の下部の光電変換層(溝部の下に残存した光電変換層)は光吸収物によって遮光されるため、フォトキャリアが生じないことを利用する(段落0013)。なお、光吸収物が確実に溝部に埋め込まれる深さである必要があるので、溝部は光電変換層を貫通せず、溝部の下に光電変換層を残存させている(段落0070)。

(もっと読む)

シミュレーション装置、シミュレーション方法、及び半導体装置の製造方法

【課題】欠陥準位を取り込んだ物理モデルに基づき、比較的短時間で高精度な回路解析を行うことができるシミュレーション装置を提供する。

【解決手段】入力装置11、記憶装置12、演算装置16、制御装置15及び出力装置17を備えるシミュレーション装置が開示されている。入力装置から入力されたTFTにおけるゲート電極端に対応する多結晶シリコン薄膜のゲート電極側表面のソース領域端の第1電位φS0、多結晶シリコン薄膜におけるゲート電極が形成された表面に対向する裏面側のソース領域端の第2電位φb0、TFTにおけるゲート電極端に対応する多結晶シリコン薄膜のゲート電極側表面のドレイン領域端の第3電位φSL、及び多結晶シリコン薄膜におけるゲート電極が形成された表面に対向する裏面側の前記ドレイン領域端の第4電位φbLに基づいて演算を行ってドレイン電流Idsを算出し、欠陥準位を含めてモデル化する。

(もっと読む)

NAND型不揮発性メモリのデータ消去方法

【課題】NAND型不揮発性メモリの消去動作として、PウェルやNウェルなどの基板端子を用いないで、不揮発性メモリ素子における電荷蓄積部に注入された電荷を放出する、すなわちNAND型不揮発性メモリのデータの消去動作する方法を提供することを課題とする。

【解決手段】NAND型不揮発性メモリにおけるデータの消去方法において、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出について、ビット線、ソース線、及び制御ゲートに電位を印加することにより行う。そして、不揮発性メモリ素子における電荷蓄積層に格納された電荷の放出を、電荷を放出する不揮発性メモリ素子のソース端子、ドレイン端子、及び制御ゲートに電位を印加することにより行う。

(もっと読む)

半導体装置

【課題】 共通電極と2つのドレイン領域との電気的な接続が不十分になることを抑制する。

【解決手段】本発明の相補型の半導体装置(100)は、第1導電型のトランジスタと第1導電型とは異なる第2導電型のトランジスタとを備える。半導体層(410)の主面の法線方向から半導体層(410)を見たときに、第1導電型のトランジスタの第1ドレイン領域(230)は、第2ドレイン領域(330)側に凸部(232)を有し、第2導電型のトランジスタの第2ドレイン領域(330)は、第1ドレイン領域(230)側に凹部(332)を有している。共通電極(400)は、前記第1ドレイン領域(230)の前記凸部(232)の少なくとも一部、および、前記第2ドレイン領域(330)の前記凹部(332)の少なくとも一部のそれぞれと重なるように配置されている。

(もっと読む)

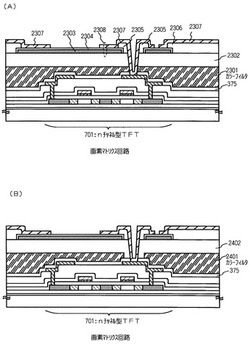

アクティブマトリクス基板

【課題】単位時間当たりの電流供給量を増大させ、能力の向上を図かったTFTにより構成される周辺回路部及び画素部よりなるアクティブマトリクス基板を提供し、これにより電子機器の小型化、及び省電力化を実現する。

【解決手段】 表示画素がマトリクス状に配置された画素部と、該画素部を駆動するための回路を有する周辺回路部が、基板上に配置されたアクティブマトリクス基板であって、該周辺回路部は、nチャネル型TFT(薄膜トランジスタ)群及び/又はpチャネル型TFT群を備え、前記nチャネル型TFT群及びpチャネル型TFT群の少なくともいずれか一方は、2以上の閾値が異なる同型のTFTから構成することにより実現を図る。

(もっと読む)

表示装置

【課題】透過型のアクティブマトリクス型液晶表示装置において、ブラックマトリクスと画素電極のコンタクト部とが接触してしまう問題を回避する。

【解決手段】ブラックマトリクスを構成する遮光材料を顔料を含有させ、遮光性を持たせた樹脂材料114でもって構成する。そしてこの樹脂材料に直接開口119を形成し、そこで画素電極120と薄膜トランジスタとのコンタクトを行わせる。こうすることにより、ブラックマトリクスを金属材料でもって構成していた場合における画素電極とブラックマトリクスとの接触の問題を解決することができる。

(もっと読む)

表示装置

【課題】遮光膜の電位の変動に起因してトランジスタの動作が不安定になるのを抑制し、かつ、動作不良が発生するのを抑制することが可能な表示装置を提供する。

【解決手段】この表示装置は、nチャネルトランジスタ8を含む画素部6に設けられるとともに、nチャネルトランジスタ8の下方に配置され、1/2(Vdd+Vbb)の電位が与えられる表示部遮光膜13の画素部遮光領域13aと、nチャネルトランジスタを含むシフトレジスタ回路25および35、サンプリングトランジスタ26、バッファ27、DAコンバータ28およびクロック発生回路29にそれぞれ設けられ、1/2(Vdd+Vss)の電位が与えられるシフトレジスタ回路遮光膜30および37、サンプリングトランジスタ遮光膜31、バッファ遮光膜32、DAコンバータ遮光膜33およびクロック発生回路遮光膜34とを備えている。

(もっと読む)

電界効果型トランジスタ

【課題】 ソース、ドレイン、ゲート電極、有機半導体層などを形成する場合に印刷法、インクジェット法などの簡便な方法によって形成しても、ON/OFF比が良好な素子を実現する。また、短チャネルを実現することにより、動作電流が大きく、且つ素子間の特性のばらつきの少ない有機材料を用いた電界効果トランジスタを安価に提供する。

【解決手段】 少なくとも支持基板、ソース電極、ドレイン電極、活性層、絶縁層、ゲート電極からなり、ソース電極およびドレイン電極が同一平面内に形成され、前記ソース電極、ドレイン電極に隣接して隔壁が設けられてなる間の幅が少なくとも前記活性層にて電気的に接続されてなる活性層として有機物を用いた電界効果型トランジスタ素子において、前記の隔壁の高さがソース−ドレイン間とその他の箇所において、高さが異なる。

(もっと読む)

横型MOSトランジスタ

【課題】 配線抵抗及び配線容量を低減するとともに、チップ面積を削減する。

【解決手段】 SOI基板30は、シリコン基板31の上にシリコン酸化膜32が形成され、このシリコン酸化膜32の上にN−型シリコン層33が形成されて構成される。ドレイン領域35は、シリコン層33の表面からシリコン酸化膜32まで到達して形成される。ドレイン電極42は、SOI基板30の裏面に電気的接触して形成される。導電体プラグ41は、ドレイン領域35の表面からドレイン領域35およびシリコン酸化膜32を貫通してシリコン基板31中に延在して、ドレイン領域35およびシリコン基板31に電気的接触して形成される。

(もっと読む)

透過型光変調素子の製造方法

【課題】 設計の自由度の大きい、構造が簡単で、コスト安で、制御が簡単で、波長依存性がない電気機械式光シャッター素子を、高精度・高品質・低価格で製造できる製造方法を提供する。

【解決手段】 透過型光変調素子の製造方法において、まず、Si(シリコン)基板上に駆動回路を形成し、次に、その上に透過型光変調部の成膜をしてパターニングを行い、その後、前記駆動回路と前記透過型光変調部を前記Si基板から透明基板上に転写するようにした。

(もっと読む)

半導体装置およびその作製方法

【課題】 従来のパルス発振のレーザー光による照射を半導体膜に行った場合、半導体表面にリッジと呼ばれる凹凸が形成され、トップゲート型TFTの場合には、素子特性がリッジにより大きく左右されていた。特に、電気的に並列に接続する複数の薄膜トランジスタ間でのバラツキが問題となっている。

【解決手段】 本発明は、複数の薄膜トランジスタからなる回路の作製において、連続発振レーザを用いて半導体膜にレーザ光を照射して溶融する領域の幅LP(微結晶領域を含まない)を大きくし、一つの領域に複数の薄膜トランジスタ(電気的に並列に連結された薄膜トランジスタ)の活性層を配置することを特徴の一つとする。

(もっと読む)

1 - 15 / 15

[ Back to top ]