Fターム[5F110GG36]の内容

薄膜トランジスタ (412,022) | チャネル半導体層 (67,982) | チャネル領域の不純物 (5,796) | 不純物の分布 (414)

Fターム[5F110GG36]の下位に属するFターム

一導電型不純物のみ (175)

Fターム[5F110GG36]に分類される特許

1 - 20 / 239

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、シリコンを含む絶縁膜と、絶縁膜上の酸化物半導体膜と、酸化物半導体膜上のシリコンを含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有する構造とし、少なくともゲート電極と重畳する酸化物半導体膜は、絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%より低い領域を有し、当該領域以外の酸化物半導体膜のシリコン濃度は、当該領域より小さくなる構造とする。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物を低減する。また、酸化物半導体膜の被形成面近傍の結晶性を向上させる。また、該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】シリコンを含む下地絶縁膜と、下地絶縁膜上に形成された酸化物半導体膜と、酸化物半導体膜上に形成されたゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも酸化物半導体膜と重畳する領域に設けられたゲート電極と、酸化物半導体膜に電気的に接続されたソース電極、及びドレイン電極と、を有し、酸化物半導体膜は、下地絶縁膜との界面から酸化物半導体膜に向けてシリコン濃度が1.0原子%以下の濃度で分布する領域を有し、少なくとも領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

半導体装置とその製造方法

【課題】 寄生ダイオードを介したリーク電流を抑えること。

【解決手段】 半導体装置1は、c面を表面とする窒化物半導体の半導体層13と、厚みが減少する厚み減少部14aを有する窒化物半導体のp型の埋込み層14と、を備える。埋込み層14では、厚み減少部14aの内部に酸素濃度がピークとなる部分が存在しており、そのピーク部分と厚み減少部14aの傾斜面の間のp型不純物の濃度が酸素濃度よりも高い部分が存在する。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制する。

【解決手段】半導体装置を、半導体層として機能する酸化物半導体膜と、酸化物半導体膜上のシリコン酸化物を含むゲート絶縁膜と、ゲート絶縁膜上の少なくとも酸化物半導体膜と重畳するゲート電極と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極を有し、少なくともゲート電極と重畳する酸化物半導体膜は、ゲート絶縁膜との界面から酸化物半導体膜に向けてシリコンの濃度が1.1原子%以下の濃度で分布する領域を有する構造とする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】比較的簡素な構成で電流コラプスの発生を抑制し、デバイス特性の劣化を抑えた信頼性の高い高耐圧のAlGaN/GaN・HEMTを実現する。

【解決手段】SiC基板1上に化合物半導体積層構造2を備えたAlGaN/GaN・HEMTにおいて、3層のキャップ層2eを用いることに加え、キャップ層2eのドレイン電極5の近傍(ゲート電極6とドレイン電極5との間で、ドレイン電極5の隣接箇所)に高濃度n型部位2eAを形成し、高濃度n型部位2eAでは、そのキャリア濃度が電子供給層2dのキャリア濃度よりも高く、そのエネルギー準位がフェルミエネルギーよりも低い。

(もっと読む)

半導体装置

【課題】酸化物半導体膜の被形成面近傍に含まれる不純物の濃度を低減する。また、酸化物半導体膜の結晶性を向上させる。該酸化物半導体膜を用いることにより、安定した電気特性を有する半導体装置を提供する。

【解決手段】ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくとも前記ゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜における、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域において、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さく、少なくとも第1の領域内に、結晶部を含む半導体装置である。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いた半導体装置において、オン電流の低下を抑制すること。

【解決手段】酸化物半導体膜を用いたトランジスタにおいて、ゲート電極と、ゲート電極を覆い、シリコンを含む酸化物を含むゲート絶縁膜と、ゲート絶縁膜と接し、少なくともゲート電極と重畳する領域に設けられた酸化物半導体膜と、酸化物半導体膜と電気的に接続するソース電極およびドレイン電極と、を有し、酸化物半導体膜において、ゲート絶縁膜との界面からの厚さが5nm以下の第1の領域は、シリコンの濃度が1.0原子%以下であり、酸化物半導体膜の第1の領域以外の領域に含まれるシリコンの濃度は、第1の領域に含まれるシリコンの濃度より小さくする。

(もっと読む)

不揮発性半導体記憶装置、及びその製造方法

【課題】チャネル移動度を向上させた不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】不揮発性半導体記憶装置は、半導体基板20上に設けられたメモリトランジスタ40と選択トランジスタ50を有する。メモリトランジスタ40は、導電層41a〜41d、メモリゲート絶縁層43、柱状半導体層44、及び酸化層45を有する。導電層41は、メモリトランジスタ40のゲートとして機能する。メモリゲート絶縁層43は、導電層の側面に接する。半導体層44は、導電層と共にメモリゲート絶縁層43を一方の側面で挟み、半導体基板20に対して垂直方向に延び、メモリトランジスタ40のボディとして機能する。酸化層45は、半導体層44の他方の側面に接する。半導体層44は、シリコンゲルマニウムにて構成される。酸化層45は、酸化シリコンにて構成される。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】不純物イオンの注入による悪影響を防止しつつ水平方向の耐圧を向上できる半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、素子を構成し、電流が流れる一対の不純物領域が、半導体基板の第1主面の表層に形成されたものであり、水平方向の耐圧を確保するため、フィールドプレート33を有している。これに加えて、この半導体装置は、半導体基板の表面から、素子の電流経路となる第1不純物領域37および第2不純物領域38よりも深い所定の深さおいて、少なくとも第1不純物領域および第2不純物領域の間の領域に半導体基板と同一成分の非晶質層24を有する。この非晶質層は、単結晶および多結晶よりも高抵抗の層であり、擬似的なフィールドプレートとして機能する。そして、この非晶質層は、不活性元素のイオン注入により形成される。

(もっと読む)

表示装置およびその製造方法

【課題】微結晶シリコンを用いたボトムゲート型の薄膜トランジスタのオン電流に対するオフ電流の割合を減少させること。

【解決手段】表示装置に含まれる薄膜トランジスタは、ゲート電極が設けられた導電層と、前記導電層の上に設けられたゲート絶縁層と、前記ゲート絶縁層の上面に接するとともに前記ゲート電極の上方に設けられ、微結晶シリコンを含む第1の半導体膜と、前記第1の半導体膜の上面に接する第2の半導体膜と、前記第2の半導体膜に電気的に接続される第1の電極と、前記第2の半導体膜に電気的に接続される第2の電極と、を含む。前記第1の半導体膜における水素濃度は、前記ゲート絶縁層との界面と前記第2の半導体膜との界面との中間で最小となり、前記第1の半導体膜と前記第2の半導体膜との境界における酸素濃度は、前記第1の半導体膜の中央および前記第2の半導体膜の中央のうち少なくとも一方の酸素濃度以下である。

(もっと読む)

半導体基材およびその製造方法

【課題】簡便な方法で、結晶化部分を有する半導体基材を得る。

【解決手段】ベース基材と;該ベース基材上に配置された、アモルファス半導体材料由来の結晶性半導体層とを少なくとも含む半導体基材。結晶性半導体層の表面近傍において、SIMSによりGeが検出可能である。

(もっと読む)

半導体装置

【課題】回路誤動作を防止できる半導体装置を提供する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。また、外部電源61に接続されるラインを電源供給ラインとガードリング端子固定ラインとを分岐し、電源供給ラインの電流が流れないガードリング端子固定ラインに抵抗63を備えることで、バイパスコンデンサ64をディスクリート部品としなくても良い回路構成とする。

(もっと読む)

半導体装置及びその製造方法

【課題】SOI基板に形成されるMOSトランジスタの特性を向上することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1上に埋込絶縁層2を介して形成される第1半導体層3と、前記第1半導体層3及び前記絶縁層2内に形成され、前記第1半導体層3に接する第2半導体層12と、前記第2半導体層12の上に形成されるゲート絶縁膜13と、前記ゲート絶縁膜13上に形成されるゲート電極14gと、前記ゲート電極14gの側壁に形成されるサイドウォール7とを有する。

(もっと読む)

半導体装置

【課題】高耐圧を確保でき、かつ大電流を流すことができるMOSトランジスタを備えた半導体装置を提供する。

【解決手段】P型拡散層15に起因してN型拡散層13に第1空乏層23が形成される。ゲート電極19にゲート電圧が印加されていない状態では、P型ポリシリコンからなるゲート電極19及びN型拡散層13の仕事関数差に起因してN型拡散層13に第2空乏層25が形成される。空乏層23,25によってソースコンタクト用拡散層9とドレインコンタクト用拡散層11が電気的に遮断される。ゲート電極19にゲート電圧が印加された状態では、第2空乏層25が消滅又は縮小することによってソースコンタクト用拡散層9とドレインコンタクト用拡散層11がN型拡散層13を介して電気的に導通する。

(もっと読む)

ライントンネリングトンネル電界効果トランジスタ(TFET)及びその製造方法

【課題】ソース領域、ドレイン領域、ソース領域とソース−チャネル界面およびドレイン領域とドレイン−チャネル界面を形成するチャネル領域、を有するトンネル電界効果トランジスタを提供する。

【解決手段】ソース領域は、第1ソースサブ領域20と、ソース−チャネル界面201に近接する第2ソースサブ領域25とを含み、第1ソースサブ領域と第2ソースサブ領域との間の界面が規定される。第2ピーク濃度は、第1ソースサブ領域と第2ソースサブ領域との界面に近接する位置での第1ドーピングプロファイルの最大レベルより充分高い。チャネル領域21及びドレイン領域22がゲート電極24によって覆われないように、ソース領域の一部を長手方向Lに覆うようにした電極24と、ゲート電極とソース領域との間の長手方向Lに沿ったゲート誘電体29と備える。

(もっと読む)

半導体装置

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

半導体装置、表示モジュール、及び電子機器

【課題】酸化亜鉛に代表される酸化物半導体膜を用いて薄膜トランジスタを形成すること

で、作製プロセスを複雑化することなく、尚かつコストを抑えることができる半導体装置

及びその作製方法を提供することを目的とする。

【解決手段】基板上にゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、

ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に第1の導電膜及び第2の

導電膜を形成する半導体装置であって、酸化物半導体膜は、チャネル形成領域において少

なくとも結晶化した領域を有する。

(もっと読む)

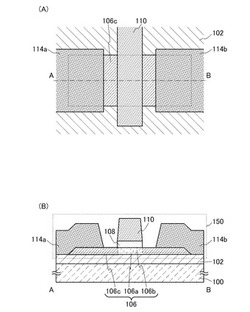

半導体装置およびその製造方法

【課題】第1のトランジスタと第2のトランジスタが、ぞれぞれのドレイン領域とソース領域を共有して同一の半導体基板上に形成される構成の半導体装置の製造において、それぞれのトランジスタのソース領域およびドレイン領域の直下に埋め込み絶縁膜を効率的に形成できる製造方法を提供する。

【解決手段】半導体基板上にそれぞれのトランジスタのソース領域およびドレイン領域に対応してトレンチを形成し、前記トレンチをSiGe混晶層と半導体層を順次形成することにより充填し、さらに第1のトランジスタのソース領域および第2のトランジスタのドレイン領域直下のSiGe混晶層を、素子分離溝を介して選択エッチングにより除去し、第1のトランジスタのドレイン領域および第2のトランジスタのソース領域として共有される拡散領域直下のSiGe混晶層を、前記拡散領域に形成した孔を介して選択エッチングし、除去する。

(もっと読む)

1 - 20 / 239

[ Back to top ]