Fターム[5F110HJ15]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | 拡散 (325)

Fターム[5F110HJ15]の下位に属するFターム

固相拡散 (107)

気相拡散(雰囲気中) (184)

Fターム[5F110HJ15]に分類される特許

1 - 20 / 34

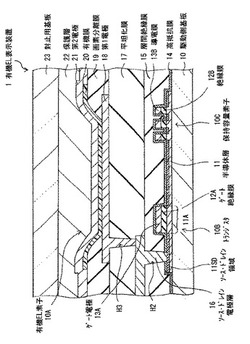

表示装置および電子機器

【課題】画質劣化を抑制することが可能な表示装置および電子機器を提供する。

【解決手段】有機EL表示装置1は、駆動側基板10上に、有機EL素子10Aと、トランジスタ10Bと、映像信号に対応する電荷を保持する保持容量素子10Cとを備えたものである。保持容量素子10Cは、酸化物半導体よりなる半導体層11上に絶縁膜12Bを介して導電膜13Bを有し、かつ半導体層11上の選択的な領域に、導電膜13Bおよび絶縁膜12Bのうちの少なくとも一部が除去されてなる凹部を有している。保持容量素子10Cでは、そのような凹部を通じて、半導体層11の酸化物半導体から酸素が離脱し易くなり、これにより、印加電圧に依存する容量変動が抑制される。

(もっと読む)

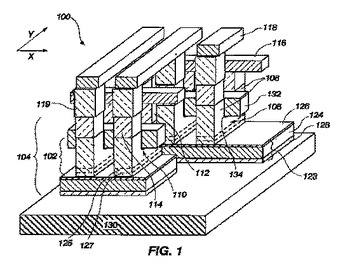

シリコン・オン・インシュレータ内に形成された金属酸化膜半導体デバイス

【課題】デバイスの破壊電圧を大きく低下させずにLDMOSデバイスのオン抵抗を減少可能にすること。

【解決手段】半導体デバイスが、第1導電型の基板、基板の少なくとも一部分上に形成された絶縁層、および絶縁層の少なくとも一部分上に形成された第2導電型のエピタキシャル層を備える。第1、第2導電型のソース/ドレイン領域が、エピタキシャル層内でその上面に近接して形成され、第1、第2ソース/ドレイン領域は互いに横に間隔を置いて設置される。ゲートは、エピタキシャル層の上でその上面に近接して、少なくとも部分的に第1および第2ソース/ドレイン領域の間に形成される。このデバイスはさらに、エピタキシャル層と、絶縁層を貫通して形成され、基板、第1ソース/ドレイン領域、およびエピタキシャル層と直接に電気的に接続するように構成された第1のソース/ドレイン接点と、エピタキシャル層を貫通して形成され、第2ソース/ドレイン領域に直接に電気的に接続できるように構成された第2ソース/ドレイン接点とを備える。

(もっと読む)

半導体装置

【課題】半導体基板上へのVFETと他の種類の素子との混載が可能でありながら、半導体基板上に積層される半導体層の表面に大きな段差を有しない半導体装置を提供する。

【解決手段】P型シリコン基板2上には、酸化シリコンからなるボックス層3、N+型横方向導電層4およびN−型表面層5が積層されている。ボックス層3上には、N−型表面層5の表面からボックス層3に至る深さを有する、平面視環状のディープトレンチ6が形成されている。ディープトレンチ6およびボックス層3に取り囲まれるトランジスタ形成領域8は、その周囲から分離されている。このトランジスタ形成領域8において、N−型表面層5の表層部には、ソース領域14およびドレイン領域16が形成されている。またディープトレンチ6の側面に沿って、ドレイン領域16とN+型横方向導電層4とに接続されたN+型縦方向導電層17が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタのスイッチング速度を高速化した半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、絶縁層の一部上に形成された半導体層10と、半導体層10の側面10aに形成され、第1のゲート絶縁膜21、第1のゲート電極22、並びにソース及びドレインとなる2つの第1の不純物層23,24を有する第1のトランジスタ20と、半導体層10の側面10bに形成され、第2のゲート絶縁膜31、第2のゲート電極32、並びにソース及びドレインとなる2つの第2の不純物層33,34を有する第2のトランジスタ30とを具備する。

(もっと読む)

結晶性酸化物半導体膜の作製方法

【課題】優れた結晶性を有する酸化物半導体膜を作製する。

【解決手段】酸化物半導体の膜を形成するに際し、基板を第1の温度以上第2の温度未満に加熱しつつ、基板の、典型的な長さが1nm乃至1μmの部分だけ、第2の温度以上の温度に加熱する。ここで、第1の温度とは、何らかの刺激があれば結晶化する温度であり、第2の温度とは、刺激がなくとも自発的に結晶化する温度である。また、典型的な長さとは、その部分の面積を円周率で除したものの平方根である。

(もっと読む)

浮遊ボディセル、浮遊ボディセルを含むデバイス、ならびに浮遊ボディセルの形成方法。

バックゲート上に配置される浮遊ボディセルのアレイと、バックゲートから間隔の開いた浮遊ボディセルのソース領域およびドレイン領域と、を含む浮遊ボディセル構造。浮遊ボディセルは、ピラーの間に伸長するチャネル領域を有する大量の半導電性材料を各々含み、ピラーは、U形状トレンチなどの間隙によって分離されうる。アレイの浮遊ボディセルは、別のゲートに電気的に結合され、別のゲートは、大量の半導電性材料の側壁上に配置されてもよいし、大量の半導電性材料の間隙内に配置されてもよい。浮遊ボディセルデバイスを形成する方法も開示される。  (もっと読む)

(もっと読む)

高耐圧半導体装置及びその製造方法

【課題】チャネルの閾値調整が容易で、オン抵抗の小さい高耐圧半導体装置及びその製造方法を提供する。

【解決手段】第1導電型であるp型の半導体基板100上に形成された第2導電型であるn型のソース領域200と、半導体基板100の表面から所定の深さまで形成された第2導電型であるn型の電界緩和層300と、電界緩和層300の領域内においてソース領域200から遠い領域の上層領域に形成されたドレイン領域400と、ドレイン領域400とソース領域200の間で半導体基板100の表面の活性領域に形成されたゲート酸化膜500と、ゲート酸化膜500の下のチャネル部550の一部に形成される閾値調整用拡散部555と、ドレイン領域400とゲート酸化膜500の間の半導体層表面に形成されたLOCOS酸化膜600と、ゲート酸化膜500上からLOCOS酸化膜600上に張り出して形成されたゲート電極510と、を有して構成する。

(もっと読む)

誘電体分離型半導体装置とその製造方法

【課題】耐圧が維持されるとともに絶縁耐量の高いワイヤ配線が電極に配線される誘電体分離型半導体装置を提供する。

【解決手段】誘電体分離型半導体装置は、支持基板、埋込誘電体層および半導体基板から構成される誘電体分離型基板を具備し、半導体基板は、選択的に形成される第1半導体領域と、第1半導体領域をその外周縁から所定の距離だけ離間して取り囲むように設けられる第2導電型の第2半導体領域と、第1半導体領域に接合される第1主電極と、第2半導体領域に接合される第2主電極と、を備え、支持基板は、第1半導体領域に重畳する領域を内包する位置に貫通孔と、貫通孔の開口に現れる埋込誘電体層の領域に接して配設されるシリコーンラダーポリマー層と、貫通孔の開口に現れる埋込誘電体層の領域、シリコーンラダーポリマー層に接して配設される裏面電極と、シリコーンラダーポリマー層に囲まれる空間を埋めて平坦化する第1ハンダと、を備える。

(もっと読む)

電界効果トランジスタ

【課題】高いしきい値電圧と大きい動作電流とを両立した電界効果トランジスタを提供すること。

【解決手段】基板と、前記基板上に形成され、窒化物系化合物半導体からなり、チャネル層を含む半導体層と、前記チャネル層上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に形成されたゲート電極と、前記半導体層上において前記ゲート電極を挟むように配置されたソース電極およびドレイン電極と、を備え、前記チャネル層の表面の、少なくとも前記ゲート電極直下の領域が、窒素極性の表面を含む。

(もっと読む)

高耐圧半導体装置および高電圧集積回路装置

【目的】ワイヤ接続における高耐圧半導体装置において、複雑なプロセス製造工程も、複雑な裏面加工工程も一切伴わず、低コストで高耐圧化、高信頼性化を実現できる高耐圧半導体装置およびそれを用いた高電圧集積回路装置を提供することにある。

【構成】半導体基板100上に誘電体層101を介して半導体層102が形成され、半導体層102上にドレイン層113と、ドレイン層113を内包するように形成されたバッファ層112と、ドレイン層113と離間し、その周りを囲むように形成されたソース層114と、ソース層114を内包するように形成されたウエル層111と、半導体層102上にゲート絶縁膜を介して形成されたゲート電極110と、を備えた高耐圧半導体装置において、ドレイン層113及び、バッファ層112の平面形状が非連続または連続の環状とする。

(もっと読む)

電界効果トランジスタ

【課題】耐圧性が高い電界効果トランジスタを提供すること。

【解決手段】p型の導電型を有する基板と、前記基板上に形成された高抵抗層と、前記高抵抗層上に形成され、p型の導電型を有するp型半導体層を前記基板側に配置したリサーフ構造を有する半導体動作層と、前記半導体動作層上に形成されたソース電極、ドレイン電極、およびゲート電極と、を備える。好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたn型の導電型を有するリサーフ層を備える。また、好ましくは、前記リサーフ構造は、前記p型半導体層上に形成されたアンドープのキャリア走行層と、前記キャリア走行層上に形成され該キャリア走行層とはバンドギャップエネルギーが異なるキャリア供給層とを備える。

(もっと読む)

NMOS及びPMOSトランジスタそれぞれのチャネルに同時に引っ張り及び圧縮歪みを与えるための方法

【課題】同一支持体上に第一歪みによる歪みが与えられた少なくとも一つの半導体領域と、第二歪みとは異なる第二歪みによる歪みが与えられた少なくとも一つの半導体領域とを備えたマイクロエレクトロニクス装置の製造方法を提供する。

【解決手段】プレ歪み層上の半導体領域の形成、その後の、プレ歪み層の厚さにわたって延伸するトレンチの形成が含まれ、トレンチのレイアウト及び寸法の関数としての半導体領域の寸法及びレイアウトは、プレ歪み層と同じ種類の歪みを有する半導体領域及びプレ歪み層のものとは異なる種類の歪みを有する半導体領域が得られるようにされる。

(もっと読む)

半導体構造のドープ方法およびその半導体デバイス

核種を歪み半導体層の中に導入する方法であって、露出した歪み半導体層を含む第1領域を備えた基板を用意し、該基板を反応チャンバの中に投入するステップと、少なくとも露出した歪み半導体層の上に、気相堆積(VPD)によって等方性の第1核種含有層を形成するステップと、続いて、第1熱処理を実施し、これにより第1核種含有層から第1核種の少なくとも一部を歪み半導体層の中に拡散し、歪み半導体層の中に拡散した第1核種の少なくとも一部を活性化するステップとを含む。  (もっと読む)

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法を提供する。また、層間絶縁膜、平坦化膜、ゲート絶縁膜等の絶縁膜、配線、電極、端子等の導電膜、半導体膜等の半導体素子の各部位の膜を形成する方法を提供する。また、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】ガリウムと亜鉛を含む液滴を吐出して、基板上に膜パターンを形成する。または、印刷法により、基板上にガリウムと亜鉛を含む材料を用いて膜パターンを形成する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】薄膜トランジスタのソース領域およびドレイン領域の低抵抗化、および短チャネル効果を抑制しS値を低減した半導体装置およびその作製方法を提供することを目的とする。

【解決手段】第1の半導体層102の上にゲート絶縁膜103を介して形成されたゲート電極104と、前記ゲート電極の側面に形成されたサイドウォール201と、該サイドウォールの端部202と、前記第1の半導体層102上に接して積層された第2の半導体層106と、を有し、前記第2の半導体層106は前記サイドウォールの端部202の少なくとも一部を覆って形成されている。

(もっと読む)

半導体装置

【課題】ドレイン・オン電流値のばらつきが小さなCNT-FETを有する半導体装置を提供することを目的とする。また、本発明は、ドレイン電流のスイッチング比のばらつきが小さなCNT-FETを有する半導体装置を提供することを目的とする。

【解決手段】複数本のカーボンナノチューブをチャネルに用いる電界効果型トランジスタを二つ以上用いている半導体装置において、前記電界効果型トランジスタのドレイン・オン電流値のばらつきがσ1(オン電流値の標準偏差を平均値で割ったもの)のとき、各電界効果型トランジスタチャネルのカーボンナノチューブの本数Nが、N>31×σ1-1なる式(1)の関係を満たすことを特徴とする半導体装置を採用する。

(もっと読む)

ZnO系トランジスタ

【課題】高性能、高品質のチャ領域を構成することができるZnO系トランジスタを提供する。

【解決手段】MgZZnO基板1上に、MgXZnO層2、MgYZnO層3が積層されている。MgXZnO層2とMgYZnO層3の界面で2次元電子ガスが発生する。4はゲート絶縁膜又は有機物電極であり、MgYZnO層3に接して形成されている。ゲート絶縁膜又は有機物電極4上にはゲート電極5が、ドナードープ部3a上には各々ソース電極6、ドレイン電極7が形成されている。このように、トランジスタのチャネル領域をMgZnO層で形成する。

(もっと読む)

ZnO系トランジスタ

【課題】基板上に積層された薄膜に影響を与えない絶縁性ZnO系基板を用いたZnO系トランジスタを提供する。

【解決手段】MgZZnO基板1上に、MgXZnO層2、MgYZnO層3が積層されている。MgXZnO層2とMgYZnO層3の界面で2次元電子ガスが発生する。4はゲート絶縁膜又は有機物電極であり、MgYZnO層3に接して形成されている。ゲート絶縁膜又は有機物電極4上にはゲート電極5が、ドナードープ部3a上には各々ソース電極6、ドレイン電極7が形成されている。MgZZnO基板1は、遷移金属を含み、かつ抵抗率が1×105Ωcm以上に絶縁化されている。

(もっと読む)

シリコンの結晶化方法、接合体、半導体装置の製造方法および半導体装置

【課題】比較的低温下で、結晶粒や成長方向の制御を確実に行うことができ、これにより半導体特性に優れたポリシリコン層を効率よく形成可能なシリコンの結晶化方法、熱処理を施すことにより良好な結晶化がなされる非晶質部を備える接合体、前記結晶化方法により形成された半導体部を備える半導体装置を製造する方法、および、この方法により製造された半導体装置を提供すること。

【解決手段】本発明のシリコンの結晶化方法は、a−Si膜30a(非晶質部)と、c−Siの種結晶30cとを用意する工程と、a−Si膜30aの表面と種結晶30cの表面に、それぞれエネルギーを付与する工程と、a−Si膜30aと種結晶30cとを接合し接合体305を得る工程と、接合体305を加熱することにより、a−Si膜30aを結晶化する工程とを有する。これにより、a−Si膜30aと種結晶30cとの接合界面が成長核となって結晶化が進行する。

(もっと読む)

III族窒化物半導体を用いた電界効果トランジスタ

【課題】絶縁膜と半導体層の界面準位を効果的に低減し,大電流を流すことのできるIII族窒化物半導体を用いた電界効果トランジスタを提供する。

【解決手段】GaN系MOSFETは、基板1と、基板1上に形成されたバッファ層2と、バッファ層2上に形成されたp型GaN層の半導体層3と、半導体層3のチャネル領域上にSiO2から成るゲート酸化膜5を介して形成されたゲート電極8と、ソース電極6及びドレイン電極7と、半導体層3のチャネル領域の両側に形成され、ソース電極6及びドレイン電極にそれぞれオーミック接触するコンタクト領域4s及び4dとを備える。ゲート酸化膜5であるSiO2をバッファードふっ酸(BHF約7%)でエッチングした場合のエッチングレートを、1 nm/sec以上3 nm/sec以下とした。

(もっと読む)

1 - 20 / 34

[ Back to top ]