Fターム[5F110HJ17]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | 不純物領域の製法 (6,364) | 不純物の導入方法 (4,201) | 拡散 (325) | 気相拡散(雰囲気中) (184)

Fターム[5F110HJ17]の下位に属するFターム

プラズマ雰囲気中 (150)

Fターム[5F110HJ17]に分類される特許

1 - 20 / 34

半導体装置およびその作製方法

【課題】酸化物半導体膜のソース領域およびドレイン領域の導電率を高めることで、高いオン特性を有する酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】第1の領域および第2の領域を有し、少なくともインジウム(In)を含む酸化物半導体膜と、少なくとも酸化物半導体膜の第1の領域と重畳して設けられたゲート電極と、酸化物半導体膜およびゲート電極の間に設けられたゲート絶縁膜と、少なくとも一部が酸化物半導体膜の第2の領域と接して設けられた電極と、を有し、酸化物半導体膜は、酸化物半導体膜と電極との界面近傍のInの濃度が高く、界面から15nmの範囲で遠ざかるに従いInの濃度が低くなる。なお、酸化物半導体膜の第1の領域はトランジスタのチャネル領域として機能し、第2の領域はトランジスタのソース領域、ドレイン領域として機能する。

(もっと読む)

半導体装置、半導体ウエハ、及びこれらの製造方法

【課題】トランジスタ特性のバラツキが低減された半導体装置を提供する。

【解決手段】SOI基板101は、P型半導体層102の上にN型半導体層104が形成された半導体基板12、その上に形成されたBOX層106、及びBOX層上に形成されたSOI層108を有する。第1素子分離絶縁層110bは、SOI基板101に埋め込まれ、下端16がP型半導体層102に達し、第1素子領域(NFET領域30)と第2素子領域(PFET領域40)とを分離する。P型トランジスタ130bは、第1素子領域40に位置し、チャネル領域120bを有し、N型トランジスタ130aは、NFET領域30に位置し、チャネル領域120aを有する。第1バックゲートコンタクト134bは、第1素子領域40に位置する第2導電型層層104に、第2バックゲートコンタクト134aは、第2素子領域30に位置する第2導電型層104に接続される。

(もっと読む)

半導体装置及びその製造方法

【課題】トレンチ分離されたSOI基板にIGBTとその制御回路等が形成される半導体装置において、IGBTの高耐圧化及びターンオフ特性の改善等が必要になる。

【解決手段】ダミー半導体基板16にN型エピタキシャル層8を形成し、N型エピタキシャル層8にトレンチ30を形成し、トレンチ30側壁及びN型エピタキシャル層8表面にN型バッファ層7、次にP型埋め込みコレクタ層6を形成し、トレンチ30底面及びP+型埋め込みコレクタ層6上を埋め込み絶縁膜5で被覆する。埋め込み絶縁膜5上をポリシリコン膜3で被覆し、該ポリシリコン膜3と絶縁膜2を介してP型半導体基板1を貼り合わせた後、ダミー半導体基板16を除去し、略同一平面状に露出するトレンチ30底面の埋め込み絶縁膜5、P+型埋め込みコレクタ層6、N型バッファ層7、N型ドリフト層8a等を具備するSOI基板を形成する。該SOI基板にIGBT等を形成する。

(もっと読む)

MEMS及びMEMSの製造方法

【課題】回路構成の設計自由度の高いMEMS及びMEMSの製造方法を提供する。

【解決手段】基板10と、基板10の一方の面側に設けられる第1半導体部21と、基板10の一方の面側に設けられる振動子31と、を備えるMEMSにおいて、第1半導体部21の側面側に設けられ、かつ基板表面に対して略垂直な第1面21aと、振動子31の側面側に設けられ、かつ基板表面に平行な方向において第1面21aと対向する第2面31aが設けられると共に、第2面31a側の表層部分は第1面21a側をゲート電極として電圧が印加された際にチャネルとなることで、第1半導体部21における第1面21aを含む部分と振動子31における第2面31aを含む部分とで電界効果トランジスタが構成されることを特徴とする。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】チャネル領域に強い歪みを印加することによりデバイス特性を改善した半導体装置を提供すること。

【解決手段】半導体基板1と、半導体基板1の第1の面に形成されたゲート絶縁膜2と、ゲート絶縁膜2の上に形成されたゲート電極3と、ゲート電極3の側壁に形成されたゲート側壁絶縁膜4と、ゲート電極3の下の半導体基板1中に形成されるチャネル領域に隣接し、不純物が注入されたソース/ドレイン拡散層領域5、6と、ゲート電極3の上方を除き、ソース/ドレイン拡散層領域5、6の上に形成された応力印加膜8と、を有し、半導体基板1の第1の面におけるソース/ドレイン拡散層領域5、6が形成された領域には、凹部または凸部50、51、60、61が設けられている半導体装置を提供する。

(もっと読む)

半導体装置の製造方法及び半導体製造装置

【課題】 極浅拡散層を形成することが可能な半導体装置の製造方法及び半導体製造装置

を提供することを目的とする。

【解決手段】

半導体基板100表面をアモルファス化することにより半導体基板100表面にアモル

ファス層111を形成するアモルファス層形成工程と、ドーパントを含むガス雰囲気中で

半導体基板100にマイクロ波を照射することにより、アモルファス層111にドーパン

トを拡散させるとともにドーパントの活性化を行い、半導体基板100に拡散層112を

形成する拡散層形成工程と、を具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

光マトリックスデバイスの製造方法

【課題】

薄膜トランジスタのソース・ドレイン間のON抵抗を低下することができる光マトリックスデバイスの製造方法を提供する。

【解決手段】

凹凸パターンが形成された転写型に真空中にて半導体膜6を形成し、半導体膜6が形成された転写型に真空中にて連続してゲート絶縁膜7を形成する。そして、基板1上に予め形成されたゲート線2上に接着用樹脂4を介して前記ゲート絶縁膜7および前記半導体膜6を転写する。そして、基板1上に転写された前記半導体膜6に水素イオンをドープする処理を行う。それにより、半導体膜6の抵抗率を低下させることができるので、薄膜トランジスタのゲートがON状態のときのソース・ドレイン間の接続抵抗を低下させることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】半導体膜に混入する不純物濃度を制御した活性層を有する半導体回路を備えた半

導体装置を提供するものである。

【解決手段】上記目的を解決するため、ガラス基板上に200nm〜500nmの膜厚の

第1の窒化珪素膜と、前記第1の窒化珪素膜上に第2の窒化珪素膜と、前記第2の窒化珪

素膜上にチャネル形成領域となる領域を含む非晶質半導体膜と、を有する構成において、

前記第1の絶縁膜と前記第2の絶縁膜との界面において、ボロンを有する。

(もっと読む)

基板全域にわたって高められた均一性を有する埋め込みSi/Ge材質を伴うトランジスタ

【解決手段】

洗練された半導体デバイスにおいては、異なる結晶方位に対して異方性エッチング挙動を有し得るウエット化学的エッチングプロセスに基いてキャビティを形成することによって、チャネル領域の近くに歪誘起半導体合金を位置させることができる。1つの実施形態では、異方性エッチング挙動に加えて二酸化シリコンに関する高いエッチング選択性を呈するTMAHを用いることができ、それにより、チャネル領域からのオフセットを更に減少させる可能性を追加的に提供する一方で、全体的なプロセスばらつきの大きな原因となることのない極めて薄いエッチング停止層が可能になる。

(もっと読む)

有機メソメリー化合物の使用、有機半導体物質、及び、電子素子

【課題】有機半導体マトリックス物質をドーピングしてその電気特性を変化させるために、有機ドーパントとして有機メソメリー化合物を使用する。

【解決手段】ドーパントが供給される有機半導体を、製造プロセス時により簡単に取り扱うことができるように、また、ドープされた有機半導体を有する電子素子を、再生可能に製造できるように、メソメリー化合物として、同じ蒸着条件下ではテトラフルオロテトラシアノキノンジメタン(F4TCNQ)よりも揮発性の低いキノン、または、キノン誘導体、または、1,2,3−ジオクサボリン、または1,3,2−ジオクサボリン誘導体を使用することを提案する。

(もっと読む)

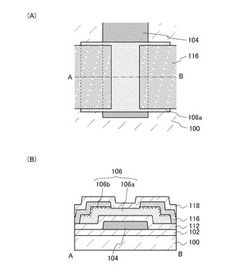

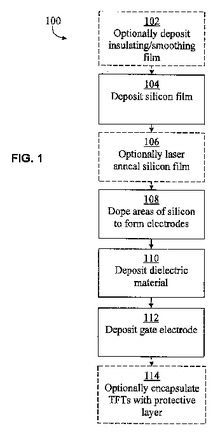

シリコン薄膜トランジスタ、並びにその製造システム及び方法

可撓性基板上に、自己整合シリコン薄膜トランジスタを製造するシステム及び方法。前記システム及び方法は、高いパフォーマンスのトランジスタを製造するために、精密さ、レゾリューション、レジストレーションが達成されるよう、レーザアニール、エッチング技術、レーザドーピングを全て低温度で行いつつ、化学気相堆積、プラズマエンハンスト気相堆積、プリント、コーティング、及び他の堆積処理といった堆積処理を組み込むとともに組み合わせている。そのようなTFTはディスプレイ、パッケージング、ラベリング等に使用できる。  (もっと読む)

(もっと読む)

横型MOS半導体装置

【課題】ボイドのでき易い深いトレンチもしくは経済性の悪い幅広トレンチを形成せずに、高耐圧に必要なオフセットドレイン領域の幅を確保しつつ占有面積を小さくすることができる横型MOS半導体装置を提供すること。

【解決手段】半導体基板の一方側の表面層に、それぞれ一導電型の、ソース領域13とドレイン領域12と、該ドレイン領域12より低不純物濃度で互いに接するオフセットドレイン領域5とを備え、前記ソース領域13表面と前記オフセットドレイン領域5表面に挟まれる他導電型のチャネル領域4表面にゲート絶縁膜を介して設けられるゲート電極6を有する横型MOS半導体装置において、前記オフセットドレイン領域5に、相互に並列で蛇行状の平面パターンであって表面から垂直に形成されるトレンチ列8を備え、該トレンチ列8に電流阻害材料7が充填されている横型MOS半導体装置とする。

(もっと読む)

半導体素子

【課題】インバータ回路など、電気接続された2つの半導体スイッチによるスイッチング動作を行なうための電気回路において、寄生インダクタンスおよびオン抵抗を抑制することができる構造の半導体素子を提供すること。

【解決手段】この半導体素子は、基板1と、基板1の一方側に形成される半導体積層構造部2とを備える。半導体積層構造部2は、n型層5、このn型層5の一方側(下面側)に積層されたp型層4、およびこのp型層4に積層されたn型層3からなる縦型npn構造の第1半導体積層構造8と、n型層5をこの第1半導体積層構造8と共有し、n型層5、このn型層5の他方側(上面側)に積層されたp型層6、およびこのp型層6に積層されたn型層7からなる縦型npn構造の第2半導体積層構造9とを備える。

(もっと読む)

窒化物半導体素子および窒化物半導体素子の製造方法

【課題】表面リーク電流を低減することができる、III族窒化物半導体を用いた窒化物半導体素子およびその製造方法を提供すること。

【解決手段】この電界効果トランジスタは、n型GaN層3、p型GaN層4およびn型GaN層5が、順に積層された窒化物半導体積層構造部2を備えている。ゲート絶縁膜9が形成されている。このゲート絶縁膜9は、窒化物半導体積層構造部2の表面全域に接して形成された窒化シリコン膜20と、この窒化シリコン膜20の上に形成された酸化シリコン10膜とを備えている。ゲート絶縁膜9の上には、ゲート絶縁膜9を挟んで領域12に対向するようにゲート電極11が形成されている。また、窒化物半導体積層構造部2の引き出し部6の表面には、ドレイン電極7が接触形成されている。一方、窒化物半導体積層構造部2のn型GaN層5の頂面には、ソース電極13が接触形成されている。

(もっと読む)

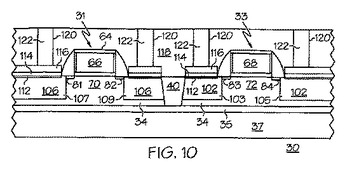

歪みが強化された半導体デバイスとその製造方法

歪みが強化された半導体デバイス30とその製造方法が提供される。1つの方法において、デバイスチャネル70、72に歪みを誘発するために、デバイスのソース領域103、107とドレイン領域105、109とに歪み誘発半導体材料102、106が埋め込まれる。誘発された歪みを緩和しないように、ソースおよびドレイン領域に対して薄い金属シリサイドコンタクト112が形成される。導電性材料114、116の層が薄い金属シリサイドコンタクトに接触して選択的に蒸着され、金属化されたコンタクト122が導電性材料に対して形成される。  (もっと読む)

(もっと読む)

GaN系半導体素子

【課題】表面準位が形成されている素子であっても、表面準位を安定化させて、表面リークを抑制し、高周波動作の応答性も向上させたGaN系半導体素子を提供する。

【解決手段】サファイア基板1上にGaNバッファ層2、アンドープGaN層3、n型GaNドレイン層4、p型GaNチャネル層5が積層されており、p型GaNチャネル層5の上には、n型GaNソース層6が形成されている。リッジ部A側面の傾斜面にゲート絶縁膜7が形成され、ゲート絶縁膜7上に積層されている。ドレイン電極10とソース電極9が形成された半導体表面及びゲート絶縁膜7で被覆されている半導体表面とを除く露出した半導体表面に、その露出した半導体表面がすべて覆われるように絶縁膜11が形成される。

(もっと読む)

シリコンと炭素を含有するインサイチュリンドープエピタキシャル層の形成

【課題】 リンでドープされたシリコンと炭素を含有するエピタキシャル層を形成する方法を提供する。

【解決手段】 圧力は、堆積中100トール以上に維持される。方法は、置換型炭素を含む膜の形成を生じさせる。特定の実施形態は、半導体デバイス、例えば、金属酸化物半導体電界効果トランジスタ(MOSFET)デバイスにおけるエピタキシャル層の形成と処理に関する。

(もっと読む)

電子素子及びその製造方法

【課題】 ナノチューブを用いた新規の電子素子を提供する。

【解決手段】 N型半導体の特性を有するソース電極6及びドレイン電極7が両端に設けられた、P型半導体の特性を有するカーボンナノチューブ1と、カーボンナノチューブ1を挟んで対向するように設けられるバイアス電極2及び制御電極3と、を備える電子素子である。バイアス電極2と制御電極3とに異なる電圧を印加することで、ソース電極6とドレイン電極7との間にチャネルが形成されるようになっている。

(もっと読む)

半導体素子製造方法

【課題】良好な膜質を有するゲート絶縁膜を化合物半導体層上に形成することができる半導体素子製造方法を提供すること。

【解決手段】本発明は、基板1上にバッファ層2を介して積層されたGaN活性層3とゲート電極8との間にゲート絶縁膜であるSiO2膜5が形成された半導体素子を製造する半導体素子製造方法において、ゲート絶縁膜は、ECRスパッタリング法を用いて形成されることを特徴とする。この結果、良好な膜質を有するゲート絶縁膜をGaN活性層3上に形成することができる半導体素子製造方法を提供することが可能になる。

(もっと読む)

1 - 20 / 34

[ Back to top ]