Fターム[5F110HJ30]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−不純物領域 (11,069) | その他 (157)

Fターム[5F110HJ30]に分類される特許

1 - 20 / 157

半導体装置の作製方法

【課題】半導体装置の製造コストを低減することを課題の一とする。半導体装置の開口率

を向上することを課題の一とする。半導体装置の表示部を高精細化することを課題の一と

する。高速駆動が可能な半導体装置を提供することを課題の一とする。

【解決手段】同一基板上に駆動回路部と表示部とを有し、当該駆動回路部は、ソース電極

及びドレイン電極が金属によって構成され、且つチャネル層が酸化物半導体によって構成

された駆動回路用TFTと、金属によって構成された駆動回路用配線とを有すればよい。

また、当該表示部はソース電極及びドレイン電極が酸化物導電体によって構成され、且つ

半導体層が酸化物半導体によって構成された画素用TFTと、酸化物導電体によって構成

された表示部用配線とを有すればよい。

(もっと読む)

表示装置

【課題】酸化物半導体を用いた薄膜トランジスタを具備する画素において、開口率の向上

を図ることのできる発光表示装置を提供することを課題の一とする。

【解決手段】薄膜トランジスタ、及び発光素子を有する複数の画素を有し、画素は、走査

線として機能する第1の配線に電気的に接続されており、薄膜トランジスタは、第1の配

線上にゲート絶縁膜を介して設けられた酸化物半導体層を有し、酸化物半導体層は、第1

の配線が設けられた領域をはみ出て設けられており、発光素子と、酸化物半導体層とが重

畳して設けられる。

(もっと読む)

熱処理方法

【課題】シリコンゲルマニウム層の弛緩を抑制しつつ、高誘電率膜の結晶化を促進することができる熱処理方法を提供する。

【解決手段】ゲルマニウム濃度が相対的に低濃度のシリコンゲルマニウムの両側を高濃度のシリコンゲルマニウムにて挟み込んだシリコンゲルマニウム層を半導体ウェハー上に形成する。その低濃度のシリコンゲルマニウムの上に二酸化ケイ素の膜を挟んで高誘電率膜を形成する。この半導体ウェハーにフラッシュランプから第1照射を行ってその表面温度を予備加熱温度T1から目標温度T2にまで3ミリ秒以上1秒以下にて昇温する。続いて、フラッシュランプから第2照射を行って半導体ウェハーの表面温度を目標温度T2から±25℃以内の範囲内に3ミリ秒以上1秒以下維持する。これにより、シリコンゲルマニウム層の歪みの緩和を抑制しつつ、高誘電率膜の結晶化を促進することができる。

(もっと読む)

表示装置

【課題】電気泳動表示装置で、書き込み回数のさらに少ないアクティブマトリクス型の電

気泳動表示装置を提供することを課題とする。

【解決手段】複数の画素電極上に、複数の帯電粒子を内蔵したマイクロカプセルを配置し

、前記画素電極の電位により前記帯電粒子を制御することによって明暗を表示することを

特徴とした表示装置において、前記画素電極への映像信号の再書き込み動作を、画素に表

示する映像が変化する場合に行うことにより、書き込み回数を低減する。

(もっと読む)

表示装置および表示装置の製造方法

【課題】酸化物半導体の特性の変化を防ぎつつ、耐圧特性も向上させた薄膜トランジスタを用いた表示装置を提供すること。

【解決手段】表示装置は、薄膜トランジスタを含む。薄膜トランジスタは、ゲート電極と、ゲート電極を覆い絶縁物質を含むゲート絶縁層と、前記ゲート絶縁層の上面に接する酸化物半導体膜と、前記酸化物半導体膜の上面にあり互いに離間する第1の領域と第2の領域にそれぞれ接するソース電極およびドレイン電極と、前記第1の領域と前記第2の領域の間の第3の領域に接し、前記絶縁物質を含むチャネル保護膜と、を含む。平面的にみて前記ゲート電極に重なる前記酸化物半導体膜の上面の領域は第3の領域に含まれかつ小さく、前記酸化物半導体膜のうち前記ゲート電極に重なる部分の一部を除く部分は、前記ゲート電極に重なる部分の前記一部より抵抗が低い。

(もっと読む)

表示装置

【課題】消費電力が抑制された表示装置を提供する。

【解決手段】第1のトランジスタ、第2のトランジスタ、及び一対の電極を有する発光素

子を含む画素が複数設けられた画素部を有し、前記第1のトランジスタは、ゲートが走査

線に電気的に接続され、ソースまたはドレインの一方が信号線に電気的に接続され、ソー

スまたはドレインの他方が前記第2のトランジスタのゲートに電気的に接続され、前記第

2のトランジスタは、ソースまたはドレインの一方が電源線に電気的に接続され、ソース

またはドレインの他方が前記一対の電極の一方に電気的に接続され、前記第1のトランジ

スタは、水素濃度が5×1019/cm3以下である酸化物半導体層を有する。そして、

前記表示装置が静止画像を表示する期間の間に、前記画素部に含まれる全ての走査線に供

給される信号の出力が停止される期間を有する。

(もっと読む)

電子デバイスの製造方法

【課題】転写歩留まりを向上することが可能な電子デバイスの製造方法を提供することを目的とする。

【解決手段】薄膜トランジスタ(TFT)19の製造方法において、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aにガスバリア層7が形成されている。そのため、ガスバリア層7側からスタンプ5を空気で加圧する際に、スタンプ5の半導体膜8および絶縁膜9が形成される側の面とは反対側の面5aから、半導体膜8および絶縁膜9が形成される面に、加圧した空気が抜けにくくなる。これにより、スタンプ5を基板1に押し付けることを持続することができるので、スタンプ5に形成された半導体膜8および絶縁膜9と基板1との密着性を増すことができる。したがって、基板1に転写されない半導体膜8および絶縁膜9が減少し、薄膜転写の歩留まりを向上させることができる。

(もっと読む)

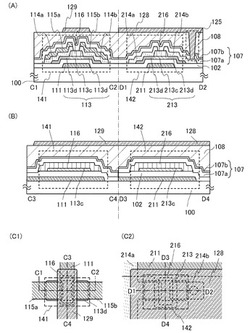

半導体装置

【課題】同一基板上に複数種の回路を形成し、複数種の回路の特性にそれぞれ合わせた複

数種の薄膜トランジスタを備えたアクティブマトリクス型液晶表示装置を提供することを

課題の一とする。

【解決手段】画素用薄膜トランジスタとしてソース電極層及びドレイン電極層上に重なる

酸化物半導体層を有する逆コプラナ型を用い、駆動回路用薄膜トランジスタとして、チャ

ネル保護型を用い、かつ、画素用薄膜トランジスタの主要な部分を透光性材料で構成する

ことにより、開口率を上げる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】トランジスタの微細化を達成し、電界緩和がなされた、酸化物半導体を用いた半導体装置を提供することを課題の一とする。

【解決手段】ゲート電極の線幅を微細化し、ソース電極層とドレイン電極層の間隔を短縮する。ゲート電極をマスクとして自己整合的に希ガスを添加し、チャネル形成領域に接する低抵抗領域を酸化物半導体層に設けることができるため、ゲート電極の幅、即ちゲート配線の線幅を小さく加工しても位置精度よく低抵抗領域を設けることができ、トランジスタの微細化を実現できる。

(もっと読む)

半導体装置

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】本発明は、低温かつ簡便で安価な製造工程により作製可能であり、トランジスタ特性に優れる、ダブルゲート構造を有する薄膜トランジスタおよびその製造方法を提供することを主目的とする。

【解決手段】本発明は、基板と、上記基板上に形成された第1ゲート電極と、上記第1ゲート電極を覆うように形成された第1ゲート絶縁層と、上記第1ゲート絶縁層上に形成され、低抵抗領域であるソースコンタクト領域およびドレインコンタクト領域ならびに高抵抗領域であるチャネル領域を有する酸化物半導体層と、上記ソースコンタクト領域に接して形成されたソース電極と、上記ドレインコンタクト領域に接して形成されたドレイン電極と、上記酸化物半導体層上に形成され、絶縁性有機材料を含む第2ゲート絶縁層と、上記第2ゲート絶縁層上に形成された第2ゲート電極とを有することを特徴とする薄膜トランジスタを提供する。

(もっと読む)

信号処理回路及びその駆動方法

【課題】複雑な作製工程を必要とせず、消費電力を抑えることができる信号処理回路の提供する。

【解決手段】入力された信号の位相を反転させて出力する論理素子を2つ(第1の位相反転素子及び第2の位相反転素子)と、第1の選択トランジスタと、第2の選択トランジスタと、を有する記憶素子であって、酸化物半導体層にチャネルが形成されるトランジスタと容量素子との組を2つ(第1のトランジスタと第1の容量素子との組、及び第2のトランジスタと第2の容量素子との組)有する。そして、信号処理回路が有する記憶装置に上記記憶素子を用いる。例えば、信号処理回路が有するレジスタ、キャッシュメモリ等の記憶装置に上記記憶素子を用いる。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供する。

【解決手段】ワイドギャップ半導体、例えば酸化物半導体を含むメモリセルを用いて構成された半導体装置であって、メモリセルからの読み出しのために基準電位より低い電位を出力する機能を有する電位切り替え回路を備えた半導体装置とする。ワイドギャップ半導体を用いることで、メモリセルを構成するトランジスタのオフ電流を十分に小さくすることができ、長期間にわたって情報を保持することが可能な半導体装置を提供することができる。

(もっと読む)

半導体装置及び半導体記憶装置

【課題】記憶回路におけるデータの保持期間を長くする。また、消費電力を低減する。また、回路面積を小さくする。また、1回のデータの書き込みに対する該データの読み出し可能回数を増やす。

【解決手段】記憶回路を具備し、記憶回路は、ソース及びドレインの一方にデータ信号が入力される第1の電界効果トランジスタと、ゲートが第1の電界効果トランジスタのソース及びドレインの他方に電気的に接続される第2の電界効果トランジスタと、ソース及びドレインの一方が第2の電界効果トランジスタのソース又はドレインに電気的に接続される第3の電界効果トランジスタと、を備える。

(もっと読む)

電界効果型トランジスタ、その製造方法及びスパッタリングターゲット

【課題】トランジスタ特性(移動度、オフ電流、閾値電圧)及び信頼性(閾値電圧シフト、耐湿性)が良好で、ディスプレイパネルに適した電界効果型トランジスタを提供すること。

【解決手段】基板上に、少なくともゲート電極と、ゲート絶縁膜と、半導体層と、半導体層の保護層と、ソース電極と、ドレイン電極とを有し、ソース電極とドレイン電極が、半導体層を介して接続してあり、ゲート電極と半導体層の間にゲート絶縁膜があり、半導体層の少なくとも一面側に保護層を有し、半導体層が、In原子、Sn原子及びZn原子を含む酸化物であり、かつ、Zn/(In+Sn+Zn)で表される原子組成比率が25原子%以上75原子%以下であり、Sn/(In+Sn+Zn)で表される原子組成比率が50原子%未満であることを特徴とする電界効果型トランジスタ。

(もっと読む)

コプレナ型の酸化物半導体素子とその製造方法

【課題】折り曲げ耐性が向上したコプレナ型の酸化物半導体を提供し、また、コンタクトホールを精巧に形成するコプレナ型の酸化物半導体の製造方法を提供する。

【解決手段】絶縁性を有する基板と、前記基板上に配置され、チャネル領域及び電極接続領域を有する酸化物半導体層と、前記酸化物半導体層上に配置され、コンタクトホールを有するゲート絶縁層と、前記ゲート絶縁層上に配置されたソース電極、ドレイン電極、及びゲート電極と、を有するコプレナ型の酸化物半導体素子であって、前記ゲート絶縁層は、架橋ポリマーで形成されていることを特徴とするコプレナ型の酸化物半導体素子とその製造方法。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

1 - 20 / 157

[ Back to top ]