Fターム[5F110HK12]の内容

薄膜トランジスタ (412,022) | ソース、ドレイン−低抵抗層 (42,553) | 材料 (26,322) | 半導体 (4,961) | 半導体の結晶構造 (2,050)

Fターム[5F110HK12]の下位に属するFターム

Fターム[5F110HK12]に分類される特許

1 - 5 / 5

トランジスタ及び当該トランジスタの作製方法

【課題】酸化物半導体層をチャネル層として適用するトランジスタにおいて、特性のばらつきを低減すると共に、酸化物半導体層とソース電極層及びドレイン電極層とのコンタクト抵抗を低減することを課題とする。

【解決手段】チャネル層を酸化物半導体で設けるトランジスタにおいて、酸化物半導体層の領域のうち、ソース電極層とドレイン電極層の間に位置しチャネルが形成される領域を少なくとも非晶質構造で設け、ソース電極層及びドレイン電極層等の外部と電気的に接続する領域を結晶構造で設ける。

(もっと読む)

半導体装置の作製方法

【課題】露光マスク数を削減することでフォトリソグラフィ工程を簡略化し、酸化物半導体を有する半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネルエッチ構造の逆スタガ型薄膜トランジスタを有する半導体装置の作製方法において、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたマスク層を用いて酸化物半導体膜及び導電膜のエッチング工程を行う。エッチング工程は、エッチング液によるウエットエッチングを用いる。

(もっと読む)

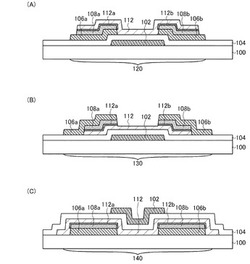

半導体装置及び半導体装置の作製方法

【課題】金属材料からなるソース電極及びドレイン電極と、酸化物半導体膜とが直接接する薄膜トランジスタ構造とすると、コンタクト抵抗が高くなる恐れがある。コンタクト抵抗が高くなる原因は、ソース電極及びドレイン電極と、酸化物半導体膜との接触面でショットキー接合が形成されることが要因の一つである。

【解決手段】酸化物半導体膜とソース電極及びドレイン電極の間に1nm以上10nm以下のサイズの結晶粒を有し、チャネル形成領域となる酸化物半導体膜よりキャリア濃度が高い酸素欠乏酸化物半導体層を設ける。

(もっと読む)

酸化物半導体薄膜トランジスタ

【課題】 ボトムゲート型TFTにおいて、ゲート電極に電圧を印加するとゲート電極の上方にある半導体層にチャネルが形成される。しかし、ソース・ドレイン電極直下の半導体層の大部分にはチャネルが形成されず、寄生抵抗となるため、電流駆動能力が低下するという課題がある。

【解決手段】 基板上に、ゲート電極と、ゲート絶縁層と、アモルファス酸化物からなる半導体層と、ソース・ドレイン電極と、保護層と、を有するトランジスタであって、

前記半導体層は、

前記ソース・ドレイン電極が形成された領域に対応する第1の領域と、

前記ソース・ドレイン電極が形成された領域に対応しない第2の領域と、を含み、

少なくとも前記第1の領域が前記第2の領域のアモルファス酸化物とは組成の異なる結晶成分を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

1 - 5 / 5

[ Back to top ]